Fターム[5F005AH02]の内容

Fターム[5F005AH02]に分類される特許

1 - 20 / 102

半導体装置

【課題】静電気放電が印加されたときの熱破壊を抑制すること。

【解決手段】半導体装置1の半導体活性層16には、n型領域23とp型領域26とn型の埋込み領域30が形成されている。n型領域23は、カソード電極Kに電気的に接続している。p型領域26は、アノード電極Aに電気的に接続している。埋込み領域30は、半導体活性層16のうちのp型領域26の裏面側の少なくも一部を含むように形成されており、p型領域26の裏面に接触しているとともに、不純物濃度が半導体活性層16の不純物濃度よりも濃い。

(もっと読む)

窒化ガリウム結晶、ホモエピタキシャル窒化ガリウムを基材とするデバイス、及びその製造方法

【課題】ホモエピタキシャルLED、LD、光検出器又は電子デバイスを形成するために役立つGaN基板の形成方法の提供。

【解決手段】約104/cm2未満の転位密度を有し、傾角粒界が実質的に存在せず、酸素不純物レベルが1019cm−3未満の窒化ガリウムからなる単結晶基板上に配設された1以上のエピタキシャル半導体層を含むデバイス。かかる電子デバイスは、発光ダイオード(LED)及びレーザーダイオード(LD)用途のような照明用途、並びにGaNを基材とするトランジスター、整流器、サイリスター及びカスコードスイッチなどのデバイスの形態を有し得る。また、約104/cm2未満の転位密度を有し、傾角粒界が実質的に存在せず、酸素不純物レベルが1019cm−3未満の窒化ガリウムからなる単結晶基板を形成し、該基板上に1以上の半導体層をホモエピタキシャルに形成する方法及び電子デバイス。

(もっと読む)

半導体装置

【課題】光により消弧可能な光スイッチング素子又はその光スイッチング素子を備える半導体装置を提供する。

【解決手段】本発明の半導体装置(100)は、窒化物半導体を含む素子構造を有する光スイッチング素子(10)と、前記光スイッチング素子に第1の波長の光を照射する第1の光源(20)と、を遮光部材(40)内に備え、前記光スイッチング素子(10)は、前記第1の波長の光を照射されることにより、該光を照射される前に比べて、立ち上がり電圧が上昇することを特徴とする。

(もっと読む)

圧接型大電力用サイリスタモジュールおよびその製造方法ならびにその使用方法

【課題】水冷設備を準備できない使用環境でサイリスタチップを冷却する。

【解決手段】サイリスタチップ113,123を具備する圧接型大電力用サイリスタモジュール100において、複数の放熱フィン1bを有するヒートシンク1のベース部分1aに対して絶縁板11とコモンバー12とアノードサブスペーサ181とサイリスタチップ113とカソードサブスペーサ183とカソードスペーサ14とカソード端子バー18とを圧接手段19によって上下方向に圧接し、ヒートシンク1のベース部分1aに対して絶縁板21とコモンバー12とカソードスペーサ24とカソードサブスペーサ193とサイリスタチップ123とアノードサブスペーサ191とアノード端子バー22とを圧接手段29によって上下方向に圧接した。

(もっと読む)

サイリスタ

【課題】ゲート電極の接触抵抗の値を制御できるサイリスタを提供することを目的としている。

【解決手段】第1導電型半導体基板14の一方の表面近傍に第1の第2導電型半導体領域16が形成され、第1の第2導電型半導体領域の表面近傍にカソード電極20と接合する第1導電型半導体領域17およびゲート電極21と接合する第2の第2導電型半導体領域18が形成され、第1導電型半導体基板の他方の表面近傍にアノード電極22と接合する第3の第2導電型半導体基板13が形成されたサイリスタにおいて、ゲート電極と第2の第2導電型半導体領域とが接合してオーミック接触を形成し、ゲート電極と第1の第2導電型半導体領域とが接合して非オーミック接触を形成する。

(もっと読む)

バイポーラ半導体素子およびその製造方法

【課題】SiC基板をp型とした結晶品質の良いSiCバイポーラ素子を提供する。

【解決手段】このダイオード素子1によれば、p型のSiCアノード層12,p型のSiCドリフト層13とn+型SiCカソード層14をn型SiC基板21上にエピタキシャル成長により形成してから、n型SiC基板21を除去した。つまり、p型基板に見立てるp+型4H-SiCアノード層12は、エピタキシャル成長により作製するから、バルク成長で作製されるp型基板に比べて結晶成長速度が遅く、p型ドーパントであるアルミニウムの濃度を上げても、結晶品質が良くなる。したがって、この結晶品質が良いp+型4H-SiCアノード層12を基板に見立てることができ、SiC基板をp型とした結晶品質の良いSiCダイオード素子を実現できる。

(もっと読む)

半導体装置

【課題】トライアックが形成された半導体装置の性能を向上させる。

【解決手段】トライアック形成用の半導体領域が形成された半導体基板1の表面に電極T1,G1が形成され、裏面に裏面電極が形成されている。電極T1から裏面電極へ電流を流す場合と、裏面電極から電極T1へ電流を流す場合の両方の動作モードにおいて、ゲート端子である電極G1に電極T1よりも高電位の電圧を印加することで、半導体基板1に形成されたサイリスタをターンオンする。半導体基板1の表面側には、p型半導体領域P2とそれに内包されるn型半導体領域N2とが形成され、電極T1はp型半導体領域P2とn型半導体領域N2に接し、電極G1はp型半導体領域P2のみに接する。そして、平面視において、電極G1が接する部分のp型半導体領域P2と電極T1が接する部分のp型半導体領域P2の間に、n型半導体領域N2が延在している。

(もっと読む)

半導体集積回路のESD保護回路およびそのESD保護素子

【課題】従来構造に比べて、レイアウト面積の増加を抑え、保護能力の大幅な低下を招くことなく、保持電圧Vhを電源電圧以上の適正な電圧に制御する。

【解決手段】ESD保護素子21は、スナップバック特性を有するスナップバック特性素子としてのSCR素子と、このSCR素子に接続されて、スナップバック開始電圧Vt1を素子電圧分だけ加算すると共に保持電圧Vhを該素子電圧の2倍高くするための電圧加算素子としてのダイオード13とを有して、ダイオード13の素子電圧を調整して、保持電圧Vhを電源電圧Vcc以上で被保護素子の耐電圧以下に調整する。

(もっと読む)

バイポーラ半導体素子

【課題】表面欠陥を低減でき、オン電圧ドリフトを抑制できるバイポーラ半導体素子を提供する。

【解決手段】このSiC GTOによれば、メサ状のp型アノードエミッタ層5の長側面5Bが延在している方向を、〈11−20〉方向としたオフ方向から角度φ=60°だけ傾斜させた方向とした。これにより、長側面5Bは、{01−10}面となり、{11−20}面である短側面5Cに比べて、表面欠陥が入りにくくなる。また、長側面5Bの延在方向を、上記オフ方向から角度φ=60°だけ傾斜させたことで、長側面5Bの延在方向とオフ方向とが一致している場合(φ=0°)に比べて、メサ状のp型アノードエミッタ層5の長側面5Bに現れる{0001}面の層の数を減らすことができて、{0001}面の層内に入る表面欠陥を減少できる。

(もっと読む)

半導体装置

【課題】ホールド電圧を変化させずに、トリガー電圧のみを調節することができるようにする。

【解決手段】本実施形態における保護素子10は、低濃度コレクタ層102、シンカー層110、高濃度コレクタ層112、エミッタ層130、高濃度ベース層122、ベース層120、第1導電型層140、及び第2導電型層150を有している。第2導電型層150は低濃度コレクタ層102に形成されており、ベース層120と第1導電型層140の間に位置している。第2導電型層150は低濃度コレクタ層102よりも不純物濃度が高い。

(もっと読む)

半導体装置

【課題】保持電流特性に影響を与えずに、点弧動作感度の高感度化を実現するサイリスタ(半導体装置)を提供する。

【解決手段】サイリスタ100は、p領域1とn領域2とp領域3とn領域4とが順に接合されるサイリスタを有する。また、サイリスタ100は、n領域2とp領域3とに接して形成され、n領域2とp領域3との接合耐圧より接合耐圧が低い低耐圧領域10を有する。低耐圧領域10は、該領域において接合面にかかる電界方向の該領域幅が、サイリスタ100のブレークダウン電圧によって該領域に生成される空乏層幅より広く、サイリスタ100のブレークオーバ電圧によって接合面がブレークダウンする範囲において狭く形成される。

(もっと読む)

発光チップ、発光装置、プリントヘッドおよび画像形成装置

【課題】複数の発光点を並行して点灯させうる発光チップ等を提供する。

【解決手段】発光チップC1(C)は、基板80上に列状に配列された発光サイリスタL1、L2、L3、…から構成される発光サイリスタ列、転送サイリスタT1、T2、T3、…から構成される転送サイリスタ列、許可ダイオードDe1、De2、De3、…から構成される許可ダイオード列、ダイオードスイッチDs1、Ds2、Ds3、…から構成されるダイオードスイッチ列を備える。さらに、第1許可信号φE1に対して、反転した第2許可信号φE2を設定する許可信号設定部170、および転送サイリスタ列を駆動する第1転送信号φ1または第2転送信号φ2に応じて、第1点灯信号φI1または第2点灯信号φの電位を設定する点灯信号設定部160を備える。

(もっと読む)

半導体装置

【課題】保護素子としてサイリスタを用いる場合に、サイリスタのトリガ電圧をホールド電圧から独立して変更することができるようにする。

【解決手段】第1の第1導電型拡散層120、第1の第2導電型拡散層130、第2の第1導電型拡散層150、及び第2の第2導電型拡散層140はこの順に並んでいる。そして第2の第2導電型拡散層140及び第1導電型層100が互いに接する領域におけるこれらの不純物濃度は、第2の第2導電型拡散層140の底面に位置する部分よりも、第2の第2導電型拡散層140の側面に位置する部分のほうが高い。

(もっと読む)

バイポーラ半導体素子

【課題】ドリフト層とドリフト層に隣接する層との界面の応力を低減して、順方向電圧を低く抑えることができるバイポーラ半導体素子を提供する。

【解決手段】このpinダイオード20は、n型SiCドリフト層23の膜厚の各範囲(300μm以下200μm超),(200μm以下100μm超),(100μm以下50μm超)に対応して、n型SiCバッファ層22の不純物濃度の各上限値(5×1017cm−3),(7×1017cm−3),(10×1017cm−3)が設定されている。これにより、n型SiCドリフト層23とn型SiCバッファ層22との界面の応力を低減でき、順方向電圧を低減できる。

(もっと読む)

半導体装置

【課題】占有面積を増大させずに、電源投入開始後のチップ動作時にESD保護素子で発生するリーク電流を低減することができるESD保護素子を提供する。

【解決手段】電源ライン及び接地ラインを含む電子回路が形成された半導体基板10と、半導体基板10において電源ライン(Vdd)及び接地ライン(Vss)間に設けられ、サイリスタSCR及びサイリスタを駆動するトリガーダイオードTDを含む静電気放電保護素子とを有し、トリガーダイオードは、半導体基板10に形成されたアノード拡散層22と、アノード拡散層22から離間して半導体基板10に形成されたカソード拡散層21と、アノード拡散層22及びカソード拡散層21間において半導体基板10上にゲート絶縁膜16を介して形成されたゲート電極17とを有し、外部電源に接続された外部端子(パッド電極27)がゲート電極17に電気的に接続されている構成とする。

(もっと読む)

バイポーラ半導体素子

【課題】制御電極による制御能力を向上できるバイポーラ半導体素子を提供する。

【解決手段】このゲートターンオフサイリスタは、隣り合う2列R1,R2のメサ型のアノードエミッタ層5の間で列方向に延在している列間の第1のコンタクトホール20Bに形成された第1のゲート端子15だけでなく、各列R1,R2の端側で各列R1,R2に沿って列方向に延在している端側の第2,第3のコンタクトホール20C,20Dに形成された第2,第3のゲート端子16,17を有する。これにより、列間の第1のゲート端子15と端側の第2,第3のゲート端子16,17とでターンオフ時の転流を分担できて、転流の不揃いを抑制できる。

(もっと読む)

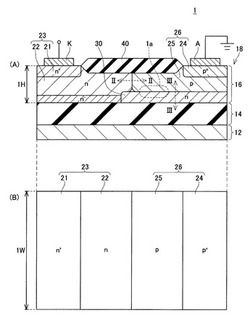

逆阻止型サイリスタ

【課題】本発明は、高い周波数のスイッチング動作に対応でき、且つ、電力損失を低減できる逆阻止型サイリスタを提供することを目的とする。

【解決手段】P領域(1a、1b)とN領域(2a、2b)とP領域3とN領域4とが順に接合された逆阻止型サイリスタ100は、P領域(1a、1b)からN領域4に順方向電圧が印加された場合にP領域(1a、1b)とN領域4の間を導通させる前の最大電圧値を示すブレークオーバ電圧が、N領域4からP領域(1a、1b)に逆方向電圧が印加された場合にN領域4とP領域(1a、1b)の間の導通を阻止する限界の電圧値を示すブレークダウン電圧より低くなるように電圧差を生じさせる電圧差生成領域30を有する。

(もっと読む)

駆動装置、プリントヘッド及び画像形成装置

【課題】発光サイリスタを駆動するための駆動回路の発振を防止する。

【解決手段】オン/オフ指令信号DRVON−PがHレベルの場合、PMOS43及びNMOS44からなるCMOSインバータ42の出力側のデータ端子DAがLレベルとなる。この結果、プリントヘッド13側の共通端子INも0Vとなり、各発光サイリスタ210のアノード・カソード間に電源電圧VDDが印加される。この際、発光サイリスタ210−1〜210−nの内、発光指令されている発光サイリスタ210のゲートのみを、シフトレジスタ110によって選択的にHレベルとすることで、発光指令されているサイリスタ210がターンオンする。NMOS44のチャネル形成予定領域に、サブストレート領域と同極性の不純物が注入されているので、NMOS44の閾値電圧が増加し、駆動回路41の発振を防止できる。

(もっと読む)

半導体装置及びその製造方法

【課題】3次元的に形成したトランジスタやサイリスタのリーク電流を低減する半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板10の主面に対してほぼ垂直に形成されたシリコンピラー12と、シリコンピラー12の下部及び上部にそれぞれ設けられた第1及び第2の不純物拡散層14,16と、シリコンピラー12を水平方向に貫いて設けられたゲート電極18と、ゲート電極18とシリコンピラー12との間に設けられたゲート絶縁膜20と、シリコンピラー12に隣接して設けられたバックゲート電極48と、バックゲート電極48とシリコンピラー12との間に設けられたバックゲート絶縁膜46とを備える。

(もっと読む)

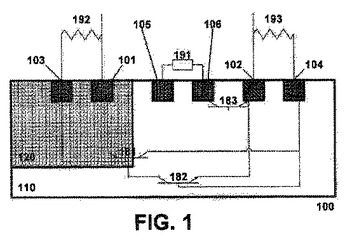

高保持電圧デバイス

高保持電圧(HVO静電放電(ESD)保護回路が、シリコン制御整流器(SCE)デバイスと、SCRデバイスの保持電圧を高める、SCRデバイスのアノードとカソードとの間の長さ(LAC)内に設置された補償領域とを備える。補償領域は、負のフィードバック機構をSCRデバイスに導入することで、SCRのループゲインに影響を及ぼし、高保持電圧で回生フィードバックに達しうる。  (もっと読む)

(もっと読む)

1 - 20 / 102

[ Back to top ]