Fターム[5F005AH03]の内容

Fターム[5F005AH03]に分類される特許

1 - 20 / 31

窒化ガリウム結晶、ホモエピタキシャル窒化ガリウムを基材とするデバイス、及びその製造方法

【課題】ホモエピタキシャルLED、LD、光検出器又は電子デバイスを形成するために役立つGaN基板の形成方法の提供。

【解決手段】約104/cm2未満の転位密度を有し、傾角粒界が実質的に存在せず、酸素不純物レベルが1019cm−3未満の窒化ガリウムからなる単結晶基板上に配設された1以上のエピタキシャル半導体層を含むデバイス。かかる電子デバイスは、発光ダイオード(LED)及びレーザーダイオード(LD)用途のような照明用途、並びにGaNを基材とするトランジスター、整流器、サイリスター及びカスコードスイッチなどのデバイスの形態を有し得る。また、約104/cm2未満の転位密度を有し、傾角粒界が実質的に存在せず、酸素不純物レベルが1019cm−3未満の窒化ガリウムからなる単結晶基板を形成し、該基板上に1以上の半導体層をホモエピタキシャルに形成する方法及び電子デバイス。

(もっと読む)

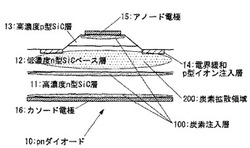

SiCバイポーラ型半導体素子

【課題】キャリア捕獲中心の少ないSiC半導体素子を提供する。

【解決手段】n型またはp型のSiC基板11と、n型またはp型の少なくとも1つのSiCエピタキシャル層12、あるいはn型またはp型の少なくとも1つのイオン注入層14と、を有し、pn接合界面付近および伝導度変調層(ベース層)内を除いた、SiC基板表面付近、SiC基板とSiCエピタキシャル層との界面付近、およびSiCエピタキシャル層の表面付近のうち少なくとも1つの領域100に、炭素注入層、珪素注入層、水素注入層、またはヘリウム注入層を有し、かつ、炭素原子、珪素原子、水素原子、またはヘリウム原子をイオン注入することで導入した格子間炭素原子をアニーリングにより伝導度変調層内へ拡散させるとともに格子間炭素原子と点欠陥とを結合させることで、電気的に活性な点欠陥が低減された領域を伝導度変調層内に有するSiCバイポーラ型半導体素子。

(もっと読む)

半導体装置

【課題】光により消弧可能な光スイッチング素子又はその光スイッチング素子を備える半導体装置を提供する。

【解決手段】本発明の半導体装置(100)は、窒化物半導体を含む素子構造を有する光スイッチング素子(10)と、前記光スイッチング素子に第1の波長の光を照射する第1の光源(20)と、を遮光部材(40)内に備え、前記光スイッチング素子(10)は、前記第1の波長の光を照射されることにより、該光を照射される前に比べて、立ち上がり電圧が上昇することを特徴とする。

(もっと読む)

半導体装置

【課題】精度良く形成されたフィンを有しつつ、十分な特性を有するESD保護素子を形成することができる半導体装置を提供する。

【解決手段】実施形態にかかる半導体装置は、制御整流素子を有し、このシリコン制御整流素子は、半導体基板と、第1のウェル領域と、第2のウェル領域と、複数のフィン領域とを有する。第1のウェル領域は半導体基板の最外周に位置する。さらに、ウェルコンタクト領域よりも外周に位置し、第1の導電型の不純物拡散層領域を有し、且つ、電気的に浮遊状態にある最外周フィン領域を有する。

(もっと読む)

バイポーラ半導体素子およびその製造方法

【課題】SiC基板をp型とした結晶品質の良いSiCバイポーラ素子を提供する。

【解決手段】このダイオード素子1によれば、p型のSiCアノード層12,p型のSiCドリフト層13とn+型SiCカソード層14をn型SiC基板21上にエピタキシャル成長により形成してから、n型SiC基板21を除去した。つまり、p型基板に見立てるp+型4H-SiCアノード層12は、エピタキシャル成長により作製するから、バルク成長で作製されるp型基板に比べて結晶成長速度が遅く、p型ドーパントであるアルミニウムの濃度を上げても、結晶品質が良くなる。したがって、この結晶品質が良いp+型4H-SiCアノード層12を基板に見立てることができ、SiC基板をp型とした結晶品質の良いSiCダイオード素子を実現できる。

(もっと読む)

逆阻止型サイリスタ

【課題】本発明は、高い周波数のスイッチング動作に対応でき、且つ、電力損失を低減できる逆阻止型サイリスタを提供することを目的とする。

【解決手段】P領域(1a、1b)とN領域(2a、2b)とP領域3とN領域4とが順に接合された逆阻止型サイリスタ100は、P領域(1a、1b)からN領域4に順方向電圧が印加された場合にP領域(1a、1b)とN領域4の間を導通させる前の最大電圧値を示すブレークオーバ電圧が、N領域4からP領域(1a、1b)に逆方向電圧が印加された場合にN領域4とP領域(1a、1b)の間の導通を阻止する限界の電圧値を示すブレークダウン電圧より低くなるように電圧差を生じさせる電圧差生成領域30を有する。

(もっと読む)

短絡型サイリスタ

【課題】本発明は、保持電流特性に影響を与えずに、オン状態に移行するブレークオーバ電圧の低電圧化を実現する短絡型サイリスタを提供することを目的とする。

【解決手段】第1領域(P領域1)と第2領域(N領域2)と第3領域(P領域3)と第4領域(N領域4)とが順に接合され、第1領域(P領域1)と第2領域(N領域2)を短絡させる電極11を有する短絡型サイリスタ100は、第3領域(P領域3)に接して形成され、第3領域(P領域3)より不純物濃度が高い第5領域(P++領域31)と、第2領域(N領域2)及び第5領域(P++領域31)に接して形成され、第2領域(N領域2)より不純物濃度が高い第6領域(N++領域41)とを有し、第5領域(P++領域31)の不純物濃度と第6領域(N++領域41)の不純物濃度とによってブレークオーバ電圧値が設定される。

(もっと読む)

パワー半導体デバイス

4層npnp構造、カソード面11およびアノード面12があり、ゲート電極4を介してターンオフできるパワー半導体デバイス1。カソード電極2とアノード電極3との間に以下の順で複数の層が配置される。−外側縁によって囲まれ、中央領域がある第1導電型カソード層5、カソード層5はカソード電極2と直接の電気的コンタクトにある,−第2導電型ベース層6,−カソード層5よりも低いドーピング濃度を有する第1導電型ドリフト層7、アノード電極3と電気的コンタクトにある第2導電型アノード層8。ゲート電極4は、カソード面11上にカソード電極2の横に配置され、ベース層6と電気的コンタクトにある。ベース層6は、カソード層5の中央領域に接触している、連続的な層としての、第1の深さに最大ドーピング濃度がある少なくとも1つの第1の層61を具備する。第1の層61よりも高いドーピング濃度を有し、第1の層61とカソード層5との間に配置され、第1の層61のほうを向いているカソード層5の外側縁をカバーする第2導電型抵抗減少層10,10’,10’’、この中でカソード層5の外側縁とベース層6との間の接合での抵抗が低減される。 (もっと読む)

半導体複合装置、この製造方法、光プリントヘッド及び画像形成装置

【課題】製造工程を簡略化して低コスト化を図る。

【解決手段】半導体複合装置は、シフトレジスタと、これにより時分割駆動される半導体薄膜からなる発光サイリスタアレイとにより構成されている。この製造方法は、例えば、シフトレジスタを構成する複数の回路構成素子243が形成されたシリコン基板241を用意する。シフトレジスタにより駆動される複数の発光サイリスタ261〜264が配列された結晶構造を持った半導体薄膜からなる発光サイリスタアレイを、パッシベーション膜242を介してシリコン基板241上に貼着する。フォトリソグラフィ法により、複数の回路構成素子243間を電気的に接続してシフトレジスタを形成すると共に、そのシフトレジスタ及び複数の発光サイリスタ261〜264間を電気的に接続するメタル配線265〜267を形成する。

(もっと読む)

点滅回路

【課題】消費電力を少なくするとともに、部品点数を少なくすることで低コスト化を図った点滅回路を提供することを目的とする。

【解決手段】発光サイリスタ20の第1端子であるアノード端子は、抵抗13を介して電源VDDに接続するとともにコンデンサ15を介してグランドに接続し、第2端子であるカソード端子は抵抗14を介してグランドに接続し、第3端子であるゲート端子は抵抗11と抵抗12の直列回路の接続中心に接続する。

(もっと読む)

半導体装置及びその製造方法

【課題】製造コストを抑えつつ、ガードリングに接するPN接合部の耐圧の向上を図る。

【解決手段】半導体基板10の表面にN−型半導体層11を形成し、その上層にP型半導体層12を形成する。P型半導体層12上には、絶縁膜13を形成する。その後、絶縁膜13からN−型半導体層11の厚さ方向の途中に至る複数の溝、即ち第1の溝17A、第2の溝17B、第3の溝17Cを形成する。これらの複数の溝は、そのうち互いに隣接する2つの溝において、電子デバイスに近い側、即ちアノード電極14に近い側の溝は、該溝よりも外側の他方の溝よりも浅く形成される。その後、第1の溝17A内、第2の溝17B内、第3の溝17C内に、絶縁材料18が充填される。その後、半導体基板10及びその上層に積層された各層からなる積層体をダイシングラインDLに沿ってダイシングする。

(もっと読む)

保護回路

【課題】静電気印加時には、高速にトリガし、通常使用時には、ラッチアップが起きにくいサイリスタ型の保護回路を提供する。

【解決手段】第1の端子と第2の端子との間に、一端が第2の端子に接続された容量素子と、半導体基板上に設けられたサイリスタであって、上記第1の端子に接続されたアノードと、上記第2の端子に接続された第1カソードと、アノードと第1カソードとの間に配置され上記容量素子の他端に接続された第2カソードと、を備えたマルチカソードサイリスタと、を用いることにより、アノードと第2カソード間で開始したサイリスタ動作がアノードと第1カソード間のサイリスタ動作を誘起するようにした。

(もっと読む)

半導体装置の製造方法

【課題】リーク電流の発生なくp型領域やn型領域を半導体基板上に結晶成長させてなるサイリスタ構成の素子を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板1の表面側にp型領域、n型領域、p型領域、およびn型領域がこの順に接して設けられた素子を備え、少なくとも1つの領域が半導体基板1の表面に結晶成長させた結晶成長層からなる半導体装置の製造方法において、第1n領域25および第2p領域27を結晶成長層として形成する際には、半導体基板1上に第1絶縁膜17と第2絶縁膜19との積層膜を成膜する第1工程と、第2絶縁膜19のエッチングに続けて第1絶縁膜17をウェットエッチングすることによって半導体基板1に達する開口を形成する第2工程と、開口底部に露出する半導体基板1の表面に、第1n領域25および第2p領域27を選択的に結晶成長させる第3工程とを行う。

(もっと読む)

半導体装置およびその製造方法

【課題】サイリスタの第2n型領域n2表面に金属シリサイド層を形成しても、第2n型領域n2と第2p型領域p2間でショートを起こさないようにすることを可能とする。

【解決手段】第1p型領域p1(第1領域)と、第1n型領域n1(第2領域)と、第2p型領域p2(第3領域)と、第2n型領域n2(第4領域)とが順に接合されたサイリスタT1が形成された半導体装置1であって、第2p型領域p2は、素子分離領域13で分離された半導体基板11に形成され、第2p型領域p2上にゲート絶縁膜21を介して形成されたゲート電極22と、ゲート電極22の両側の側壁に形成されたサイドウォール23、24を有し、2n型領域n2は、その一方側が第2p型領域p2の他方側と素子分離領域13(13−1)との接合部上を被覆し、その他方側がサイドウォール23の他方側に接合していることを特徴とする。

(もっと読む)

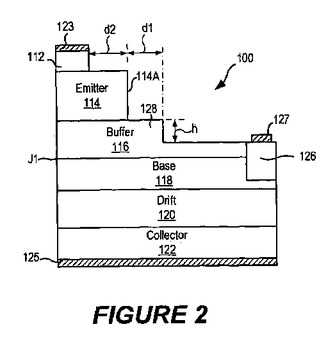

メサ構造とメサ段差を含むバッファ層とを備えた電力半導体デバイス

バイポーラ接合トランジスタが、第1の導電型を有するコレクタと、このコレクタ上の、第1の導電型を有するドリフト層と、このドリフト層上の、第1の導電型と反対の第2の導電型を有するベース層と、このベース層上の、低濃度でドープされ第1の導電型を有しベース層とp−n接合部を形成するバッファ層と、このバッファ層上の第1の導電型を有し側壁を有するエミッタメサとを含む。バッファ層は、エミッタメサの側壁の近傍でそこから横方向に間隔を置いて配置されたメサ段差を含み、エミッタメサの下のバッファ層の第1の厚さは、メサ段差外側のバッファ層の第2の厚さよりも厚い。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】エピタキシャル成長層上に形成したシリサイド層やエピタキシャル成長層と半導体基板とがショートを起こすのを防止することを可能にする。

【解決手段】半導体基板11に形成された素子分離領域14によって分離された該半導体基板11の素子形成領域12と、前記半導体基板11上に形成された絶縁膜41と、前記素子形成領域12の選択エピタキシャル成長させる領域上を含むように前記絶縁膜41に形成された開口部42と、前記開口部42内の半導体基板11の素子形成領域12より選択エピタキシャル成長により形成された半導体層15とを有することを特徴とする。

(もっと読む)

サイリスタ

【課題】高いゲート・カソード間耐圧を有するサイリスタを提供する。

【解決手段】第1導電型の半導体基板の第1主面には、第1導電型の不純物領域であるカソード領域と、前記カソード領域を取り囲むような第2導電型の不純物領域であるアノード領域と、前記カソード領域と前記アノード領域との間にはメサ溝部とを有し、前記半導体基板の第2主面には、第2導電型の不純物領域部であるゲート領域と、前記第1主面から前記ゲート領域まで達する深さの前記メサ溝部と、前記第1主面の前記カソード領域にはカソード金属電極、前記アノード領域にはアノード金属電極を有し、前記第2主面の前記ゲート領域上にはゲート金属電極を有することを特徴とするサイリスタであり、ゲート・カソード間距離が充分に確保できる構造であるため、ゲート・カソード間耐圧を高く確保することができる。

(もっと読む)

炭化珪素バイポーラ型半導体装置

【課題】メサ構造をもつ炭化珪素バイポーラ型半導体装置において、素子の表面付近に存在する欠陥核を起点とした積層欠陥の発生およびその面積拡大を抑制し、これにより順方向電圧の増加を抑制する。

【解決手段】第1導電型炭化珪素単結晶基板、第1導電型炭化珪素ドリフト層、第2導電型炭化珪素電荷注入層および該炭化珪素電荷注入層よりもドーピング密度が高い第2導電型の高ドーピング層が、この順序にて積層してなり、前記炭化珪素ドリフト層から前記高ドーピング層側の素子表面に至るメサ構造を有し、前記高ドーピング層の厚さが15nm〜1.5μmであり、かつ、前記高ドーピング層における最大ドーピング密度が1×1020cm-3〜2×1021cm-3であることを特徴とする炭化珪素バイポーラ型半導体装置。

(もっと読む)

垂直型電流制御型シリコン・オン・インシュレータ(SOI)デバイス及びそれを形成する方法

【課題】 CMOS集積回路(IC)のための静電放電(ESD)保護デバイスとして用いるのに適した電流制御シリコン・オン・インシュレータ(SOI)デバイスを提供すること。

【解決手段】 垂直型シリコン制御整流器(SCR)、垂直型バイポーラ・トランジスタ、垂直型キャパシタ、抵抗器及び/又は垂直型ピンチ抵抗器のようなデバイスを有するシリコン・オン・インシュレータ(SOI)集積回路(IC)チップ、及びそれらのデバイスを作製する方法である。デバイスは、SOI表面層及び絶縁体層を通って基板に達するシード孔内に形成される。例えばN−型埋め込み拡散部が、基板内のシード孔を通って形成される。ドープされたエピタキシャル層が、埋め込み拡散部上に形成され、このドープされたエピタキシャル層は、例えばP−型層及びN−型層などの多数のドープ層を含むことができる。ドープされたエピタキシャル層上に、例えばP−型のポリシリコンを形成することができる。コンタクト・ライナ内に、埋め込み拡散部へのコンタクトが形成される。

(もっと読む)

半導体装置の製造方法

【課題】サイリスタ構成の半導体装置において、アノード側の第1p型領域p1とn型の第1n型領域n1との界面を、急峻な濃度プロファイルに形成することを可能とする。

【解決手段】第1伝導型の第1領域(第1p型領域p1)と、前記第1伝導型とは逆伝導の第2伝導型の第2領域(第1n型領域n1)と、第1伝導型の第3領域(第2p型領域p2)と、第2伝導型の第4領域(第2n型領域n2)とが順に接合されたサイリスタを有する半導体装置1の製造方法において、前記第1n型領域n1をn型の不純物をドーピングしながらエピタキシャル成長により形成する工程と、前記第1n型領域n1の表層を除去する表面処理を行う工程と、前記表面処理をした第1n型領域n1上に、前記第1p型領域p1をp型の不純物をドーピングしながらエピタキシャル成長により形成する工程とを備えたことを特徴とする。

(もっと読む)

1 - 20 / 31

[ Back to top ]