Fターム[5F005BA01]の内容

Fターム[5F005BA01]の下位に属するFターム

凹溝 (26)

Fターム[5F005BA01]に分類される特許

1 - 20 / 66

窒化ガリウム結晶、ホモエピタキシャル窒化ガリウムを基材とするデバイス、及びその製造方法

【課題】ホモエピタキシャルLED、LD、光検出器又は電子デバイスを形成するために役立つGaN基板の形成方法の提供。

【解決手段】約104/cm2未満の転位密度を有し、傾角粒界が実質的に存在せず、酸素不純物レベルが1019cm−3未満の窒化ガリウムからなる単結晶基板上に配設された1以上のエピタキシャル半導体層を含むデバイス。かかる電子デバイスは、発光ダイオード(LED)及びレーザーダイオード(LD)用途のような照明用途、並びにGaNを基材とするトランジスター、整流器、サイリスター及びカスコードスイッチなどのデバイスの形態を有し得る。また、約104/cm2未満の転位密度を有し、傾角粒界が実質的に存在せず、酸素不純物レベルが1019cm−3未満の窒化ガリウムからなる単結晶基板を形成し、該基板上に1以上の半導体層をホモエピタキシャルに形成する方法及び電子デバイス。

(もっと読む)

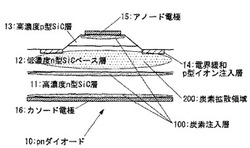

SiCバイポーラ型半導体素子

【課題】キャリア捕獲中心の少ないSiC半導体素子を提供する。

【解決手段】n型またはp型のSiC基板11と、n型またはp型の少なくとも1つのSiCエピタキシャル層12、あるいはn型またはp型の少なくとも1つのイオン注入層14と、を有し、pn接合界面付近および伝導度変調層(ベース層)内を除いた、SiC基板表面付近、SiC基板とSiCエピタキシャル層との界面付近、およびSiCエピタキシャル層の表面付近のうち少なくとも1つの領域100に、炭素注入層、珪素注入層、水素注入層、またはヘリウム注入層を有し、かつ、炭素原子、珪素原子、水素原子、またはヘリウム原子をイオン注入することで導入した格子間炭素原子をアニーリングにより伝導度変調層内へ拡散させるとともに格子間炭素原子と点欠陥とを結合させることで、電気的に活性な点欠陥が低減された領域を伝導度変調層内に有するSiCバイポーラ型半導体素子。

(もっと読む)

半導体装置

【課題】光により消弧可能な光スイッチング素子又はその光スイッチング素子を備える半導体装置を提供する。

【解決手段】本発明の半導体装置(100)は、窒化物半導体を含む素子構造を有する光スイッチング素子(10)と、前記光スイッチング素子に第1の波長の光を照射する第1の光源(20)と、を遮光部材(40)内に備え、前記光スイッチング素子(10)は、前記第1の波長の光を照射されることにより、該光を照射される前に比べて、立ち上がり電圧が上昇することを特徴とする。

(もっと読む)

圧接型大電力用サイリスタモジュールおよびその製造方法ならびにその使用方法

【課題】水冷設備を準備できない使用環境でサイリスタチップを冷却する。

【解決手段】サイリスタチップ113,123を具備する圧接型大電力用サイリスタモジュール100において、複数の放熱フィン1bを有するヒートシンク1のベース部分1aに対して絶縁板11とコモンバー12とアノードサブスペーサ181とサイリスタチップ113とカソードサブスペーサ183とカソードスペーサ14とカソード端子バー18とを圧接手段19によって上下方向に圧接し、ヒートシンク1のベース部分1aに対して絶縁板21とコモンバー12とカソードスペーサ24とカソードサブスペーサ193とサイリスタチップ123とアノードサブスペーサ191とアノード端子バー22とを圧接手段29によって上下方向に圧接した。

(もっと読む)

バイポーラ半導体素子およびその製造方法

【課題】SiC基板をp型とした結晶品質の良いSiCバイポーラ素子を提供する。

【解決手段】このダイオード素子1によれば、p型のSiCアノード層12,p型のSiCドリフト層13とn+型SiCカソード層14をn型SiC基板21上にエピタキシャル成長により形成してから、n型SiC基板21を除去した。つまり、p型基板に見立てるp+型4H-SiCアノード層12は、エピタキシャル成長により作製するから、バルク成長で作製されるp型基板に比べて結晶成長速度が遅く、p型ドーパントであるアルミニウムの濃度を上げても、結晶品質が良くなる。したがって、この結晶品質が良いp+型4H-SiCアノード層12を基板に見立てることができ、SiC基板をp型とした結晶品質の良いSiCダイオード素子を実現できる。

(もっと読む)

バイポーラ半導体素子

【課題】表面欠陥を低減でき、オン電圧ドリフトを抑制できるバイポーラ半導体素子を提供する。

【解決手段】このSiC GTOによれば、メサ状のp型アノードエミッタ層5の長側面5Bが延在している方向を、〈11−20〉方向としたオフ方向から角度φ=60°だけ傾斜させた方向とした。これにより、長側面5Bは、{01−10}面となり、{11−20}面である短側面5Cに比べて、表面欠陥が入りにくくなる。また、長側面5Bの延在方向を、上記オフ方向から角度φ=60°だけ傾斜させたことで、長側面5Bの延在方向とオフ方向とが一致している場合(φ=0°)に比べて、メサ状のp型アノードエミッタ層5の長側面5Bに現れる{0001}面の層の数を減らすことができて、{0001}面の層内に入る表面欠陥を減少できる。

(もっと読む)

半導体装置

【課題】保持電流特性に影響を与えずに、点弧動作感度の高感度化を実現するサイリスタ(半導体装置)を提供する。

【解決手段】サイリスタ100は、p領域1とn領域2とp領域3とn領域4とが順に接合されるサイリスタを有する。また、サイリスタ100は、n領域2とp領域3とに接して形成され、n領域2とp領域3との接合耐圧より接合耐圧が低い低耐圧領域10を有する。低耐圧領域10は、該領域において接合面にかかる電界方向の該領域幅が、サイリスタ100のブレークダウン電圧によって該領域に生成される空乏層幅より広く、サイリスタ100のブレークオーバ電圧によって接合面がブレークダウンする範囲において狭く形成される。

(もっと読む)

発光チップ、発光装置、プリントヘッドおよび画像形成装置

【課題】複数の発光点を並行して点灯させうる発光チップ等を提供する。

【解決手段】発光チップC1(C)は、基板80上に列状に配列された発光サイリスタL1、L2、L3、…から構成される発光サイリスタ列、転送サイリスタT1、T2、T3、…から構成される転送サイリスタ列、許可ダイオードDe1、De2、De3、…から構成される許可ダイオード列、ダイオードスイッチDs1、Ds2、Ds3、…から構成されるダイオードスイッチ列を備える。さらに、第1許可信号φE1に対して、反転した第2許可信号φE2を設定する許可信号設定部170、および転送サイリスタ列を駆動する第1転送信号φ1または第2転送信号φ2に応じて、第1点灯信号φI1または第2点灯信号φの電位を設定する点灯信号設定部160を備える。

(もっと読む)

バイポーラ半導体素子

【課題】制御電極による制御能力を向上できるバイポーラ半導体素子を提供する。

【解決手段】このゲートターンオフサイリスタは、隣り合う2列R1,R2のメサ型のアノードエミッタ層5の間で列方向に延在している列間の第1のコンタクトホール20Bに形成された第1のゲート端子15だけでなく、各列R1,R2の端側で各列R1,R2に沿って列方向に延在している端側の第2,第3のコンタクトホール20C,20Dに形成された第2,第3のゲート端子16,17を有する。これにより、列間の第1のゲート端子15と端側の第2,第3のゲート端子16,17とでターンオフ時の転流を分担できて、転流の不揃いを抑制できる。

(もっと読む)

逆阻止型サイリスタ

【課題】本発明は、高い周波数のスイッチング動作に対応でき、且つ、電力損失を低減できる逆阻止型サイリスタを提供することを目的とする。

【解決手段】P領域(1a、1b)とN領域(2a、2b)とP領域3とN領域4とが順に接合された逆阻止型サイリスタ100は、P領域(1a、1b)からN領域4に順方向電圧が印加された場合にP領域(1a、1b)とN領域4の間を導通させる前の最大電圧値を示すブレークオーバ電圧が、N領域4からP領域(1a、1b)に逆方向電圧が印加された場合にN領域4とP領域(1a、1b)の間の導通を阻止する限界の電圧値を示すブレークダウン電圧より低くなるように電圧差を生じさせる電圧差生成領域30を有する。

(もっと読む)

短絡型サイリスタ

【課題】本発明は、保持電流特性に影響を与えずに、オン状態に移行するブレークオーバ電圧の低電圧化を実現する短絡型サイリスタを提供することを目的とする。

【解決手段】第1領域(P領域1)と第2領域(N領域2)と第3領域(P領域3)と第4領域(N領域4)とが順に接合され、第1領域(P領域1)と第2領域(N領域2)を短絡させる電極11を有する短絡型サイリスタ100は、第3領域(P領域3)に接して形成され、第3領域(P領域3)より不純物濃度が高い第5領域(P++領域31)と、第2領域(N領域2)及び第5領域(P++領域31)に接して形成され、第2領域(N領域2)より不純物濃度が高い第6領域(N++領域41)とを有し、第5領域(P++領域31)の不純物濃度と第6領域(N++領域41)の不純物濃度とによってブレークオーバ電圧値が設定される。

(もっと読む)

圧接型半導体装置

【課題】主電極にめっきを施しつつ、主電極の端部を含む面に圧接電極を面接合させることができる圧接型半導体装置を提供する。

【解決手段】半導体基体12と、めっき処理され、該半導体基体12の主面に固着されためっき付き主電極22と、該めっき付き主電極22のめっき22aが形成された面に重なるように圧接された圧接電極と、を備える。そして、該めっき付き主電極22の側面には溝22bが形成され、該溝22bは、該半導体基体12と該めっき付き主電極22が重なる部分の直上領域より外側に形成されたことを特徴とする。

(もっと読む)

駆動装置、プリントヘッド及び画像形成装置

【課題】発光サイリスタを駆動するための駆動回路の発振を防止する。

【解決手段】オン/オフ指令信号DRVON−PがHレベルの場合、PMOS43及びNMOS44からなるCMOSインバータ42の出力側のデータ端子DAがLレベルとなる。この結果、プリントヘッド13側の共通端子INも0Vとなり、各発光サイリスタ210のアノード・カソード間に電源電圧VDDが印加される。この際、発光サイリスタ210−1〜210−nの内、発光指令されている発光サイリスタ210のゲートのみを、シフトレジスタ110によって選択的にHレベルとすることで、発光指令されているサイリスタ210がターンオンする。NMOS44のチャネル形成予定領域に、サブストレート領域と同極性の不純物が注入されているので、NMOS44の閾値電圧が増加し、駆動回路41の発振を防止できる。

(もっと読む)

パワー半導体デバイス

4層npnp構造、カソード面11およびアノード面12があり、ゲート電極4を介してターンオフできるパワー半導体デバイス1。カソード電極2とアノード電極3との間に以下の順で複数の層が配置される。−外側縁によって囲まれ、中央領域がある第1導電型カソード層5、カソード層5はカソード電極2と直接の電気的コンタクトにある,−第2導電型ベース層6,−カソード層5よりも低いドーピング濃度を有する第1導電型ドリフト層7、アノード電極3と電気的コンタクトにある第2導電型アノード層8。ゲート電極4は、カソード面11上にカソード電極2の横に配置され、ベース層6と電気的コンタクトにある。ベース層6は、カソード層5の中央領域に接触している、連続的な層としての、第1の深さに最大ドーピング濃度がある少なくとも1つの第1の層61を具備する。第1の層61よりも高いドーピング濃度を有し、第1の層61とカソード層5との間に配置され、第1の層61のほうを向いているカソード層5の外側縁をカバーする第2導電型抵抗減少層10,10’,10’’、この中でカソード層5の外側縁とベース層6との間の接合での抵抗が低減される。 (もっと読む)

駆動回路、駆動装置及び画像形成装置

【課題】発光サイリスタ等の被駆動素子の破壊を防止して信頼性の向上を図る。

【解決手段】ドライバICは、第1端子と、第2端子と、前記第1端子及び前記第2端子間の導通状態を制御する制御端子と、を有する被駆動素子が複数配列された被駆動素子アレイを時分割駆動する回路である。被駆動素子アレイは、隣接配置された被駆動素子毎に被駆動素子群が形成され、各被駆動素子群における第1端子群、第2端子群、及び制御端子群の内、各第2端子群がグランドにそれぞれ接続され、各制御端子群が共通母線にそれぞれ接続されている。ドライバICは、各共通母線をそれぞれ駆動する複数のゲート駆動用バッファ162を備えている。各バッファ162は、電源VDDと共通母線OUTとの間に直列に接続されたスイッチ用PMOS403及び降圧用PMOS406と、共通母線OUTとグランドGNDとの間に接続されたスイッチ用PMOS404とを有している。

(もっと読む)

半導体複合装置、この製造方法、光プリントヘッド及び画像形成装置

【課題】製造工程を簡略化して低コスト化を図る。

【解決手段】半導体複合装置は、シフトレジスタと、これにより時分割駆動される半導体薄膜からなる発光サイリスタアレイとにより構成されている。この製造方法は、例えば、シフトレジスタを構成する複数の回路構成素子243が形成されたシリコン基板241を用意する。シフトレジスタにより駆動される複数の発光サイリスタ261〜264が配列された結晶構造を持った半導体薄膜からなる発光サイリスタアレイを、パッシベーション膜242を介してシリコン基板241上に貼着する。フォトリソグラフィ法により、複数の回路構成素子243間を電気的に接続してシフトレジスタを形成すると共に、そのシフトレジスタ及び複数の発光サイリスタ261〜264間を電気的に接続するメタル配線265〜267を形成する。

(もっと読む)

半導体装置の動作方法

【課題】ワイドギャップ半導体素子を動作させる半導体装置の動作方法であって、積層欠陥の発生による素子破壊を招くことなく簡単に実現できるとともに、定格電流に達するまでの時間を短縮できるものを提供すること。

【解決手段】ゼロから定格電流までの或る電流の値I1を設定して、上記通電電流がゼロからI1に達するまでの電流上昇率を一定値dI1/dtとし、上記通電電流がI1から上記定格電流に達するまでの電流上昇率をdIn/dtとする。上記ワイドギャップ半導体素子内の積層欠陥の発生による上記ワイドギャップ半導体素子の破壊を防止するように、上記dI1/dtは、一定値で、かつ0.5秒<(I1÷(dI1/dt))なる関係式を満たす。上記dIn/dtは、(dI1/dt)<(dIn/dt)なる関係式を満たす。

(もっと読む)

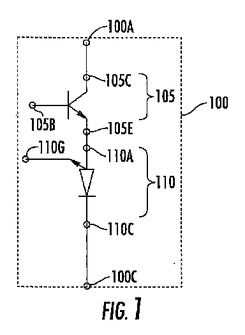

非負の温度係数及び関連した制御回路を有するワイド・バンドギャップ・バイポーラ・ターンオフ・サイリスタ

アノード、カソード及びゲート端子を有するワイド・バンドギャップ・サイリスタと、ベース、コレクタ及びエミッタ端子を有するワイド・バンドギャップ・バイポーラ・トランジスタを含む。バイポーラ・トランジスタとサイリスタとが直列接続されるように、バイポーラ・トランジスタのエミッタ端子は、サイリスタのアノード端子に直接結合される。バイポーラ・トランジスタ及びサイリスタは、ワイド・バンドギャップ・バイポーラ・パワー・スイッチング・デバイスを特徴付け、ワイド・バンドギャップ・バイポーラ・パワー・スイッチング・デバイスは、非導通状態と、ベース端子への第一制御信号の印加及びゲート端子への第二制御信号の印加に応答してバイポーラ・トランジスタのコレクタ端子に対応する第1主端子とサイリスタのカソード端子に対応する第2主端子との間に電流を流すことができる導通状態との間を切り替えるように構成される。関連した制御回路も開示される。  (もっと読む)

(もっと読む)

サイリスタ

【課題】サイリスタ内の残存キャリアがサイリスタ相互に及ぼす影響を抑制し、転流時臨界電圧上昇率を改善し、小型化を図ることができ、更に電流上昇率耐量を向上することができるサイリスタを提供する。

【解決手段】逆並列接続構造を有するサイリスタ1において、第1の主サイリスタと第2の主サイリスタとの間にpn接合によって双方を分離する接合分離領域210が配設される。第1の主サイリスタは第5の半導体領域25、第3の半導体領域23、第1の半導体領域21及び第7の半導体領域27により構成される。第2の主サイリスタは第4の半導体領域24、第2の半導体領域22、第7の半導体領域27及び第8の半導体領域28により構成される。

(もっと読む)

発光サイリスタ、発光素子アレイ、発光装置および画像形成装置

【課題】 ベース層のキャリア濃度および厚み寸法を大きく設定することなく、発光強度に対する電流増幅率βの影響を抑制することのできる発光サイリスタ、発光素子アレイ、発光装置および画像形成装置を提供することである。

【解決手段】 発光サイリスタは、基板上に第1半導体層、第1半導体層と反対導電型の第2半導体層、第1半導体層と同じ導電型の第3半導体層、および第1半導体層と反対導電型の第4半導体層がこの順に積層されており、第3半導体層のバンドギャップは、第2半導体層のバンドギャップと略同一、かつ、第1および第4半導体層のバンドギャップより狭幅であり、第3半導体層は、基板側の第1領域と基板と反対側の第2領域とからなり、かつ、第1領域の不純物濃度は1×1016(cm−3)未満である。

(もっと読む)

1 - 20 / 66

[ Back to top ]