Fターム[5F005GA03]の内容

Fターム[5F005GA03]に分類される特許

1 - 16 / 16

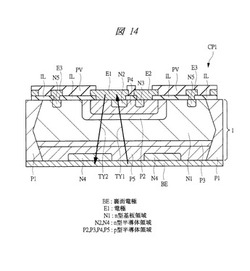

半導体装置およびその製造方法

【課題】トライアックが形成された半導体装置の性能を向上させる。

【解決手段】裏面電極BEと電極E1の間に、p型半導体領域P5,P3、n型基板領域N1、p型半導体領域P2,P4およびn型半導体領域N2によってサイリスタTY1が形成され、p型半導体領域P4,P2、n型基板領域N1、p型半導体領域P3,P5およびn型半導体領域N4によってサイリスタTY2が形成されている。サイリスタTY1とサイリスタTY2は、裏面電極BEと電極E1の間に流れる電流の向きが反対である。高不純物濃度のp型半導体領域P4は、低不純物濃度のp型半導体領域P2に内包されるように形成され、高不純物濃度のp型半導体領域P5とn型基板領域N1との間には、低不純物濃度のp型半導体領域P3が介在している。

(もっと読む)

半導体装置の動作方法

【課題】ワイドギャップ半導体素子を動作させる半導体装置の動作方法であって、積層欠陥の発生による素子破壊を招くことなく簡単に実現できるとともに、定格電流に達するまでの時間を短縮できるものを提供すること。

【解決手段】ゼロから定格電流までの或る電流の値I1を設定して、上記通電電流がゼロからI1に達するまでの電流上昇率を一定値dI1/dtとし、上記通電電流がI1から上記定格電流に達するまでの電流上昇率をdIn/dtとする。上記ワイドギャップ半導体素子内の積層欠陥の発生による上記ワイドギャップ半導体素子の破壊を防止するように、上記dI1/dtは、一定値で、かつ0.5秒<(I1÷(dI1/dt))なる関係式を満たす。上記dIn/dtは、(dI1/dt)<(dIn/dt)なる関係式を満たす。

(もっと読む)

半導体装置の動作方法

【課題】ワイドギャップ半導体素子を動作させる半導体装置の動作方法であって、積層欠陥の発生による素子破壊を招くことなく簡単に実現できるものを提供すること。

【解決手段】この発明の半導体装置の動作方法では、ワイドギャップ半導体素子の通電開始時に通電電流Iを或る電流上昇率でゼロから定格電流Inまで上昇させる。ワイドギャップ半導体素子内の積層欠陥の発生によるワイドギャップ半導体素子の破壊を防止するように、通電電流Iをゼロから定格電流Inまで上昇させるソフトスタート時間tsを0.5秒から10秒までの範囲内に設定する。

(もっと読む)

圧接型大電力用サイリスタモジュール

【課題】圧接型大電力用サイリスタモジュールの上下方向寸法を小型化する。

【解決手段】放熱板1、絶縁板11、コモンバー12、スペーサ181、サイリスタチップ113、スペーサ183,24及びカソード端子バー18を圧接手段19により上下方向に圧接する。四角形のサイリスタチップ113を用い、四角形のスペーサ181,183をサイリスタチップ113よりも小さくする。絶縁性ホルダ182,184とによってスペーサ181,183とを包囲する。サイリスタチップ113のゲート電極113b上に配置されたコイルバネ型ゲート電極信号線15のコイル部分15aとスペーサ14とを絶縁性ゲートスペーサ316,317によって絶縁する。コイルバネ型ゲート電極信号線15の水平方向に延ばされた部分15bを絶縁被覆し、スペーサ14の収容溝14b内に収容する。水平方向に延ばされた部分15bの根元側部分15b2を絶縁性ゲートスペーサ316,317によって狭持する。

(もっと読む)

半導体装置

【課題】可制御電流が大きく、低損失のパワー半導体装置に適したアセンブリ構造を提供すること。

【解決手段】金属基板125と、絶縁板126と、金属膜7とを備える。金属基板125上に、ワイドギャップ半導体層からなるバイポーラスイッチング素子20を備える。金属膜7上に、n型ワイドギャップ半導体層を含むダイオード素子13を備える。バイポーラスイッチング素子20の低電位側の主電極32は、金属基板125に直接に半田付けされている。一方、バイポーラスイッチング素子20の高電位側の主電極29は、金属膜7に配線34、7aを介して電気的に接続されている。ダイオード素子13の低電位側の主電極32は、金属膜7に直接に半田付けされている。一方、ダイオード素子13の高電位側の主電極6は、金属基板125に配線8を介して電気的に接続されている。

(もっと読む)

半導体装置の製造方法

【課題】可制御電流が大きく、低損失のパワー半導体装置を作製すること。

【解決手段】順方向特性にビルトイン電圧を有するワイドギャップバイポーラ半導体素子を形成するように、互いに異なる導電型を有する少なくとも2層のワイドギャップ半導体層1、2、3を積層する。積層欠陥を有するワイドギャップ半導体層1、2、3に、所定の照射エネルギーのγ線、電子線または荷電粒子線を所定量照射する。

(もっと読む)

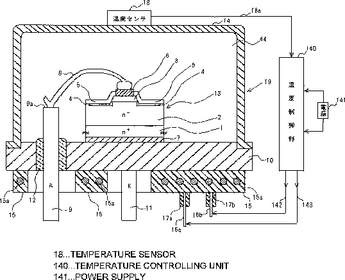

半導体装置及びその製造方法、動作方法、この半導体装置を用いた電力変換装置

【課題】可制御電流が大きく、かつ低損失のパワー半導体装置を得ること。

【解決手段】ワイドギャップ半導体を用いた、順方向特性にビルドイン電圧を有するワイドギャップバイポーラ半導体素子13を備える。ワイドギャップバイポーラ半導体素子13を収納し、ワイドギャップバイポーラ半導体素子13を外部の装置に接続するための電気接続手段7、8、9、11を有する半導体パッケージ10、14を備える。半導体パッケージ10、14内の前記ワイドギャップバイポーラ半導体素子13を50℃以上、750℃以下の温度範囲に加熱するための発熱手段15を備える。

(もっと読む)

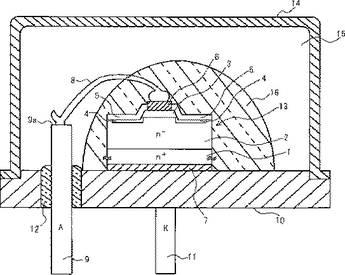

圧接型大電力用サイリスタモジュール

【課題】圧接型大電力用サイリスタモジュール全体の上下方向寸法を小型化する。

【解決手段】放熱板1上に絶縁板11、アノード端子バー12を配置し、下面にアノード電極13aを有し、上面の中心部分にゲート電極13bを有し、その周りに環状のカソード電極13cを有するサイリスタチップ13をそれらの上に配置し、カソード電極13c上に導電性カソードスペーサを14配置し、ゲート電極13b上にコイルバネ型ゲート電極信号線15を配置し、導電性カソードスペーサ14とコイルバネ型ゲート電極信号線15とを絶縁する筒状の絶縁性ゲートスペーサ16を配置し、導電性カソードスペーサ14上にカソード端子バー18を配置し、それらを圧接手段19により上下方向に圧接し、コイルバネ型ゲート電極信号線15の上端の水平方向に延ばされた部分15bを絶縁性ゲートスペーサ16の収容溝16aの底面16a2と協働して狭持する狭持突起17bを絶縁性蓋部材17の下面に形成した。

(もっと読む)

圧接型半導体装置およびその製造方法

【課題】本発明は、圧接型半導体装置に組み込む際に付着していた異物を発見しやすくし、より容易に取り除くことができる半導体素子およびその製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体素子は、第1の導電型の第1の半導体層と、前記第1の半導体層の所定の領域上に積層された第2の導電型の第2の半導体層と、前記第1の半導体層上に形成された第1の電極層と、前記第2の半導体層上に形成された第2の電極層と、前記第1の電極層上に形成された絶縁層と、前記絶縁層および前記第2の電極層の上に貼り合わされた導電性シートとを備えたことを特徴とする。

(もっと読む)

光転送アレイ装置およびその製造方法、発光装置ならびに画像形成装置

【課題】 隣接する2つの光転送用発光素子間においてより確実に発光状態を転送することのできる光転送アレイ装置およびその製造方法を提供する。

【解決手段】 光転送アレイ装置1は、相互に間隔をあけて配置される複数のスイッチ素子Tと、隣接する2つのスイッチ素子T間に設けられ、隣接する2つのスイッチ素子Tのうち、一方のスイッチ素子Tからの光を他方のスイッチ素子Tに導く導波体17とを含んで構成される。導波体17の表面103は反射集光領域104を有し、反射集光領域104は、外方に凸となった凸曲面状に形成され、一方のスイッチ素子Tからの光が反射集光領域104で反射されると、他方のスイッチ素子Tに入射するように形成される。

(もっと読む)

半導体集積回路装置

【課題】本発明は、配線抵抗のばらつきに依ることなく、単位面積当たりのESD耐圧効率を高めることが可能な半導体集積回路装置を提供することを目的とする。

【解決手段】本発明に係る半導体集積回路装置において、SCRのアノードとなるp型半導体領域3は、アノード電極9との導通路10a〜10dが複数接続されるコンタクト領域3sを除いて、そのシリサイド化処理がブロックされて成る構成とされている。

(もっと読む)

半導体装置及びその製造方法、この半導体装置を用いた電力変換装置

可制御電流が大きく、かつ低損失のパワー半導体装置を得るために、ワイドギャップ半導体を用いるバイポーラ半導体素子の温度を、ヒーターなどの加熱手段を用いて上昇させる。その温度は、ワイドギャップバイポーラ半導体素子の、温度の上昇に応じて低下するビルトイン電圧の低下量に対応する前記ワイドギャップバイポーラ半導体素子の定常損失の減少量が、前記温度の上昇に応じて増加するオン抵抗の増加量に対応する前記定常損失の増加量よりも大きくなる温度を超える温度にする。  (もっと読む)

(もっと読む)

半導体装置

【課題】駆動条件に応じて駆動領域を変更することができ、従来に比べて損失の低減を図ることのできる半導体装置を提供する。

【解決手段】3つのゲート電極パッド3a,3b,3cは、3つの駆動領域2a,2b,2cに夫々対応して設けられ、3つの駆動領域2a,2b,2cには、互いに電気的に分離されたゲート電極4a,4b,4cが配置されている。そして、駆動条件に応じてゲート信号によって、駆動する駆動領域2a,2b,2cの数を変更可能とされている。

(もっと読む)

高耐熱半導体装置

150℃以上の高温で使用するSiCなどのワイドギャップ半導体装置において、ワイドギャップ半導体素子の絶縁性を改善し、高耐電圧のワイドギャップ半導体装置を得るために、ワイドギャップ半導体素子の外面を合成高分子化合物で被覆する前記合成高分子化合物は、シロキサン(Si−O−Si結合体)による橋かけ構造を有する1種以上の有機珪素ポリマーAと、シロキサンによる線状連結構造を有する1種以上の有機珪素ポリマーBとをシロキサン結合により連結させた有機珪素ポリマーC同士を、付加反応により生成される共有結合で連結させて三次元の立体構造に形成している。  (もっと読む)

(もっと読む)

半導体装置

【課題】MOSFETを含む半導体装置において、チップサイズの縮小に対応できる過熱保護用のサイリスタチップの実装を実現する。

【解決手段】半導体装置1は、一方の主面1aにゲート電極Gとソース電極Sとを有するMOSFETを備えている。ソース電極S上に所定の温度以上で導通動作するサイリスタチップ2が配置されている。MOSFETは、N型の半導体基板11の一方の面(主面1a)にP型の拡散層12、その内部にN型の拡散層13をそれぞれ形成し、拡散層13に接続したソース電極Sと、チャネル部に延伸部を対向させたゲート電極Gとをそれぞれ形成し、半導体基板11の他方の面にドレイン電極Dを形成した構造をもつ。サイリスタチップ2のアノード電極Aはゲート電極Gに接続され、第1カソード電極K1はソース電極Sと直接電気的に接続され、第2カソード電極K2は第1カソード電極K1とサイリスタチップ2の内部で接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】 水分の浸入や汚染物質の侵入を防止し、長期間の使用に対する電気的信頼性を向上することができ、更に外部応力に対する半導体素子の損傷を防止し、半導体素子の電気的特性の変化を防止することができる半導体装置を提供する。

【解決手段】 樹脂封止型半導体装置において、支持基板1上にベベル端面を有する半導体素子4、例えばダイオードが取り付けられ、この半導体素子4上に中間接続導体6が取り付けられている。中間接続導体6の幅寸法(直径寸法)L3は半導体素子4の第2の主電極44の幅寸法(直径寸法)L2以上に設定されている。中間接続導体6の周縁部分を第2の主電極44の周縁部分よりも突出させたことによって、半導体素子4のベベル端面45上には、中間接続導体6の表面上の一部に渡る広範囲で保護樹脂10を形成することができる。

(もっと読む)

1 - 16 / 16

[ Back to top ]