Fターム[5F033GG00]の内容

半導体集積回路装置の内部配線 (234,551) | 基板材料(シリコンを除く) (2,930)

Fターム[5F033GG00]の下位に属するFターム

Fターム[5F033GG00]に分類される特許

1 - 20 / 240

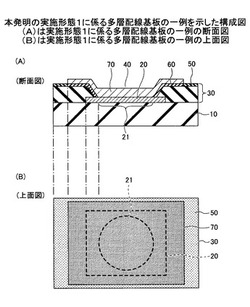

多層配線基板、アクティブマトリクス基板及びこれを用いた画像表示装置、並びに多層配線基板の製造方法

【課題】上部配線層と下部配線層とを、微細なコンタクトホールを介して接続する多層配線基板、アクティブマトリクス基板及びこれを用いた画像表示装置、並びに多層配線基板の製造方法を提供する。

【解決手段】基板10上に形成された第1の導電層20と、層間絶縁層30と、第2の導電層70とを有し、前記層間絶縁層に形成されたコンタクトホール40を介して前記第1の導電層と前記第2の導電層とが電気的に接続された構造を有する多層配線基板において、

前記層間絶縁層は、前記コンタクトホールを含まない第1の領域50と、前記コンタクトホールを含み、該第1の領域よりも表面エネルギーが高く形成された第2の領域60とを有し、

前記第1の導電層の前記コンタクトホール内の領域は、前記第2の領域よりも表面エネルギーが高く、

前記第2の導電層は、前記層間絶縁層の前記第2の領域に接触して堆積形成され、前記コンタクトホールを介して前記第1の導電層と接続されている。

(もっと読む)

回路基板、回路基板の製造方法、表示装置および電子機器

【課題】被蒸着膜を高精細なパターンで形成することが可能な蒸着用マスクを提供する。

【解決手段】蒸着用マスクは、1または複数の第1開口部を有する基板と、この基板の一主面側に設けられると共に、各第1開口部と対向して1または複数の第2開口部を有する高分子膜とを備える。蒸着の際には、蒸着材料が第1開口部および第2開口部を順に通過することにより、第2開口部に対応した所定のパターンで被蒸着膜が形成される。基板と高分子膜とを組み合わせて用いることにより、機械的強度を保持しつつも、金属膜のみで構成されている場合に比べ、第2開口部において微細かつ高精度な開口形状を実現できる。

(もっと読む)

表示装置

【課題】配線等のパターンを、材料の利用効率を向上させ、かつ、作製工程を簡略化して得られた表示装置である。また配線等のパターンを所望の形状で制御性よく形成された導電膜を有する表示装置である。

【解決手段】トランジスタ上の第1の導電膜と、第2の導電膜とは、複数の屈曲点を有するコの字状に設けられる。本形状であっても、第1の導電膜と、第2の導電膜とはパターンを所望の形状で制御性よく形成される。なお、第1の導電膜と第2の導電膜は、共通電極層と、画素電極層となることができる。

(もっと読む)

ボンディングパッド構造を有する裏面照射型センサーとその製造方法

【課題】ボンディングパッド構造を有する裏面照射型センサーとその製造方法を提供する。

【解決手段】本発明は半導体構造を提供する。半導体構造は、正面と背面を有する装置基板;装置基板の正面上に設置される相互接続構造;および、相互接続構造に接続されるボンディングパッドを含む。ボンディングパッドは、誘電材料層中の凹部領域;凹部領域間に挿入される誘電材料層の誘電体メサ; および、凹部領域中と誘電体メサ上に設置される金属層を含む。

(もっと読む)

半導体装置

【課題】半導体装置において、少なくとも容量素子とトランジスタとを有する回路要素が占める面積を小さくする。

【解決手段】第1のトランジスタと第2のトランジスタと容量素子とを有する半導体装置において、第2のトランジスタよりも上方に第1のトランジスタ及び容量素子を配置する。そして、第1のトランジスタのソース又はドレインの一方と、容量素子の一方の電極とを兼ねる共通電極を設ける。さらに、容量素子の他方の電極を共通電極よりも上方に配置する。

(もっと読む)

半導体基板内の埋込ボイドを検出するための方法

【課題】半導体基板内又は基板上に形成された構造内の埋込ボイドを検出するための方法を提供する。

【解決手段】構造を形成するための少なくとも1つの処理ステップを実施する工程と、基板の質量M1を測定する工程と、熱処理を実施する工程と、基板の質量M2を測定する工程と、前記実施した熱処理の前後で測定した基板の質量の差を計算する工程と、前記質量の差を所定値と比較することにより、前記構造内の埋込ボイドの存在を推測する工程とを含む。

(もっと読む)

半導体素子の製造方法

【課題】 製造コストの低減が可能な半導体素子の製造方法を提供する。

【解決手段】 第1再配線層400は、金属バンプ層320の一部分を露出するように形成される。第1再配線層400は、第1拡張パッド部410、第1延長部420及び第1連結部430を備える。第1拡張パッド部410は、金属パッド120と電気的に接続し、外部装置と接続する。第1延長部420は、金属バンプ層320上から第1拡張パッド部410上に延びるように形成される。第1連結部430は、スクライブレーン領域SRに形成され、複数の第1再配線層400を電気的に連結する。第1再配線層400は、銀、ニッケルまたは銅を含むペーストまたはインクを利用したプリンティング方法、または、ロールオフセットプリンティング方法によって形成される。これにより、金属パッドと再配線層との接触抵抗を小さくするとともに、製造コストを低減することができる。

(もっと読む)

ボンディングパッドおよびシールド構造を有する半導体装置およびその製造方法

【課題】ボンディングパッドおよびシールド構造を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体装置の正面と背面に対応する正面と背面を有する装置基板と、装置基板の正面上に形成される金属層部と、半導体装置の背面に設置され、金属層部と電気的に接続するボンディングパッドと、装置基板の背面上に設置されるシールド構造と、を含み、シールド構造とボンディングパッドは異なる厚さを有する。

(もっと読む)

半導体装置

【課題】パッドの下方に半導体素子を設けることができ、信頼性の高い半導体装置を提供する。

【解決手段】素子形成領域10Aと該素子形成領域10Aの周囲に設けられた素子分離領域20とを有する半導体層10と、前記素子形成領域10A内に形成された素子30と、前記半導体層10の上方に設けられた層間絶縁層60と、前記層間絶縁層60の上方に設けられ、平面形状が短辺と長辺とを有する長方形である電極パッド62であって、前記素子30と平面視で少なくとも一部が重複する前記電極パッド62と、を含み、前記半導体層10において、前記電極パッド62の前記短辺の鉛直下方から外側に位置する所定の範囲は、素子禁止領域12である。

(もっと読む)

導電性構成部品、貫通ビア及び導電性貫通ウェーハ・ビアを含む半導体構成部品を製造するためのプロセス及び集積化スキーム

【課題】公知のプロセスよりも高速であり、充てんされたビアにボイド、凹み又はキーホールを残さず、製造の費用効果が高い、改善された方法を提供する。

【解決手段】第1の表面214及び対向する第2の表面216を有する基板212を設け、基板の第1の表面に部分的にのみ前記基板の中に広がる少なくとも1つのブラインドビア218を形成する。酸化材料によって前記少なくとも1つのブラインドビアの表面をパッシベーションし、少なくとも一つのブラインドビアの酸化材料の表面に銅を含むシード材料228を、シード材料を前記少なくとも一つのブラインドビアの内部に閉じ込め、かつ、基板の前記第1の表面を露出させるように形成する。シード材料の上に導電性材料230を前記少なくとも一つのブラインドビアを充填するように無電解めっきし、少なくとも一つのブラインドビアの導電性材料を露出させるために基板の前記第2の表面に研磨平坦化を実施する。

(もっと読む)

表示装置およびその製造方法

【課題】配線にCuを用いる配線の電気抵抗値とTFTの電気特性値を均一にするアクティブマトリクス型表示装置及びその製造方法を提供する。

【解決手段】基板およびTFTを有する表示装置の製造方法であって、TFTは、電極および電極近接層を有し、電極は、銅および銅以外の添加元素を含み、以下の工程を含む表示装置の製造方法(A)基板の上に電極および電極近接層が形成される工程、(B)電極または電極近接層がオゾン水で洗浄される工程、(C)前記(B)の工程後の熱処理により、電極と電極近接層との界面に、酸素を含む酸化物膜が形成される工程。

(もっと読む)

半導体チップとその製造方法、半導体装置

【課題】立体的な集積に適した、電磁妨害耐性に優れる半導体チップを提供する。また、その半導体チップを用いた、高い電磁妨害耐性と高い処理能力を両立する半導体装置を提供する。

【解決手段】能動素子もしくは受動素子と、それらの素子を電気的に接続する配線部を備えた半導体チップについて、配線部を被覆するように導電性薄膜を設ける。この導電性薄膜は配線部に対して、不要電磁波を遮蔽するシールドとして働くので、半導体チップの電磁妨害耐性が向上する。また、この半導体チップを三次元集積半導体装置に組み込むことで、隣接するチップをフェイス・トゥ・フェイス接続した場合でも、チップ間のクロストークを遮断できる。

(もっと読む)

発光装置の作製方法

【課題】微細な配線パターンを備えた発光装置の作製方法の提供。

【解決手段】Inと、Gaと、Znとを有する酸化物半導体層を形成し、酸化物半導体層上に第1の導体パターンを形成し、第1の導体パターンより微細な第2の導体パターンを形成し、前記第2の導体パターンと電気的に接続する発光素子を形成する発光装置の作製方法であって、第2の導体パターンは、酸化物半導体層を横断する。

(もっと読む)

回路基板の製造方法

【課題】絶縁膜に形成されるヴィアホールの直径を縮小化することが可能で、高密度化に寄与することのできる回路基板の製造方法を提供する。

【解決手段】本発明の回路基板の製造方法は、基板10上に第1導電体を形成する第1導電体形成工程と、第1導電体を被覆する様にゲート絶縁膜21を成膜する第1絶縁膜成膜工程と、第1導電体上のゲート絶縁膜21に貫通孔32を開口して、当該貫通孔32を介して第1導電体の表面および基板の表面を部分的に露出させる貫通孔形成工程と、貫通孔32内に露出する第1導電体の表面を撥液化させる撥液化工程と、貫通孔32内に露出する第1導電体以外の領域に第2絶縁膜を形成する第2絶縁膜形成工程と、を含むことを特徴とする。

(もっと読む)

トランジスタアレイ、およびその製造方法

【課題】簡略化された構成を有するトランジスタアレイを、簡易的に製造することが可能なトランジスタアレイの製造方法を提供することを主目的とする。

【解決手段】金属基板を用い、上記金属基板上に、絶縁性材料からなり、貫通孔を有する絶縁層を形成する絶縁層形成工程と、上記絶縁層上に、ドレイン電極が上記絶縁層に形成された貫通孔を介して上記金属基板に接続されるように薄膜トランジスタを形成する、薄膜トランジスタ形成工程と、上記金属基板をパターニングすることにより、上記金属基板を画素電極とする画素電極形成工程と、を有することを特徴とする、トランジスタアレイの製造方法を提供することにより、上記課題を解決する。

(もっと読む)

膜形成用組成物および該組成物を用いた薄膜トランジスタ

【課題】 本発明の目的は、有機半導体素子の製造プロセス適応性に優れる膜形成用組成物および該組成物を用いた薄膜トランジスタを提供することである。

【解決手段】上記課題は、必須成分として、(a)式(I)で表される構造を0.6mmol/g以上含有する有機化合物と、(b)有機溶剤とを含有する膜形成用組成物および該組成物を有機半導体素子の絶縁膜等に用いる薄膜トランジスタにより達成される。該薄膜トランジスタは、閾値電圧が高く、ON/OFF電流比も高い特性の良好なトランジスタとなる。

【化1】 (もっと読む)

(もっと読む)

ポリマー薄膜における自己整合ビアホールの形成

【課題】有機電界効果トランジスタにおけるビア形成を、低コストで効率的なプロセスで実現する。

【解決手段】誘電層106内にビア113を形成する際、まず各ビア位置にパターン化された導電材よりなるポストを印刷し、次にパターン化されていない誘電層106を堆積させ、次に第2のパターン化された導電層を堆積させる。ビア113は、誘電層106を堆積した後、第2の導電層を堆積する前に、ポストをフラッシュアニールすることにより形成される。

(もっと読む)

金属銅膜の作製方法及び印刷金属銅パターン

【課題】印刷形成が可能である銅系粒子堆積層を、基板密着性、低体積抵抗率、基板ダメージがなく深部まで還元する処理方法であり、且つ印刷塗布部外への銅の析出を抑制した、金属銅膜の作製方法、及び、作製した印刷金属銅パターンを提供する。

【解決手段】基板上に形成された、酸化銅からなる粒子を含む銅系粒子堆積層を、120℃以上において、ガス状のギ酸と、ガス状の1価のアルコール/エステル/ケトンから選択される少なくとも1種の有機溶剤と混合ガスにより処理する、金属銅膜の作製方法。

(もっと読む)

半導体デバイス用基板洗浄液及び洗浄方法

【課題】基板表面を腐食することなく微粒子付着による汚染、有機物汚染及び金属汚染を同時に除去することができ、しかも水リンス性も良好で、短時間で基板表面を高清浄化することができる半導体デバイス用基板洗浄液を提供する。

【解決手段】

半導体デバイス製造における化学的機械的研磨工程の後に行われる、半導体デバイス用基板の洗浄工程に用いられる洗浄液であって、以下の成分(A)〜(D)を含有してなる半導体デバイス用基板洗浄液。

(A)有機酸

(B)スルホン酸型アニオン性界面活性剤

(C)ポリビニルピロリドン及びポリエチレンオキシド−ポリプロピレンオキシドブロック共重合体から選ばれる少なくとも1種の高分子凝集剤

(D)水

(もっと読む)

半導体装置

【課題】電極パッド直下の領域を有効領域とする半導体装置の提供を目的とする。

【解決手段】本発明の半導体装置は、半導体層上に設けられた、シリサイド膜からなるエミッタ電極7と、エミッタ電極7上に形成された絶縁膜10と、絶縁膜10上に形成されたAlからなる電極パッド8とを備える。

(もっと読む)

1 - 20 / 240

[ Back to top ]