Fターム[5F033GG02]の内容

半導体集積回路装置の内部配線 (234,551) | 基板材料(シリコンを除く) (2,930) | 化合物半導体 (913) | III−V族 (485)

Fターム[5F033GG02]に分類される特許

1 - 20 / 485

半導体装置

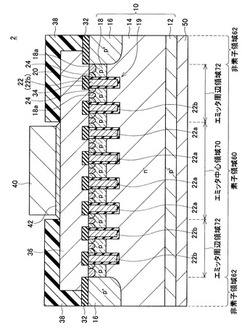

【課題】本明細書では、半導体装置が短絡状態で動作する場合における、半導体装置全体の短絡耐量を向上させることができる半導体装置を提供する。

【解決手段】本明細書が開示する半導体装置2は、素子領域60と、表面電極36と、熱伝導部材40と、保護膜38とを備える。素子領域60は、複数個のゲート電極22を備える。表面電極36は、素子領域60の表面に形成されている。熱伝導部材40は、表面電極36の中心部の表面側に形成され、素子領域60の熱伝導率よりも高い熱伝導率を有している。保護膜38は、表面電極36の表面側であって、中心部の周囲を取り囲む周辺部に形成されている。素子領域60は、表面電極36の中心部の裏面側に形成されるエミッタ中心領域70では、表面電極36の周辺部の裏面側に形成されるエミッタ周辺領域72と比較して、オン状態となる時間が長い。

(もっと読む)

半導体集積回路装置

【課題】チップあたりの端子数の増大に伴って、フリップチップ実装が種々の形態で実施されている。しかし、バンプピッチの微細化およびバンプの鉛フリー化によって、エレクトロマイグレーション耐性の確保がますます重要となっている。

【解決手段】本願の発明は、フリップチップ型の半導体集積回路装置において、チップの第1の主面上に形成された多数のUBMパッド状の各々に設けられた半田バンプの中間部には、上下を分割する前記半田バンプとは異なる材質の金属隔壁が設けられているものである。

(もっと読む)

パターン形成方法

【課題】微細なパターン、例えば、線幅が50μmよりも小さいパターンであっても高い精度でパターンを形成することができるパターン形成方法を提供する。

【解決手段】微細なパターンのパターン形成方法であって、基板上に形成された、親疎水性変換機能を有する第1の膜において、パターンが形成されるパターン形成領域を親疎水性に変化させる工程と、パターン形成領域に第2の膜を形成し、第2の膜が乾燥してパターンを形成する工程とを有する。第2の膜は、厚さが0.1μmになったときの粘度が3mPa・s以下である。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】断線等の問題を抑制しつつ逆メサの段差に配線を設けることができる半導体装置の製造方法を提供する。

【解決手段】エッチングにより半導体基板に逆メサ段差部を形成する。逆メサ段差部の下段における半導体基板の表面に、電極を設ける。逆メサ段差部内を埋めるように当該逆メサ段差部の高さよりも厚い絶縁膜を設ける。逆メサ段差部内に絶縁膜を残すように、絶縁膜積層工程で積層した絶縁膜に対してエッチバックを行う。電極に接続する配線を、逆メサ段差部に残された絶縁膜の上方に設ける。このとき、電極とのコンタクトをとる部分を対象にして、層間絶縁膜に対し開口を形成する。開口形成後、配線を、層間絶縁膜上であって逆メサ段差部の上方の領域に蒸着する。コンタクト開口を介して、配線が電極と接続する。

(もっと読む)

半導体装置

【課題】VIAホールを高密度に形成したとしても半導体素子が割れやすくなるのを防止し、素子の形成歩留りを向上させることができる半導体装置を提供する。

【解決手段】半導体装置は、基板110と、基板の第1表面に配置され、それぞれ複数のフィンガーを有するゲート電極124、ソース電極120およびドレイン電極122と、ソース電極120の下部に配置されたVIAホールSCと、基板の第1表面とは反対側の第2表面に配置され、VIAホールを介してソース電極に接続された接地電極とを備え、VIAホールSCは、基板110を形成する化合物半導体結晶のへき開方向とは異なる方向に沿って配置される。

(もっと読む)

半導体装置の製造方法

【課題】エピ抵抗や抵抗チップを用いることなく、奇モードのループ発振を抑えること。

【解決手段】本発明は、金属層60を形成する工程と、複数のFETそれぞれのゲートフィンガー14を共通に接続するゲートバスライン26のパターンのうち一部分を除いたパターンを有するめっき層64と、一部分の領域を被覆する第2マスク層66と、をマスクにして金属層60をパターニングすることで、ゲートバスライン26を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体層と電気的に接続するソース電極層及びドレイン電極層を、酸化物半導体層上のゲート絶縁層及び絶縁層の開口を埋め込むように設ける。ソース電極層を設けるための開口とドレイン電極層を設けるための開口は、それぞれ異なるマスクを用いた個別のエッチング処理によって形成される。これにより、ソース電極層(またはドレイン電極層)と酸化物半導体層が接する領域と、ゲート電極層との距離を十分に縮小することができる。また、酸化物半導体層の下に第1の電極層および第2の電極層を設けてコンタクト抵抗の低減を図る。

(もっと読む)

半導体装置及びその製造方法

【課題】外部からの不純物等に対する耐性を向上することができる半導体装置及びその製造方法を得る。

【解決手段】GaAs基板1上に下層配線2が設けられている。GaAs基板1及び下層配線2上に樹脂膜4が設けられている。樹脂膜4は、下層配線2上に開口5を有する。下層配線2及び樹脂膜4上にSiN膜6が設けられている。SiN膜6は、開口5内に開口7を有する。下層配線2及び樹脂膜4の一部上に上層配線8が設けられている。上層配線8は、開口5,7を介して下層配線2に接続されたTi膜8aと、Ti膜8a上に設けられたAu膜8bとを有する。上層配線8及び樹脂膜4上にSiN膜9が設けられている。SiN膜9は、樹脂膜4上においてSiN膜6に付着している。SiN膜6,9はTi膜8aの周囲を保護する。

(もっと読む)

半導体ウエハ、半導体ウエハ検査装置、及び半導体ウエハの検査方法

【課題】本発明は、半導体ウエハの検査において、半導体ウエハの裏面電極の端子としての機能を維持しつつ、半導体ウエハに過度の力がかかることを防止できる半導体ウエハ、半導体ウエハ検査装置、及び半導体ウエハの検査方法を提供することを目的とする。

【解決手段】本発明に係る半導体ウエハは、ダイシングラインを隔てて複数のチップが並ぶ半導体ウエハの表面側に形成された表面電極と、該半導体ウエハの裏面側に、該ダイシングラインを隔てて形成された複数の裏面電極と、該半導体ウエハの裏面側に、該ダイシングラインを跨いで該複数の裏面電極を電気的に接続する接続パターンと、を備える。該複数の裏面電極のうちの少なくともひとつは、該半導体ウエハのバイアホールを介して該表面電極と電気的に接続される。

(もっと読む)

半導体ウエハ及び半導体装置並びに半導体装置の製造方法

【課題】ダイシング工程におけるチッピング不良を低減させる。

【解決手段】一面側に複数の回路素子3が形成され、この回路素子が形成された領域間に第一スクライブライン領域R1が設けられたウエハ状の半導体基板2と、この半導体基板の他面2bから半導体基板の一面2aまで貫通する貫通孔7と、この貫通孔の内面及び半導体基板の他面側に形成された絶縁膜5と、この絶縁膜上に形成された配線6とを備えた半導体ウエハにおいて、半導体基板の他面側に形成された絶縁膜に、第一スクライブライン領域に沿って絶縁膜が離間した領域である第二スクライブライン領域R2が設けられている半導体ウエハを提供する。

(もっと読む)

有機シリケート材料からの炭素の除去方法

【課題】有機シリケート(OSG)膜内の炭素含有種の少なくとも一部分を除去すること。

【解決手段】本明細書中に記載されているのは、酸化剤等の、しかし酸化剤に限られない薬品を用いてOSG膜を処理する工程、OSG膜紫外線を含むエネルギー源に曝す工程、またはOSG膜を薬品で処理する工程およびOSG膜をエネルギー源に曝す工程により、有機シリケート(OSG)膜内の炭素含有種の少なくとも一部分を除去するための方法である。

(もっと読む)

3DIC方法および装置

【解決手段】 切り分けられたダイまたはウェハのような素子を3次元的に集積する方法および切り分けられたダイまたはウェハのような素子が接続された集積構造。ダイまたはウェハの一方または両方は、その中に形成された半導体デバイスを有する。第1コンタクト構造を有する第1素子は、第2コンタクト構造を有する第2素子に接着される。第1、第2コンタクト構造は、接着の際に露出されることが可能で、また接着の結果、電気的に接続される。接着後にビアがエッチングされるとともに埋め込まれて電気的配線を露出および形成して第1、第2コンタクト構造を接続するとともに、この電気的配線への表面からの電気的なアクセスが可能になる。または、第1、第2コンタクト構造は接着の際に露出されず、接着後にビアがエッチングおよび埋め込みされて第1、第2コンタクト構造が電気的に接続されるとともに接続された第1、第2コンタクト構造への電気的なアクセスが得られる。 (もっと読む)

電界効果トランジスタ

【課題】ゲート電極とソース電極との間に印加される電圧がソース電極パッドの電気抵抗による電圧降下で低下することを防止でき、安定した動作を実現できる電界効果トランジスタを提供する。

【解決手段】このGaN HFETによれば、ボンディング部16Bの第2のパッド部16B‐2は、電極接続部16Aが含有する複数の接続部分19のうちの第2の方向(ソース電極12とドレイン電極11が対向している方向)の一端に配置された接続部分19の上記第2の方向の外端を電極延在方向へ延長した仮想延長線L1に関して第1のパッド部16B‐1とは反対側に位置している。第2のパッド部16B‐2に接続された第2のソース配線24のボンディング箇所の第2の方向の位置を電極接続部16Aのソース電極12との接続部分19の第2の方向の位置と重ならないようにして、ソース電極12からの電流が第2のソース配線24に流れにくくできる。

(もっと読む)

半導体装置及びその製造方法

【課題】電極端部への電界集中を抑えるとともに、ゲート電極の変形や、ゲート−フィールドプレート間に生じる容量による特性劣化を抑える。

【解決手段】半導体装置において、第1の基板と、第1の基板表面に形成された素子領域と、素子領域と接続され、第1の基板上に形成されたゲート電極、ソース電極及びドレイン電極と、第1の基板と、第1の面で積層される第2の基板と、第2の基板を貫通し、電極上に配置されるビアホールと、ビアホール内に形成され、電極と接続される金属層と、第2の基板に設けられ、ゲート電極、ソース電極及びドレイン電極のいずれかと接続されるフィールドプレート電極と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】本願発明者らが、プラズマ処理等による半導体ウエハのチャージアップの影響を検討したところによると、半導体ウエハ等にドライエッチング等を施すと、通常、その結果として、半導体ウエハは、主に電気的に正側に偏った不均一な帯電状態となることが明らかとなった。これは、ドライエッチング等によって、正の可動イオン等がウエハの表面やその近傍に残存し、不均一に分布していることを示すものであり、個々の半導体チップとされた後も残存して、動作に悪影響を及ぼす恐れがある。

【解決手段】本願発明は、通常、ポリマー除去液等を使用する必要のないメタル膜加工工程に於いて、加工用レジスト膜の除去後、ポリマー除去液類似の導電性処理液との摩擦により、ウエハ全体を負に帯電させるものである。

(もっと読む)

窒化物半導体装置

【課題】ドレイン電極配線によって形成されるフィールドプレートに起因する電流コラプス現象への影響が抑制された窒化物半導体装置を提供する。

【解決手段】窒化物半導体からなる機能層20と、機能層20上に離間して配置されたソース電極3及びドレイン電極4と、ソース電極3とドレイン電極4間で機能層20上に配置されたゲート電極5と、機能層20上に配置された層間絶縁膜7と、層間絶縁膜7上に配置され、ドレイン電極4と電気的に接続されたドレイン電極配線41とを備える窒化物半導体装置であって、ゲート電極5とドレイン電極4間において、層間絶縁膜7を介してドレイン電極配線41が機能層20と対向する領域を有さない。

(もっと読む)

半導体発光素子

【課題】メタル電極に設けられた延伸部の表面を覆う絶縁膜の剥離が抑制された半導体素子を提供する。

【解決手段】半導体からなる活性層に積層されたn型またはp型の半導体層と、該半導体層の上に配置され接続部および延伸部を有するメタル電極と、該メタル電極の該延伸部の上面および側面を少なくとも覆う絶縁膜と、を備え、該延伸部はメタル多層膜で形成され、該メタル多層膜は少なくとも2層の第1メタル層と、該第1メタル層と交互に積層された第2メタル層とを含み、かつ、その最上層は該第2メタル層のひとつであり、該メタル多層膜に含まれる該最上層の第2メタル層以外の第2メタル層の各々の端面が該延伸部の側面に露出して該絶縁膜と接しており、該第2メタル層を構成する第2メタル材料は該第1メタル層を構成する第1メタル材料よりも導電率は低いが該第1メタル材料よりも該絶縁膜との密着強度に優れている。

(もっと読む)

表示装置

【課題】配線等のパターンを、材料の利用効率を向上させ、かつ、作製工程を簡略化して得られた表示装置である。また配線等のパターンを所望の形状で制御性よく形成された導電膜を有する表示装置である。

【解決手段】トランジスタ上の第1の導電膜と、第2の導電膜とは、複数の屈曲点を有するコの字状に設けられる。本形状であっても、第1の導電膜と、第2の導電膜とはパターンを所望の形状で制御性よく形成される。なお、第1の導電膜と第2の導電膜は、共通電極層と、画素電極層となることができる。

(もっと読む)

タングステン膜の成膜方法

【課題】工程が煩雑になることなく、埋め込み部分のボイドやシームを解消することができるタングステン膜の成膜方法を提供すること。

【解決手段】処理容器内において、ホールを有する基板にCVDによりタングステン膜を成膜してホール内にタングステンの埋め込み部を形成する工程と、同じ処理容器内にエッチングガスとしてClF3ガスまたはF2ガスを供給して埋め込み部の上部をエッチングし、開口を形成する工程と、開口が形成された埋め込み部を有する基板に対して同じ処理容器内において、CVDによりタングステン膜を成膜する工程とを有する。

(もっと読む)

半導体ダイ上にフィーチャをめっきするためのヒューズバス

【課題】半導体ダイ上に相互接続部又はボンドパッドなどのフィーチャ構造を電気めっきする方法を提供する。

【解決手段】方法は半導体基板の上方に複数のヒューズ(208)を形成する工程と、半導体基板の上方の複数の相互接続層(400〜408)と、該複数の相互接続層の上面の複数の相互接続パッド(502)とを形成する工程と、を含む。シールリング(202)が、半導体基板(302)と、前記複数の相互接続パッド(502)と、前記複数のヒューズ(208,320)とに形成された能動回路を包囲する。各ヒューズ(208,320)は、対応する相互接続パッド(502)とシールリング(202)とに電気的に接続される。各ヒューズ(208)が導通状態にあるとき、該ヒューズは対応する相互接続パッド(502)をシールリング(202)に電気的に接続する。

(もっと読む)

1 - 20 / 485

[ Back to top ]