Fターム[5F033GG03]の内容

半導体集積回路装置の内部配線 (234,551) | 基板材料(シリコンを除く) (2,930) | 絶縁性基板 (1,777)

Fターム[5F033GG03]の下位に属するFターム

透光性基板 (1,019)

Fターム[5F033GG03]に分類される特許

1 - 20 / 758

銅を含む電極連結構造体

半導体装置およびその製造方法

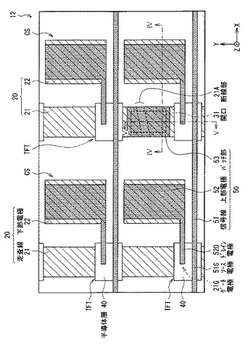

薄膜トランジスタアレイおよびその製造方法、並びに表示装置

【課題】配線密度を高くしすぎることなく断線を修復することが可能であり、フレキシブル性を持たせる場合に短絡や断線などを抑えることが可能な薄膜トランジスタアレイおよびその製造方法、並びに表示装置を提供する。

【解決手段】第1導電層と、前記第1導電層の少なくとも一部に対向して、前記第1導電層に合わせた平面形状の開口を有する絶縁膜と、前記開口を塞ぐと共に前記開口内で前記第1導電層に接するパッチ部を含む第2導電層とを備えた薄膜トランジスタアレイ。

(もっと読む)

配線の形成方法、電子素子、および表示装置

【課題】物理的な版を必要とせず、微細な導電パターンを形成でき、パターン変更に対して柔軟に対応できる配線の形成方法を提供する。

【解決手段】本発明では、基板上に、エネルギー付与によって臨界表面張力が変化する材料を含有する濡れ性変化層を形成する工程と、前記濡れ性変化層に選択的にレーザ光を照射して、前記濡れ性変化層の臨界表面張力が高くなるように変化させた高表面エネルギー領域部を前記濡れ性変化層に形成する工程と、前記高表面エネルギー領域部に導電性インクを塗布し、前記高表面エネルギー領域部上に配線を形成する工程と、を有し、前記濡れ性変化層と前記高表面エネルギー領域部とには段差がなく、前記配線は前記高表面エネルギー領域部上に形成されていることを特徴とする配線の形成方法が提供される。

(もっと読む)

半導体集積回路装置

【課題】チップあたりの端子数の増大に伴って、フリップチップ実装が種々の形態で実施されている。しかし、バンプピッチの微細化およびバンプの鉛フリー化によって、エレクトロマイグレーション耐性の確保がますます重要となっている。

【解決手段】本願の発明は、フリップチップ型の半導体集積回路装置において、チップの第1の主面上に形成された多数のUBMパッド状の各々に設けられた半田バンプの中間部には、上下を分割する前記半田バンプとは異なる材質の金属隔壁が設けられているものである。

(もっと読む)

半導体装置の製造方法

【課題】電界効果トランジスタを有する半導体装置のトランジスタ性能を向上させることのできる技術を提供する。

【解決手段】ゲート絶縁膜5およびゲート電極6n,6pの側面にサイドウォール9を形成した後、サイドウォール9の両側の半導体基板1に不純物をイオン注入して不純物領域を形成する。続いて、半導体基板1の主面上に第1絶縁膜14、第2絶縁膜15、および第3絶縁膜16を順次形成した後、イオン注入された上記不純物を活性化する熱処理を行う。ここで、第1絶縁膜14は、第2絶縁膜15よりも被覆性のよい膜であり、かつ、第2絶縁膜15とエッチング選択比が異なる膜である。第2絶縁膜15は、第1絶縁膜14よりも水素の拡散を阻止する機能が高い膜である。第3絶縁膜16は、第1絶縁膜14および第2絶縁膜15よりも内部応力の変化が大きい膜である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性の向上を図る。

【解決手段】本発明の半導体装置は、(a)素子分離領域STIにより囲まれた半導体領域3よりなる活性領域Acに配置されたMISFETと、(b)活性領域Acの下部に配置された絶縁層BOXとを有する。さらに、(c)活性領域Acの下部において、絶縁層BOXを介して配置されたp型の半導体領域1Wと、(d)p型の半導体領域1Wの下部に配置されたp型と逆導電型であるn型の第2半導体領域2Wと、を有する。そして、p型の半導体領域1Wは、絶縁層BOXの下部から延在する接続領域CAを有し、p型の半導体領域1Wと、MISFETのゲート電極Gとは、ゲート電極Gの上部から接続領域CAの上部まで延在する一体の導電性膜であるシェアードプラグSP1により接続されている。

(もっと読む)

型押し構造体の製造方法、薄膜トランジスター、薄膜キャパシター、アクチュエーター、圧電式インクジェットヘッド及び光学デバイス

【課題】従来よりも大幅に少ない原材料及び製造エネルギーを用いて、かつ、従来よりも短工程で製造することが可能な機能性デバイスの製造方法を提供する。

【解決手段】熱処理することにより金属酸化物又は金属となる液体材料を準備する第1工程と、基材上に液体材料を塗布することにより金属酸化物又は金属の前駆体組成物からなる前駆体組成物層を形成する第2工程と、前駆体組成物層に対して凹凸型を用いて型押し加工を施すことにより前駆体組成物層に残膜を含む型押し構造を形成する第3工程と、型押し構造が形成された前駆体組成物層に対して大気圧プラズマ又は減圧プラズマによるアッシング処理を施すことにより残膜を処理する第4工程と、前駆体組成物層を熱処理することにより、前駆体組成物層から金属酸化物又は金属からなる型押し構造体を形成する第5工程とをこの順序で含む型押し構造体の製造方法。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置において誤動作が生じる蓋然性を低減する。

【解決手段】積層配置されるメモリセルアレイ(例えば、酸化物半導体材料を用いて構成されているトランジスタを含むメモリセルアレイ)と周辺回路(例えば、半導体基板を用いて構成されているトランジスタを含む周辺回路)の間に遮蔽層を配置する。これにより、当該メモリセルアレイと当該周辺回路の間に生じる放射ノイズを遮蔽することが可能となる。よって、半導体記憶装置において誤動作が生じる蓋然性を低減することが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】隣接するSOI領域とバルクシリコン領域とが短絡することを防止する。

【解決手段】一つの活性領域内にSOI領域およびバルクシリコン領域が隣接する半導体装置において、それぞれの領域の境界にダミーゲート電極8を形成することにより、BOX膜4上のSOI膜5の端部のひさし状の部分の下部の窪みにポリシリコン膜などの残渣が残ることを防ぐ。また、前記ダミーゲート電極8を形成することにより、それぞれの領域に形成されたシリサイド層14同士が接触することを防ぐ。

(もっと読む)

配線構造及びその製造方法

【課題】配線間の絶縁性に優れ信頼性の高い配線構造及びその製造方法を提供する。

【解決手段】スピンコート法により、ベースポリマーがポリイミド樹脂である非感光性樹脂のワニスを塗布後、ベーク、キュアしてポリイミド樹脂を硬化、膜を形成する。これを第1絶縁膜12とする。次いで、めっきシード層18形成、フォトレジスト溝パターン22形成、めっき、フォトレジスト溝パターン22除去、配線下以外のめっきシード層18除去に依り、第1の絶縁膜上に配線26を形成する。そして、第1絶縁膜の表面上にシリカ粒子30を分散し、散したシリカ粒子30をマスクとして、CF4及びO2を混合したガスで、第1絶縁膜12をドライエッチングすることに依り、段差が100nm以上の凹凸32を形成する。最後に前述と同様にして、スピンコート法により、第2絶縁膜としてのポリイミド樹脂膜34を形成する。

(もっと読む)

パターン構造体の製造方法

【課題】基材上にパターンを低温かつ低コストで形成することができると共に、リフトオフを容易にできるパターン構造体の製造方法を提供する。

【解決手段】実施形態に係るパターン構造体の製造方法では、基材10上に、インクジェット法によりリフトオフ材12を形成する。次に、基材10及びリフトオフ材12上に、原子層堆積法により機能膜14を形成する。次に、リフトオフ法によりリフトオフ材12を除去することによって、基材10上に、機能膜14からパターン14aを形成する。リフトオフ材12は、樹脂と溶媒とを含むインクを基材10上に塗布した後、溶媒を除去することによって形成される。溶媒は、樹脂に対する第1溶解性を有する第1溶媒と、第1溶解性よりも低い第2溶解性を有する第2溶媒とを含む。第1溶媒は第2溶媒に相溶する。

(もっと読む)

ウェハ裏面のキャパシタを有する半導体デバイスを形成する方法

【課題】 ウェハ裏面のキャパシタを有する半導体デバイスの形成方法を提供する。

【解決手段】 本発明の方法は、その前面の活性シリコン層とその裏面のバルク・シリコン層との間に挿入された埋込み絶縁層を有する、SOI基板を準備するステップと、SOI基板の前面から埋込み絶縁層を貫通して延びる埋込みコンタクト・プラグを含む集積回路を、SOI基板の前記前面に形成するステップと、裏面エッチング・プロセスを実施してバルク・シリコン層内にトレンチを形成し、埋込みコンタクト・プラグの端部を埋込み絶縁層の裏表面に露出させるステップと、第1キャパシタ・プレートと、第2キャパシタ・プレートと、該第1及び第2キャパシタ・プレートの間に挿入されたキャパシタ誘電体層とを含むキャパシタをトレンチ内に形成するステップとを含み、第1キャパシタ・プレートは、埋込みコンタクト・プラグの露出した端部に接触するように形成される。

(もっと読む)

半導体装置

【課題】無線通信により交信可能な半導体装置において、個体識別子を容易に付けることができるようにする。また信頼性の高い半導体装置を提供する。

【解決手段】チャネル形成領域と、ソース領域またはドレイン領域を有する島状半導体膜131と、ゲート絶縁膜と、ゲート電極103とを有する薄膜トランジスタと、層間絶縁膜と、層間絶縁膜中に形成され、ソース領域またはドレイン領域の一方に達する複数のコンタクトホールを含む第1のコンタクトホール142と、ソース領域またはドレイン領域の他方に達する第2のコンタクトホール141とを有し、第2のコンタクトホール141の径は、第1のコンタクトホール142に含まれる複数のコンタクトホール142のそれぞれの径より大きく、第1のコンタクトホールの底面積の合計と、第2のコンタクトホール141の底面積は等しい半導体装置に関する。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】微細な溝部の内部に隙間無く導電材料を埋め込み、導電性に優れた配線を得ることが可能な半導体装置の製造方法および半導体装置を提供する。

【解決手段】中間層の形成時に、第2コイル46および第3コイル61によってターゲット53と基体11との間に磁力線M1が通るように磁場を発生させることによって、溝部12の内壁面に均一な厚みで中間層を成膜することが可能になる。

(もっと読む)

半導体装置の製造方法

【課題】スルーホールの底部における突起の形成を防止して、半導体装置の品質を安定させる手段を提供する。

【解決手段】配線層5と、該配線層上に形成された金属窒化膜8とを覆う層間絶縁膜9とを形成した半導体ウェハに、層間絶縁膜を貫通し金属窒化膜に達するスルーホール10を形成する工程を備えた半導体装置の製造方法において、スルーホールを形成する工程は、層間絶縁膜上に、レジストマスク18を形成する工程と、半導体ウェハを第1の温度とし、異方性エッチングにより層間絶縁膜をエッチングする第1のエッチング工程と、半導体ウェハを、第1の温度より高い第2の温度とし、レジストマスクをそのまま用いて、異方性エッチングにより金属窒化膜の上表面をエッチングする第2のエッチング工程と、レジストマスクを除去する工程と、を備え、第1のエッチング工程と、第2のエッチング工程で用いるエッチングガスとを同一とする。

(もっと読む)

トップゲート型アクティブマトリックス基板、およびその製造方法

【課題】データ配線が銀や銀合金により形成されており、またデータ配線に、ゲート絶縁層によって被覆されておらずむき出しとなっている部分があった場合でも、当該むき出しとなっている部分でマイグレーション現象が生じることがないトップゲート型アクティブマトリックスを提供する。

【解決手段】基材と、前記基材上に直接または間接的に形成された、ソース電極、ドレイン電極、半導体層、ゲート絶縁層、ゲート電極、層間絶縁層、画素電極、および前記ソース電極と接続したデータ配線と、を有するトップゲート型アクティブマトリックス基板において、前記ソース電極と前記データ配線をともに銀または銀合金で形成し、前記ゲート電極を銀または銀合金以外で形成し、前記データ配線においてむき出しとなっている部分をゲート電極と同じ材質からなる被覆層によって被覆する。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】微細な溝部の内部に隙間無く導電材料を埋め込み、導電性に優れた配線を得ることが可能な半導体装置の製造方法および半導体装置を提供する。

【解決手段】溝部12を除いた基体11の一面11a、即ち溝部12の頂面にエッチングカバー層14を形成する。エッチングカバー層14は、例えば、Ta,Tiまたはこれらを含む合金から構成される。エッチングカバー層14の形成は、例えば、スパッタリング法を用いることが好ましい。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】微細な溝部の内部に隙間無く導電材料を埋め込み、導電性に優れた配線を得ることが可能な半導体装置の製造方法および半導体装置を提供する。

【解決手段】バリア層(バリアメタル)13を覆うようにライナー層14が形成されている。ライナー層14は、Ni(ニッケル)から構成される。ライナー層14は、このライナー層14の内側に形成されるCu(銅)からなる導電体15に対する濡れ性を高め、かつ、溝部12の内側の平滑性を高める。

(もっと読む)

膜の形成方法および形成装置

【課題】プラスチック基板上に塗布印刷を用いて所望の特性を有する膜を形成することができる膜の形成方法および形成装置を提供する。

【解決手段】プラスチック基板上に塗布組成物を塗布した塗布膜からなるパターンが形成された部材を作製する工程1、部材に超音波を照射して塗布膜の乾燥および/または改質を行う工程2を備え、溶液状態の塗布膜に化学作用を及ぼして、デバイスに用いられる配線膜、電極膜、絶縁膜などの所定の膜を形成する。

(もっと読む)

1 - 20 / 758

[ Back to top ]