Fターム[5F033HH17]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 金属及びその合金(シリサイドを除く) (23,853) | 高融点金属 (8,733)

Fターム[5F033HH17]の下位に属するFターム

Fターム[5F033HH17]に分類される特許

1 - 20 / 962

Cu層形成方法及び半導体装置の製造方法

薄膜トランジスタアレイおよびその製造方法、並びに表示装置

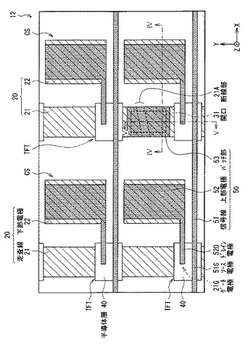

【課題】配線密度を高くしすぎることなく断線を修復することが可能であり、フレキシブル性を持たせる場合に短絡や断線などを抑えることが可能な薄膜トランジスタアレイおよびその製造方法、並びに表示装置を提供する。

【解決手段】第1導電層と、前記第1導電層の少なくとも一部に対向して、前記第1導電層に合わせた平面形状の開口を有する絶縁膜と、前記開口を塞ぐと共に前記開口内で前記第1導電層に接するパッチ部を含む第2導電層とを備えた薄膜トランジスタアレイ。

(もっと読む)

半導体装置およびその製造方法ならびに表示装置および電子機器

【課題】配線層の膜応力を低減し、製造歩留まりを向上することが可能な半導体装置およびその製造方法並びに表示装置および電子機器を提供する。

【解決手段】本技術の半導体装置は、一方向に延在する複数の第1配線層と、第1配線層の間に設けられた第1配線層よりも膜厚が薄いゲート電極と、第1配線層およびゲート電極上に形成された絶縁膜と、絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層と、半導体層上に設けられた層間膜と、層間膜上に形成されると共に、層間膜に設けられた貫通孔を介して半導体層と接続された第2配線層とを備えている。

(もっと読む)

半導体集積回路装置

【課題】チップあたりの端子数の増大に伴って、フリップチップ実装が種々の形態で実施されている。しかし、バンプピッチの微細化およびバンプの鉛フリー化によって、エレクトロマイグレーション耐性の確保がますます重要となっている。

【解決手段】本願の発明は、フリップチップ型の半導体集積回路装置において、チップの第1の主面上に形成された多数のUBMパッド状の各々に設けられた半田バンプの中間部には、上下を分割する前記半田バンプとは異なる材質の金属隔壁が設けられているものである。

(もっと読む)

パターン形成方法

【課題】微細なパターン、例えば、線幅が50μmよりも小さいパターンであっても高い精度でパターンを形成することができるパターン形成方法を提供する。

【解決手段】微細なパターンのパターン形成方法であって、基板上に形成された、親疎水性変換機能を有する第1の膜において、パターンが形成されるパターン形成領域を親疎水性に変化させる工程と、パターン形成領域に第2の膜を形成し、第2の膜が乾燥してパターンを形成する工程とを有する。第2の膜は、厚さが0.1μmになったときの粘度が3mPa・s以下である。

(もっと読む)

半導体装置の製造方法及び半導体装置、電子機器

【課題】空洞部の破壊を防ぐと共に、基板間の接続の信頼性を向上できるようにした半導体装置の製造方法及び半導体装置、電子機器を提供する。

【解決手段】第1の基板は、第1の面と第2の面とを有する第1の基材と、第1の基材の第1の面側に設けられた犠牲層と、第1の基材の第1の面と第2の面との間を貫通する貫通電極と、貫通電極と第1の基材との間に設けられた絶縁膜と、を有する。第2の基板は、第3の面を有する第2の基材と、第2の基材の第3の面側に設けられたバンプと、第2の基材の第3の面側に設けられ、バンプを囲む環状導電部と、を有する。第2の面と第3の面とを対向させた状態で、貫通電極とバンプとを接続すると共に、第1の基板の周縁部を環状導電部に埋入させる実装工程と、実装工程の後で、犠牲層をエッチングして第1の基材の第1の面側に空洞部を形成するエッチング工程と、を含む。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法

【課題】大型化に適した薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法を提供する。

【解決手段】フレキシブルな樹脂基板60に形成された薄膜トランジスタ200であって、周面の一部又は全部が導電性材料20により覆われたワイヤー10と、前記導電性材料を覆う絶縁膜30と、該絶縁膜を介して前記導電性材料上に形成された薄膜半導体40と、が一体的に構成されたゲート・チャネル一体形成部50を有し、該ゲート・チャネル一体形成部が前記樹脂基板の表面上又は内部の所定位置に設けられ、前記薄膜半導体の両側に第1及び第2の電極70、80が接続されて形成されたことを特徴とする。

(もっと読む)

パターン構造体の製造方法

【課題】基材上にパターンを低温かつ低コストで形成することができると共に、リフトオフを容易にできるパターン構造体の製造方法を提供する。

【解決手段】実施形態に係るパターン構造体の製造方法では、基材10上に、インクジェット法によりリフトオフ材12を形成する。次に、基材10及びリフトオフ材12上に、原子層堆積法により機能膜14を形成する。次に、リフトオフ法によりリフトオフ材12を除去することによって、基材10上に、機能膜14からパターン14aを形成する。リフトオフ材12は、樹脂と溶媒とを含むインクを基材10上に塗布した後、溶媒を除去することによって形成される。溶媒は、樹脂に対する第1溶解性を有する第1溶媒と、第1溶解性よりも低い第2溶解性を有する第2溶媒とを含む。第1溶媒は第2溶媒に相溶する。

(もっと読む)

配線構造およびその製造方法

【課題】複雑な配線構造であっても、電極パターン同士を簡単な構造で接続できると共に、配線パターンの強度をも確保できるような配線構造、およびこうした配線構造を製造するための有用な方法を提供する。

【解決手段】本発明の配線構造は、基板上に形成された少なくとも第1の配線パターンと第2の配線パターンを有する配線構造であって、前記第1の配線パターンと第2の配線パターンとの間は、金属ワイヤーによる空中配線部によって接続されると共に、少なくとも金属ワイヤー表面には、金属ワイヤーと同じ若しくは異なる素材からなる金属めっきが施されたものである。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】微細な溝部の内部に隙間無く導電材料を埋め込み、導電性に優れた配線を得ることが可能な半導体装置の製造方法および半導体装置を提供する。

【解決手段】溝部12を除いた基体11の一面11a、即ち溝部12の頂面にエッチングカバー層14を形成する。エッチングカバー層14は、例えば、Ta,Tiまたはこれらを含む合金から構成される。エッチングカバー層14の形成は、例えば、スパッタリング法を用いることが好ましい。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】微細な溝部の内部に隙間無く導電材料を埋め込み、導電性に優れた配線を得ることが可能な半導体装置の製造方法および半導体装置を提供する。

【解決手段】バリア層(バリアメタル)13を覆うようにライナー層14が形成されている。ライナー層14は、Ni(ニッケル)から構成される。ライナー層14は、このライナー層14の内側に形成されるCu(銅)からなる導電体15に対する濡れ性を高め、かつ、溝部12の内側の平滑性を高める。

(もっと読む)

半導体磁気記憶装置

【課題】磁気記憶素子を構成する層を、周辺回路部内で有効に活用する。

【解決手段】実施形態によれば、半導体磁気記憶装置は、セルトランジスタを含むセル部と、周辺トランジスタを含む周辺回路部とが形成された半導体基板を備える。さらに、前記装置は、前記セル部内に配置され、下部電極と、前記下部電極上に形成された電極間層と、前記電極間層上に形成された上部電極とを含む磁気記憶素子を備える。さらに、前記装置は、前記周辺回路部内に配置され、前記下部電極を形成している第1の層と、前記電極間層を形成している第2の層と、前記上部電極を形成している第3の層とを含む構造体を備える。さらに、前記装置は、前記第1の層に電気的に接続された第1及び第2のプラグを備える。さらに、前記第1の層は、前記第1のプラグと前記第2のプラグを電気的に接続する配線として機能する。

(もっと読む)

半導体装置の製造方法

【課題】貫通電極を有する半導体装置の製造方法において、埋設導電部間のショートが起き難くすること。

【解決手段】半導体素子を有する素子領域と貫通電極が形成される貫通電極領域とを有する基板の上に第1絶縁膜を形成し、前記素子領域上の前記第1絶縁膜に凹部を形成し、前記貫通電極領域上の前記第1絶縁膜にダミー凹部を形成し、前記第1絶縁膜上、前記凹部内、および前記ダミー凹部内に第1導電材を形成し、前記第1導電材および前記第1絶縁膜の上部を研磨して、前記凹部内に導電部を形成すると共に前記ダミー凹部内にダミー導電部を形成し、前記貫通電極領域上の前記第1絶縁膜および前記貫通電極領域をエッチングして前記基板内に至る貫通電極ホールを形成した後、前記貫通電極ホール内に第2導電材を形成し、前記貫通電極ホール内に形成された第2導電材が露出するまで前記基板の裏面を研磨して、前記貫通電極を形成すること。

(もっと読む)

半導体装置の製造方法

【課題】切削又は研削加工を用いつつ、低コストで金属電極を形成することができる半導体装置の製造方法を提供する。

【解決手段】半導体基板12の主面12aに下地電極14を形成する工程と、下地電極を覆う保護膜16を形成するとともに、該保護膜に下地電極を露出させる開口部16aを形成する工程と、保護膜及び開口部から臨む下地電極の表面を覆うように第1金属膜22を形成する工程と、第1金属膜が形成された半導体基板を、裏面12bを搭載面として吸着ステージ30に吸着固定した状態で、吸着ステージと平行に設定された基準面上P1に位置する保護膜の部分及び第1金属膜の部分を、切削により除去して、第1金属膜をパターニングする工程と、パターニング工程後、裏面から半導体基板を研削し、半導体基板の厚さを所定厚さまで薄くする工程とを備える。

(もっと読む)

半導体装置

【課題】酸化物半導体層を用いた表示装置に代表される半導体装置において、画面サイズの大型化や高精細化に対応し、表示品質が良く、安定して動作する信頼性のよい半導体装置を提供する。

【解決手段】引き回し距離の長い配線にCuを含む導電層を用いることで、配線抵抗の増大を抑える。また、Cuを含む導電層を、TFTのチャネル領域が形成される酸化物半導体層と重ならないようにし、窒化珪素を含む絶縁層で包むことで、Cuの拡散を防ぐことができ、信頼性の良い半導体装置を作製することができる。特に、半導体装置の一態様である表示装置を大型化または高精細化しても、表示品質が良く、安定して動作させること

ができる。

(もっと読む)

貫通配線の検査方法、貫通配線基板の製造方法

【課題】1つの貫通配線のみの抵抗を測定できる貫通配線の検査方法、及び該貫通配線の検査方法を行う工程を含む貫通配線基板の製造方法の提供。

【解決手段】基板1の一方の面1aに配された導電部2と、基板1を貫通し、導電部2と接続される第一貫通配線3、第二貫通配線4および第三貫通配線5とを少なくとも備えた貫通配線基板10を用い、基板1の他方の面1b側から第一貫通配線3及び第二貫通配線4に、定電流源6の一組の端子6a,6bを電気的に接続して、第一貫通配線3、導電部2、第二貫通配線4の経路に電流を流すと同時に、基板1の他方の面1b側から第一貫通配線3及び第三貫通配線5に、電圧計7の一組の端子7a,7bを電気的に接続して、第一貫通配線3における電圧降下を測定することを特徴とする貫通配線の検査方法。

(もっと読む)

半導体装置

【課題】層間絶縁膜のエッチングの際に半導体層がエッチングされることによるコンタク

ト抵抗の増大を防ぎ、書き込み特性及び電荷保持特性に優れた不揮発性半導体記憶装置及

びその作製方法を提供する。

【解決手段】ソース領域又はドレイン領域とソース配線又はドレイン配線との間に導電層

を設ける。また、該導電層は、制御ゲート電極を形成する導電層と同じ導電層からなる。

また、該導電層を覆うように絶縁膜が設けられており、該絶縁膜は該導電層の一部が露出

するコンタクトホールを有する。また、該ソース配線又はドレイン配線は、該コンタクト

ホールを埋めるように形成されている。

(もっと読む)

貫通配線基板および貫通配線基板の製造方法

【課題】貫通孔内に形成された導電層に加わる応力を抑制できるとともに、導電層からの効果的な放熱も促すことができる貫通配線基板、及びこの貫通配線基板の製造方法を提供する。

【解決手段】半導体基板11(基板)の一方の面11aに配された電極層12と、電極層12の少なくとも一部が露呈するように半導体基板11内に開けられた貫通孔20と、貫通孔20の内側面20aを覆い、電極層12の少なくとも一部が露呈するように配された第一絶縁層15と、第一絶縁層15を介して、貫通孔20の内側面20a及び電極層12の露呈部を覆うように配され、電極層12と電気的に接続された導電層5と、導電層5を覆うように配された第二絶縁層16と、を少なくとも備えてなる貫通配線基板10であって、第二絶縁層16は、導電層5の表面形状に沿って形成されていることを特徴とする。

(もっと読む)

銅膜作製方法

【課題】下地層との密着性に優れた銅膜を製造する方法の提供。

【解決手段】成膜対象物上に下地層としてチタン膜を形成した後、この下地層を水素ガス雰囲気中で100℃以上200℃未満の温度で熱処理し、次いでその上に銅膜を作製する。このように銅膜を作製した後、さらに水素ガス雰囲気中で100℃以上200℃未満の温度で熱処理を行う。

(もっと読む)

集積回路装置の作製方法

【課題】薄膜回路の下方に外部と接続するための電極を容易に形成できる薄膜回路部品の

構造及び薄膜回路部品の作製方法を提供することを課題とする。

【解決手段】第1の絶縁膜と、第1の絶縁膜の一方の面上に形成された薄膜回路と、薄膜

回路上に形成された第2の絶縁膜と、第2の絶縁膜上に形成された電極と、電極上に形成

された樹脂膜とを有する積層物を形成し、積層物の第1の絶縁膜の他方の面側に、電極と

重なるように導電膜を形成し、導電膜にレーザーを照射する。

(もっと読む)

1 - 20 / 962

[ Back to top ]