Fターム[5F033HH25]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | シリサイド (1,618)

Fターム[5F033HH25]の下位に属するFターム

高融点金属のシリサイド (1,006)

Fターム[5F033HH25]に分類される特許

1 - 20 / 612

半導体装置およびその製造方法

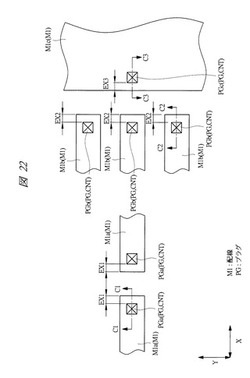

半導体装置の設計方法、半導体装置の製造方法および半導体装置

【課題】半導体装置の性能を向上させる。

【解決手段】半導体装置の設計フローは、プラグPGに接続された配線M1を含むチップレイアウトを設計するステップと、設計されたチップレイアウトにおけるプラグPGに対する配線M1のマージンを、プラグPGに対する配線M1のリセス量に応じて修正するステップとを有している。この修正ステップは、テストウエハに試験用プラグとそれに3次元的に接続された試験用配線とを含むテストパターンを形成するサブステップと、試験用配線の配線幅および配線密度と試験用プラグに対する試験用配線のリセス量との相関を調べるサブステップを有している。更に、得られた相関に基づいてプラグPGに対する配線M1のリセス量を予測するサブステップと、予測されたリセス量に応じてプラグPGに対する配線M1のマージンを修正するサブステップを有している。

(もっと読む)

半導体装置およびその製造方法

【課題】配線倒れを防止することが可能な半導体装置の製造方法を提供する。

【解決手段】一の実施形態による半導体装置の製造方法では、半導体基板上に、第1の絶縁膜、第2の絶縁膜、および犠牲膜を順に形成し、前記犠牲膜と前記第2の絶縁膜から複数の芯材を形成する。さらに、前記方法では、各々の前記芯材の側面に、前記芯材に接する第1側面と、前記第1側面の反対側に位置する第2側面とを有する第1配線と、前記芯材に接する第3側面と、前記第3側面の反対側に位置する第4側面とを有する第2配線を形成する。さらに、前記方法では、前記第1および第2配線の形成後に、前記第2の絶縁膜が残存するように前記犠牲膜を除去する。

(もっと読む)

半導体装置の製造方法

【課題】電界効果トランジスタを有する半導体装置のトランジスタ性能を向上させることのできる技術を提供する。

【解決手段】ゲート絶縁膜5およびゲート電極6n,6pの側面にサイドウォール9を形成した後、サイドウォール9の両側の半導体基板1に不純物をイオン注入して不純物領域を形成する。続いて、半導体基板1の主面上に第1絶縁膜14、第2絶縁膜15、および第3絶縁膜16を順次形成した後、イオン注入された上記不純物を活性化する熱処理を行う。ここで、第1絶縁膜14は、第2絶縁膜15よりも被覆性のよい膜であり、かつ、第2絶縁膜15とエッチング選択比が異なる膜である。第2絶縁膜15は、第1絶縁膜14よりも水素の拡散を阻止する機能が高い膜である。第3絶縁膜16は、第1絶縁膜14および第2絶縁膜15よりも内部応力の変化が大きい膜である。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細化されたトランジスタのオン特性を向上させる。微細化されたトランジスタを歩留まりよく作製する。

【解決手段】一対の低抵抗領域及び該低抵抗領域に挟まれるチャネル形成領域を含む酸化物半導体層と、ゲート絶縁層を介してチャネル形成領域と重畳する第1のゲート電極層と、第1のゲート電極層のチャネル長方向の側面及びゲート絶縁層の上面と接し、一対の低抵抗領域と重畳する一対の第2のゲート電極層と、第2のゲート電極層上の、側端部を第2のゲート電極層の側端部と重畳する一対の側壁絶縁層と、を有する半導体装置を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】個別の工程で形成されることで分離して配置された電極どうしを断線することなく接続できる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板の主面に第1の絶縁膜を介して形成された第1の電極と、半導体基板の主面に第2の絶縁膜を介して形成された第2の電極との間に補償膜を埋設する。第1の電極及び第2の電極上には、第1の電極の上面及び第2の電極の上面と接触する、第1の電極の上面から補償膜の上面を経由して第2の電極の上面まで到達する配線を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通ビアを用いた実装における端子間のショートや実装精度の低下を防止する。

【解決手段】半導体チップ88の貫通ビア86の上に、他の半導体チップ101を実装する。半導体チップ101のバンプ103は、4つの貫通ビア86で囲まれた領域に導かれて接合される。各貫通ビア86は、バンプ103に面する側面及び上面の保護膜31がエッチングによって除去されており、バンプ103のハンダ材料への濡れ性が保護膜31で覆われた領域よりも良好になっている。このために、ハンダ材料のはみ出しによる他の電極との間のショートが防止される。さらに、1つのバンプ103に複数の貫通ビア86からなる接続端子を配置するので、バンプ103に確実に接合できる。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体層と電気的に接続するソース電極層及びドレイン電極層を、酸化物半導体層上のゲート絶縁層及び絶縁層の開口を埋め込むように設ける。ソース電極層を設けるための開口とドレイン電極層を設けるための開口は、それぞれ異なるマスクを用いた個別のエッチング処理によって形成される。これにより、ソース電極層(またはドレイン電極層)と酸化物半導体層が接する領域と、ゲート電極層との距離を十分に縮小することができる。また、酸化物半導体層の下に第1の電極層および第2の電極層を設けてコンタクト抵抗の低減を図る。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体を含み、高速動作が可能なトランジスタを提供する。または、該トランジスタを含む信頼性の高い半導体装置を提供する。

【解決手段】下地絶縁層の溝に埋め込まれた電極層上に、一対の低抵抗領域及びチャネル形成領域を含む酸化物半導体層を設ける。チャネル形成領域は、サイドウォールを側壁に有するゲート電極層と重なる位置に形成される。溝は、深い領域と浅い領域を有し、サイドウォールは、浅い領域と重なり、配線との接続は、深い領域と重なる。

(もっと読む)

半導体装置

【課題】無線通信により交信可能な半導体装置において、個体識別子を容易に付けることができるようにする。また信頼性の高い半導体装置を提供する。

【解決手段】チャネル形成領域と、ソース領域またはドレイン領域を有する島状半導体膜131と、ゲート絶縁膜と、ゲート電極103とを有する薄膜トランジスタと、層間絶縁膜と、層間絶縁膜中に形成され、ソース領域またはドレイン領域の一方に達する複数のコンタクトホールを含む第1のコンタクトホール142と、ソース領域またはドレイン領域の他方に達する第2のコンタクトホール141とを有し、第2のコンタクトホール141の径は、第1のコンタクトホール142に含まれる複数のコンタクトホール142のそれぞれの径より大きく、第1のコンタクトホールの底面積の合計と、第2のコンタクトホール141の底面積は等しい半導体装置に関する。

(もっと読む)

半導体装置

【課題】微細化が可能な半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、上面に、一方向に延び上方に突出した複数本のアクティブエリアが形成された半導体基板と、前記アクティブエリア間のトレンチの下部に埋め込まれた素子分離絶縁体と、第1の絶縁材料からなり、前記素子分離絶縁体の直上域に配置され、下部が前記トレンチ内に配置され、上部が前記アクティブエリアの上端よりも上方に突出した絶縁ブロックと、前記第1の絶縁材料とは異なる第2の絶縁材料からなり、前記半導体基板及び前記絶縁ブロックの上方に設けられた層間絶縁膜と、前記層間絶縁膜内に形成され、下端が前記アクティブエリアの上面に接続されたコンタクトと、を備える。前記コンタクトにおける前記絶縁ブロックの直上域に位置する部分の下面は、前記コンタクトにおける前記アクティブエリアの直上域に位置する部分の下面よりも上方に位置している。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセル積層構造間に空隙を有する不揮発性半導体記憶装置において、隣接するメモリセル積層構造間、及び、メモリセル積層構造−選択ゲート積層構造間のショートを防ぐことができる不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、シリコン基板上にゲート絶縁膜、浮遊ゲート電極、電極間絶縁膜および制御ゲート電極が順に積層されたメモリセル積層構造が複数隣接して配置され、隣接する前記メモリセル積層構造間に空隙を有する不揮発性半導体記憶装置であって、前記メモリセル積層構造間のシリコン基板上に、前記メモリセル積層構造の側壁に形成されたシリコン酸化膜より厚いシリコン酸化膜が形成されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】隣接する配線の間におけるリークを抑制することができる不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置1は、シリコンを含む基板11と、基板11の上に設けられた複数のメモリセルと、複数のメモリセルの上方に設けられた配線7と、配線7の上に設けられたリーク抑制層8と、前記リーク抑制層8の上方に設けられた層間絶縁膜10と、を備えている。そして、隣接するメモリセルの間、および、隣接する配線7の間には空隙12が形成され、リーク抑制層8の幅寸法は、配線7の幅寸法よりも短いこと、および、隣接するリーク抑制層8の間の寸法は、隣接する配線7の間の寸法よりも長いこと、の少なくともいずれかである。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】ワード線抵抗を低減し、かつ、周辺回路のトランジスタの特性変化を抑制することができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板と、複数のメモリセルと、周辺回路とを備える。メモリセルは、半導体基板の上方に設けられたフローティングゲートと、フローティングゲート上に設けられたゲート間絶縁膜と、ゲート間絶縁膜上に設けられたコントロールゲートとを含む。周辺回路は、互いに電気的に接続されたフローティングゲートおよびコントロールゲートと、少なくともフローティングゲートとコントロールゲートとの間の電気的接触部分に設けられ該フローティングゲートと該コントロールゲートとの間の電気的接続を妨げない絶縁薄膜とを含むトランジスタを含む。複数のメモリセルは、コントロールゲート内に絶縁薄膜を含まない。メモリセルおよび周辺回路において、コントロールゲートの少なくとも上部はシリサイド化されている。

(もっと読む)

半導体装置およびその製造方法

【課題】論理素子のnチャネルMOSトランジスタに十分な膜厚の引張応力膜を形成し、メモリ素子がゲート電極間の層間絶縁膜の埋込不良を生じない製造方法の提供。

【解決手段】論理素子は、第1及び第2のnチャネルMOSトランジスタを含み、第1のゲート高さGH1及び第1のゲート長を有するゲート電極を有し、ゲート電極は第1の間隔Dを有し、メモリ素子は、第3および第4のnチャネルMOSトランジスタを含み、ゲート高さGH2および第2のゲート長を有するゲート電極を含み、論理素子及びメモリ素子は第1の引張応力膜64で覆われ、論理素子は、さらに第2の引張応力膜65で覆われ、論理素子及びメモリ素子のゲート間に形成された引張応力膜の最小距離は各々第1の距離LL及び第1の距離LMで隔てられ、第1のアスペクト比(GH1/LL)と、第2のアスペクト比(GH2/LM)とは略等しい。

(もっと読む)

半導体装置の製造方法

【課題】局所配線を有する半導体装置に関し、位置ずれに起因する電気特性や歩留まりの低下を抑制しうる半導体装置の製造方法を提供する。

【解決手段】半導体基板上に、隣接して配された第1の配線及び第2の配線を形成し、第1の配線の側壁に第1の側壁絶縁膜を、第2の配線の側壁に第2の側壁絶縁膜を形成し、第1及び第2の配線、第1及び第2の側壁絶縁膜が形成された半導体基板上に導電膜を形成し、第1及び第2の配線上の導電膜を選択的に除去し、第1の配線と第2の配線との間の領域に、導電膜により形成され、第1及び第2の側壁絶縁膜によって第1及び第2の配線から隔てられた第3の配線を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、製造コストを低減し、さらにゲート電極およびゲートコンタクトの抵抗を低減した半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明にかかる半導体装置は、ゲート電極7の少なくとも上層は、第2金属シリサイド膜としてのWSix膜72からなり、第1金属シリサイド膜としてのNiSi2膜18に含まれる第1金属(Ni)とシリコンとの結合エネルギーが、WSix膜72に含まれる第2金属(W)とのシリコンとの結合エネルギーよりも小さく、WSix膜72の組成MSix(Mは第2金属を示す)において、xが1.5以上2.0未満であることを特徴とする。

(もっと読む)

半導体装置

【課題】層間絶縁膜のエッチングの際に半導体層がエッチングされることによるコンタク

ト抵抗の増大を防ぎ、書き込み特性及び電荷保持特性に優れた不揮発性半導体記憶装置及

びその作製方法を提供する。

【解決手段】ソース領域又はドレイン領域とソース配線又はドレイン配線との間に導電層

を設ける。また、該導電層は、制御ゲート電極を形成する導電層と同じ導電層からなる。

また、該導電層を覆うように絶縁膜が設けられており、該絶縁膜は該導電層の一部が露出

するコンタクトホールを有する。また、該ソース配線又はドレイン配線は、該コンタクト

ホールを埋めるように形成されている。

(もっと読む)

ヒューズ、半導体装置、半導体装置の製造方法

【課題】高電圧が不要で安定した状態を得ること。

【解決手段】半導体装置10に形成されたヒューズ素子11は、概略的に、拡散領域22と、拡散領域22と一部重なるように拡散領域22より上方に形成された導電体25を含む。半導体装置10の半導体基板21には、拡散領域22が形成されている。半導体基板21には素子分離領域23が形成されている。拡散領域22を含む半導体基板21上には絶縁膜24が形成されている。絶縁膜24上には、導電体25が形成されている。導電体25上には、カバー膜26が形成されている。カバー膜26は、導電体25の上面及び側面を覆うように形成されている。カバー膜26は、絶縁膜24より高い引っ張り応力を持つ。

(もっと読む)

不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置

【課題】メモリセルトランジスタのゲート電極間の空隙の形状を最適化し、高性能、高信頼性を実現する不揮発性半導体記憶装置の製造方法。

【解決手段】実施の形態の不揮発性半導体記憶装置の製造方法は、半導体基板上に、第1のゲート絶縁膜、第1のフローティングゲート電極、第1のゲート間絶縁膜、第1のコントロールゲート電極、第1のゲートマスク絶縁膜の積層構造を有する複数のメモリセルゲート電極を形成する。メモリセルゲート電極の側壁部に保護膜を形成し、その一部を第1のコントロールゲート電極の側壁部の一部が露出するよう除去する。金属膜を形成し、熱処理により、金属膜と第1のコントロールゲート電極を反応させ第1の金属半導体化合物層を形成する。メモリセルゲート電極間を埋め込み、内部に空隙を有する層間絶縁膜であって、第1のコントロールゲート電極の上面よりも半導体基板から離れた位置に空隙の上端が位置する層間絶縁膜を形成する。

(もっと読む)

1 - 20 / 612

[ Back to top ]