Fターム[5F033JJ00]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060)

Fターム[5F033JJ00]の下位に属するFターム

コンタクト層なし、上層配線と一体形成 (1,607)

半導体(基板を除く) (666)

金属及びその合金(シリサイドを除く) (14,566)

シリサイド (585)

化合物 (4,106)

透光性導電膜材料 (308)

超伝導材料 (3)

Fターム[5F033JJ00]に分類される特許

41 - 60 / 219

基板の配線方法及び半導体製造装置

【課題】基板上に形成された配線用パターンの底部までCu埋め込みが可能な基板の配線方法を提供する。

【解決手段】真空状態に保持された処理容器100内にて配線用パターンが形成された基板を配線する方法であって、ウエハ上の配線用パターンを所望のクリーニングガスにより洗浄する前工程と、前工程後、クラスタ化された金属ガス(金属ガスクラスタCg)を用いて配線用パターン内に金属ナノ粒子を埋め込む埋め込み工程と、を含むことを特徴とする基板の配線方法が提供される。

(もっと読む)

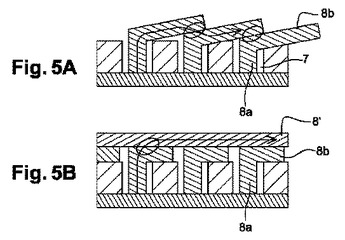

方向転換されたカーボンナノチューブで作られた相互接続構造

本発明は、少なくとも2つの異なる方向に沿って伸びる電気接続を含む電子デバイスであって、前記接続は本質的にカーボンナノチューブの束(CNT)(8)を用いて形成され、少なくとも2つのCNT束は、第1方向に沿った軸を有する部分(8a)と、第2方向に沿って方向転換された軸を有する部分(8b)とを含み、前記CNT束間の接続は前記少なくとも2つの束の一部分(8b)の重なりによって達成され、接続ライン(4)を形成する、電子デバイスに関する。  (もっと読む)

(もっと読む)

半導体集積回路および半導体集積回路設計方法

【課題】チップサイズを縮小化すること。

【解決手段】第1領域に形成される活性領域1と第2領域に形成されるウェル領域2とトランジスタゲート電極3とダミーゲート電極5と、コンタクト8とを備えている。活性領域1とトランジスタゲート電極3とは、トランジスタを形成している。トランジスタゲート電極3とダミーゲート電極5とは、互いに平行である複数の直線にそれぞれ沿うように形成されている。ダミーゲート電極5は、その第2領域とその第1領域との両方に配置されるように形成されている。コンタクト8は、その第2領域に形成され、ウェル領域2に同電位である配線層6にダミーゲート電極5を電気的に接続している。このような装置は、活性領域1とウェル領域2とが配置される領域のレイアウトサイズを小さくすることができ、その結果、チップサイズを縮小化することができる。

(もっと読む)

領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法

【課題】従来の領域分割基板と較べて部分領域を引き出し導電領域として利用した場合の抵抗値が小さく、導電性、半導電性または絶縁性の任意の基板材料を用いることができ、適用制限の少ない領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法を提供する。

【解決手段】基板30の第1表面S1から第2表面S2に亘って、当該基板30を貫通するように形成されたトレンチ31aによって、当該基板30が複数の部分領域Ceに分割され、トレンチ31aによって形成された部分領域Ceの側壁に、第1表面S1の側から第2表面S2の側に亘って、当該基板30より高い導電率を有する導電層35が形成され、導電層35を介して、トレンチ31a内に絶縁体31bが埋め込まれてなる領域分割基板A10とする。

(もっと読む)

半導体装置

【課題】ダイシングブレードでダイシングする際の層間絶縁膜間の密着性を良好にしつつ、層間絶縁膜の層間クラックを防ぐ。

【解決手段】スクライブライン領域202において、ダイシング工程においてダイシングブレードが通るブレード領域204およびブレード領域204の両側に形成され、ダイシングブレードが通らない非ブレード領域206にそれぞれダミー配線が形成され、非ブレード領域206においては上下に隣接するダミー配線106bとダミー配線110bとがダミービア108bで接続され、ブレード領域204においては、上下に隣接するダミー配線106aとダミー配線110aとがダミービアで接続されていない。

(もっと読む)

コンタクト構造体を有する半導体素子の製造方法

【課題】 コンタクト構造体を有する半導体素子の製造方法を提供する。

【解決手段】 この製造方法は半導体基板上に絶縁膜を形成する第1工程と、前記絶縁膜の所定領域内に選択的に不純物イオンを注入して前記絶縁膜の前記所定領域内に格子欠陥(lattice defects)を生成する第2工程とを含む。さらに、格子欠陥を有する絶縁膜を熱処理して前記所定領域内の格子欠陥の生成を加速する第3工程を含む。その結果、前記所定領域内に電流通路(current paths)を有する導電性の領域が形成される。前記第3工程は前記絶縁膜を少なくとも20℃/min以上の温度変化率で急冷する段階を含む。

(もっと読む)

電極基板の製造方法、電極基板、及び薄膜トランジスタ

【課題】製造工程の複雑化と製造コストの高価格化を招くことなく、多層電極間の接続を容易に行うことが可能な電極基板の製造方法、電極基板、及び薄膜トランジスタを提供する。

【解決手段】下地層の上に、下層電極、層間絶縁膜、上層電極がこの順番で積層され、下層電極と上層電極とが層間絶縁膜に形成された開口部を介して電気的に接続された電極基板の製造方法であって、下地層の上に、電極材料を含有する溶液を塗布した後、乾燥させて下層電極を形成する工程と、下層電極が形成された下地層の上に、開口部を有する層間絶縁膜を形成する工程と、開口部に溶液の溶媒を滴下し、開口部に位置する下層電極を溶解した後、乾燥させることにより、電極材料を開口部の内壁に沿ってコーヒーステイン形状に形成する工程と、電極材料が開口部の内壁に沿ってコーヒーステイン形状に形成された層間絶縁膜の上に上層電極を形成する工程と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】高密度のカーボンナノチューブを容易に配線に用いることができる半導体装置の製造方法を提供する。

【解決手段】絶縁膜7にビアホール9を形成し、ビアホール9内及び絶縁膜7上に触媒部12を形成する。絶縁膜7上の触媒部12を不活化し、ビアホール9内の触媒部12を起点としてビアホール9内にカーボンナノチューブを成長させる。

(もっと読む)

3次元半導体装置および3次元半導体装置の冷却方法

【課題】回路設計に対する制限を低減するか解消し3次元回路内のホットスポットを効率的に冷却する3次元半導体装置。

【解決手段】 チップを貫通する貫通電極を有する複数の半導体チップ1を積層してなる3次元半導体装置であって、前記貫通電極として、異種の第1、第2の材料で構成された第1、第2の貫通電極(4、5)を備え、前記第1、第2の貫通電極とそれぞれ電気的に接続され、前記第1、第2の貫通電極とそれぞれ同種の材料からなり、チップの回路面上に配置され、前記回路面上で接続された第1、第2の表面配線を有し、前記第1の貫通電極、前記第1の表面配線、前記第2の表面配線、前記第2の貫通電極に沿って電流を流すことにより、前記回路面上の前記第1の表面配線と前記第2の表面配線との接合部(2)でペルチェ吸熱が行われる。

(もっと読む)

コンタクト形成方法及び半導体装置の製造方法

【課題】自己組織化材料を用いて制御性の良いコンタクトを形成可能なコンタクト形成方法及び半導体装置の製造方法が提供する。

【解決手段】基板上に形成され、異なる層を電気的に接続するコンタクトの形成方法であって、第一の層上に形成された層間絶縁膜をエッチングし、前記第一の層の一部を露出させるコンタクトホールを形成する工程と、前記コンタクトホール内に導電性高分子ブロック共重合体を含む高分子膜を形成する工程と、前記高分子膜を相分離させ、前記コンタクトホール内の露出した前記第一の層上に導電性の配列構造からなるコンタクトを形成する工程と、前記コンタクト上に第二の層を形成する工程と、を備える。

(もっと読む)

スタック型MIMキャパシタおよびその製造方法

【課題】多くのマスク数を必要とせずに、電極材料やMIMスタック層数の制限が少なくすることのできるスタック型MIMキャパシタおよびその製造方法を提供する。

【解決手段】

スタック型MIMキャパシタ10のMIM電極13A,13Bには、MIM電極13Aの層の表面に小空孔15と大空孔16の2種類の空孔が、表面上において2次元に形成される。さらに、半導体基板11上に形成された保護膜12上に、異なる形状を持つMIM電極13A,13Bを交互に重ね、誘電体膜14を挟んでスタック型MIM構造を形成する。

(もっと読む)

キャパシタ・モジュール・アレイを含む半導体構造とその製造方法および動作方法

【課題】漏れ電流の大きいキャパシタを電気的に切断することができるキャパシタ・モジュールを含む半導体構造、これを製造する方法、およびこれを動作させる方法を提供する。

【解決手段】モジュール化したキャパシタ・アレイは複数のキャパシタ・モジュールを含む。各キャパシタ・モジュールは、キャパシタと、このキャパシタを電気的に切断するように構成されたスイッチング・デバイスと、を含む。スイッチング・デバイスは、キャパシタの漏れのレベルを検出するように構成された検知ユニットを含み、漏れ電流が所定のレベルを超えるとスイッチング・デバイスがキャパシタを電気的に切断するようになっている。各キャパシタ・モジュールは、単一のキャパシタ・プレート、2つのキャパシタ・プレート、または3つ以上のキャパシタ・プレートを含むことができる。漏れセンサおよびスイッチング・デバイスを用いて、漏れを生じたキャパシタ・アレイのキャパシタ・モジュールを電気的に切断し、これによってキャパシタ・アレイを過剰な電気的漏洩から保護する。

(もっと読む)

不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置

【課題】積層構造を有する柱状の複数のメモリセル間のショート発生を防止した不揮発性半導体記憶装置の製造方法を提供すること。

【解決手段】本発明は、マトリクス状に配置された柱状の複数のメモリセルMCを形成する工程と、直線上に並んだ一群のメモリセルの一方の底面に各々接触し、互いに平行なワードライン47a,47c,47eを形成する工程と、直線上に並んだ一群のメモリセルの他方の底面に各々接触し、互いに平行であり、かつワードラインと同一平面視で交差するビットライン56b,56dを形成する工程とを含み、ワードラインを形成する工程では、複数のメモリセルのうち同じワードラインまたはビットラインに接触する一群のメモリセルの端部に位置する端部メモリセルMCe1,MCe3と所定間隔を隔てて配置され、メモリセルMCと同じ積層構造を有するダミーメモリセルDMC1,DMC2を形成する。

(もっと読む)

カーボンナノチューブ配線及びその製造方法

【課題】カーボンナノチューブを有するプラグ配線において良好な電気的接続を得ることができるカーボンナノチューブ配線及びその製造方法を提供する。

【解決手段】第1配線層12上に層間絶縁膜13が形成され、層間絶縁膜13上に第2配線層14が形成されている。第1配線層12と第2配線層14との間の層間絶縁膜13内にはコンタクト孔15が形成される。コンタクト孔15内には、一端が第1配線層12に接続され、他端が第2配線層14に接続された複数のカーボンナノチューブ16が形成されている。さらに、層間絶縁膜13と第2配線層14との間にはストッパ膜17が形成され、ストッパ膜17の一部は複数のカーボンナノチューブ16の前記他端間に充填されている。

(もっと読む)

埋め込み配線を有する半導体装置及び埋め込み配線の製造方法

【課題】ディッシングを抑制できる太幅の埋め込み配線を有する半導体装置、及びディッシングを抑制できる太幅の埋め込み配線の簡易な製造方法を提供する。

【解決手段】金属製埋め込み配線を有する半導体装置であって、該埋め込み配線の表面の長さ方向に、所定値以下の間隔で、該金属よりも硬度の高い金属材料からなるバリア線6が配設されていることを特徴とする半導体装置及びその埋め込み配線の製造方法。

(もっと読む)

カーボン・ナノチューブを選択的に成長させる方法

【課題】1つ以上のカーボン・ナノチューブを選択的に成長させる方法を提供する。

【解決手段】本方法は、上面を有する絶縁層を基板上に形成するステップと、絶縁層内にビアを形成するステップと、ビアの側壁及び底面を含め、絶縁層上に活性金属層を形成するステップと、ビアの内部での1つ以上のカーボン・ナノチューブの選択的な成長を可能にするために、イオン・ビームを用いて上面の部分にある活性金属層を除去するステップとを含む。

(もっと読む)

基板の処理方法及び基板の処理装置

【課題】 層間絶縁膜にLow−k材を使用した基板であっても、層間絶縁膜の経時劣化や変質の可能性を低くできる基板の処理方法を提供すること。

【解決手段】 シリコン酸化膜よりも低い誘電率の誘電体層を含む基板を処理する基板の処理方法であって、不活性ガスの雰囲気中で、前記誘電体層を脱水縮合処理するために加熱する脱水工程と、少なくとも水素原子を含むガスの雰囲気中で、前記基板をアニールする工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極間を埋め込む膜に吸湿性の高い膜を用いた半導体装置において、金属配線の信頼性劣化を防ぐ。

【解決手段】半導体装置50は、基板1上に形成された複数のゲート電極2と、複数のゲート電極2上を含む基板上を覆う第1の層間絶縁膜5と、第1の層間絶縁膜5上を覆う第2の層間絶縁膜6と、第1の層間絶縁膜5及び第2の層間絶縁膜6を貫通し、それぞれ基板1上の所定箇所又は複数のゲート電極2のいずれか一つに達する複数のコンタクトプラグ7と、第2の層間絶縁膜6上に形成され、コンタクトプラグ7に接続された金属配線9を含む配線形成層8とを備える。第1の層間絶縁膜5は、少なくとも一つのゲート電極2上方に第1の凹部5aを有すると共に、複数のゲート電極2及び基板1に接する下部膜3と、第1の凹部5a以外の部分において下部膜3上に配置された上部膜4とを有し、第1の凹部5a内に、第2の層間絶縁膜6が埋め込まれている。

(もっと読む)

カーボンナノチューブへの金属接合方法及びカーボンナノチューブを用いた配線構造

【課題】 カーボンナノチューブと電極をなす金属とを強い結合力でかつ十分な密着性を持って接合できるカーボンナノチューブへの金属接合方法及びCNTを用いた配線構造を提供する。

【解決手段】本発明のカーボンナノチューブへの金属接合方法は、カーボンナノチューブを成長させる工程と、成長させたカーボンナノチューブの欠陥に硫黄原子を導入する工程と、前記硫黄原子を介して、Au、Ag、Pt、Pd、Ru、Rh、Os、Ir、Hg、Si、Ga及びAsの中から選択された少なくとも1つの金属またはこれらの合金を接合する工程とを、含む。

(もっと読む)

半導体装置の製造方法

【課題】下層金属膜上の絶縁性保護膜に貫通部を形成した後の残渣処理を簡単かつ確実に行い、下層金属膜の露出面を良好な状態に維持することによって上層金属膜の形成を確実に行うこと。

【解決手段】ウェハ表面の下層金属膜上に絶縁性保護膜を形成する。その絶縁性保護膜上にマスクを形成し、このマスクを用いて絶縁性保護膜を選択的に除去して下層金属膜の一部を露出させる。薬液によるウェット処理を行ってマスクを除去する。その後、その露出した下層金属膜の表面に存在する残渣を酸素系プラズマ処理により除去する。酸素系プラズマ処理によって下層金属膜の露出面にできたダメージを、水素系プラズマ処理を行って取り除く。そして、下層金属膜の露出面上に上層金属膜をメッキ等により積層する。

(もっと読む)

41 - 60 / 219

[ Back to top ]