Fターム[5F033JJ03]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 半導体(基板を除く) (666)

Fターム[5F033JJ03]の下位に属するFターム

Fターム[5F033JJ03]に分類される特許

1 - 20 / 58

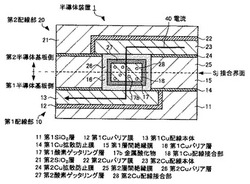

半導体装置、電子デバイス、及び、半導体装置の製造方法

【課題】 より信頼性の高いCu−Cu接合界面を有する半導体装置及びその製造方法を提供する。

【解決手段】 半導体装置1を、第1の配線18を含む第1半導体部10と、第1半導体部10と貼り合わせて設けられ、第1の配線18と電気的に接合された第2の配線28を含む第2半導体部20とを備える構成とする。さらに、半導体装置1は、酸素に対して水素よりも反応し易い金属材料と酸素とが反応して生成された金属酸化物17bを備える。そして、この金属酸化物17bを、第1の配線18及び第2の配線28の接合界面Sj、並びに、第1の配線18及び第2の配線28の少なくとも一方の内部を含む領域に拡散させた構成とする。

(もっと読む)

半導体装置の製造方法

【課題】膜厚の薄い抵抗体もつ抵抗素子を形成する際に、抵抗体の断線に対して強い抵抗素子を提供する。

【解決手段】バリアメタル膜とアルミ電極膜からなる積層電極の先端領域を単層のバリアメタル電極とし、並列するバリアメタル電極間に電気的に接続する抵抗体をリフトオフ法にて形成する。

(もっと読む)

半導体記憶装置

【課題】動作速度の向上と面積の縮小を図る。

【解決手段】半導体記憶装置は、半導体基板100と、前記半導体基板上に形成され、データを記憶する複数のメモリセルが配置されたメモリセルアレイ部Aと、前記メモリセルアレイ部上に絶縁層を介して形成され、かつ、前記絶縁層および前記メモリセルアレイ部を貫通する孔106内に形成されて前記半導体基板に接続された単結晶半導体層109と、前記単結晶半導体層上に形成された回路部Bと、を具備し、前記メモリセルアレイ部上における前記単結晶半導体層の下部側は、上部側よりもGe濃度が高い。

(もっと読む)

分離トレンチの形成方法

【課題】隣接デバイスの特性への悪影響を低減するTSV相互接続構造の製造方法を提供する。

【解決手段】第1の主面S1を有する基板を設け、少なくとも一つのTSV穴部と、TSV穴部を囲み残りの基板材料によって分離されるトレンチ状構造3、とをエッチングにより同時に作製する。基板の第1の主面でトレンチ状構造の開口をピンチオフするためと、TSV穴部側壁を平滑にするために、誘電性のライナー2a、2bを堆積し、トレンチ状構造にエアギャップ4を作製する。TSV相互接続10を生成するためにTSV穴部に導体材料を堆積する。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリセル領域の周辺に金属電極を有するアンチフューズを製造歩留り良く形成する。

【解決手段】MOSトランジスタを備えたメモリセルを有するメモリセル領域と、アンチフューズを備えた周辺回路領域とを有する半導体装置において、メモリセルを構成するコンタクトプラグ又はビット配線と同層に形成される周辺回路のコンタクトプラグ又は配線を用いて、アンチフューズの電極を形成する。

(もっと読む)

配線構造物及びその製造方法

【課題】短時間で、配線母体の内部に、種々のトポロジーの貫通配線や連結配線を埋め込むことが可能な配線構造物を提供する。

【解決手段】配線母体11と、配線母体11の内部に設けられた複数の穴部の内部にそれぞれ配置された、配線子連続体(Qi1,Qi2,Qi3,……,Qin-1,Qin;Qi+11,Qi+12,Qi+13,……,Qi+1n-1,Qi+1n)からなる複数の貫通配線部とを備える。複数の配線子連続体のそれぞれをなす複数の配線子Qi1,Qi2,Qi3,……,Qin-1,Qin;Qi+11,Qi+12,Qi+13,……,Qi+1n-1,Qi+1nのそれぞれは、コア部と、コア部を被覆し、コア部より融点の低い導電体からなるシェル部Qi,shell,Qi+1,shellを有する。複数の配線子は、それぞれのシェル部を互いに溶融することにより金属学的に接合される。

(もっと読む)

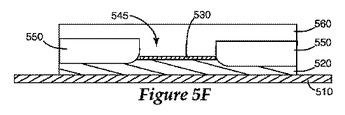

3次元集積のための裏側ダミー・プラグを含む半導体構造およびこれを製造する方法

金属キャリアを有する半導体デバイスおよび製造方法

【課題】 金属キャリアを有する半導体デバイス及び製造方法を提供する。

【解決手段】 金属キャリア基板を含む半導体デバイス。キャリア基板の上には、Alx1Gay1Inz1N(x1+y1+z1=1、x1≧0、y1≧0、z1≧0)の第1の半導体層が形成される。第1の半導体層の上にはAlx2Gay2Inz2N(x2+y2+z2=1、x2>x1、y2≧0、z2≧0)の第2の半導体層が配され、第2の半導体層の上にはゲート領域が配置される。半導体デバイスはさらに、ソース領域およびドレイン領域を含み、これらの領域のうちの一方が金属キャリア基板と電気的に接続され、第1の半導体層を介して延在する導電性領域を含む。

(もっと読む)

半導体ダイにおける応力を軽減するためのルーティング層

【解決手段】

半導体ダイのためのルーティング層が開示される。ルーティング層は、半田バンプを取り付けるためのパッドと、集積回路を有するダイのバンプパッドにボンディングされるボンドパッドと、ボンドパッドをパッドと相互接続するトレースと、を含む。ルーティング層は誘電体材質の層上に形成される。ルーティング層は、パッドに取り付けられる半田バンプからの応力を吸収するように、幾つかのパッドを少なくとも部分的に包囲する伝導性トレースを含む。パッドを包囲するトレースの一部は、半田バンプに隣接する下層の誘電体材質の一部を応力から保護する。

(もっと読む)

電子モジュールの製造方法、および、電子モジュール

半導体基板に集積された回路と、基板と、ヒートシンクとしての支持体と、基板および支持体をはんだ付けにより接続する熱伝導性接続部とを備えた電子モジュールを提案する。ここでは、基板で用いられる後面金属化部として、まず第1の厚いAu層(23)、ついでバリア層(24)、最後に第2の薄いAu層(25)が堆積される。バリア層の材料は、はんだ付け過程において、第2のAu層の領域のAuSn液相のSnないしAuSnが第1のAu層(23)へ浸入することを阻止するように選定される。また、基板の貫通孔にも、後面金属化部の積層体が堆積される。ここで、第2のAu層の表面は、バリア層から拡散する材料によって、はんだ付け材料に対する低減された濡れ性を有する。  (もっと読む)

(もっと読む)

紫外線架橋性材料の基板に対する接着を改善するための方法

【課題】紫外線の暴露により架橋し得る材料で作製された層の基板に対する接着を改善するための方法、およびそれを利用しトランジスタを製造する方法を提供する。

【解決手段】紫外線への暴露により架橋し得る材料Mで作製された層の基板Sの表面に対する接着を改善する際に、a)材料Mの表面の反応基M1と反応し得る第1の反応基F1と、基板Sの表面を構成する材料(複数可)と結合を形成し得る第2の反応基F2とを備える少なくとも1種の分子Fを含む未重合の重合性組成物Pの堆積ステップ、b)ステップa)において得られた未重合の組成物Pの層上への、未架橋の材料Mで作製された層の堆積ステップ、およびc)ステップb)において得られた3層構造に紫外線を暴露するステップ。

(もっと読む)

半導体構造、半導体構造の形成方法、半導体装置の動作方法(高周波の高調波を減少するためのSOIRFスイッチ)

【課題】SOI基板における容量結合を減少した集積回路を提供する。

【解決手段】底部半導体層と同じ導電型のドーパントを含む第1のドープされた半導体領域18及び反対導電型のドーパントを含む第2のドープされた半導体領域28がSOI基板の埋め込み絶縁層20の直下に形成される。第1のドープされた半導体領域18及び第2のドープされた半導体領域28は、共にグランド電位に接続されるか、又は底部半導体層への少数キャリアの順方向バイアス注入に基づく過剰な電流を生じるには不十分は電圧、即ち、0.6V乃至0.8Vを越えない電位差を保って底部半導体層に対して順方向バイアスされる。上部半導体の半導体装置内の電気信号により誘起される電荷層内の電荷は第1及び第2のドープされた半導体領域に接続されている電気的コンタクトを介して引き出され、これにより半導体装置内の高調波信号を減少させる。

(もっと読む)

冷却機構を含む接合型半導体構造体とその形成方法

【課題】 冷却機構を有する接合型半導体基板を形成するための構造体、設計構造体、及びその形成方法を提供すること。

【解決手段】 2つの半導体基板を備える接合型基板が提供される。各々の半導体基板は、半導体デバイスを含む。少なくとも1つの基板貫通ビアが2つの半導体基板の間に設けられ、それらの間に単一の経路を提供する。2つの半導体基板の底側は、冷却機構を含む少なくとも1つの接合材料層によって接合される。1つの実施形態において、冷却機構は冷却チャネルであり、その中を通って冷却流体が流動し、接合型基板内の半導体デバイスの動作中に接合型半導体基板を冷却する。別の実施形態において、冷却機構は、2つの端部とそれらの間の連続した経路を備えた導電性冷却フィンである。冷却フィンはヒートシンクに接続され、接合型基板内の半導体デバイスの動作中に接合型半導体基板を冷却する。

(もっと読む)

陽極酸化された薄膜構造用の電気的接続

第1の薄膜メタライゼーション層と第2の薄膜メタライゼーション層とを電気的に接続する回路ビアの形成のための手法が述べられる。ビアの形成では、第1のメタライゼーション層の陽極酸化に先立って、ビア接続領域に配置される陽極酸化バリア及び/又は補助パッドを使用する。バリアを形成するために使用される材料は、陽極酸化の際に陽極酸化液を実質的に透過せず、導電層とバリアとの間に酸化物が形成されることを阻止するものである。補助パッドは非陽極酸化性であり、陽極酸化の際に、パッドを通じて電流が流れることを実質的に防止するためにバリアによって覆われる。陽極酸化の後に、バリアは除去される。補助パッドが充分な導電性を有する場合には、バリアの除去後に第1のメタライゼーション層上に残存されてもよい。第2のメタライゼーション層が陽極酸化層上に配置され、ビア接続領域において第1の導電層と電気的に接触する。  (もっと読む)

(もっと読む)

半導体装置とその製造方法

【課題】柱状半導体層が微細化されて高集積化されても、コンタクト抵抗の増加を抑制する構造の半導体装置を提供する。

【解決手段】半導体装置は、基板(半導体基板1)と、半導体基板1上に設けられた、半導体柱状部(柱状半導体層3)と、の天面に接するように設けられた、柱状半導体層3と同径以下のコンタクト柱状部(コンタクト層7)と、この天面に設けられた凹部をと備えるものである。

(もっと読む)

3−D積層型デバイスのESD保護を可能にするシステム及び方法

【解決手段】静電気放電(ESD)保護デバイスが、積層型半導体ダイのアクティブレイヤ間の縦型の空間に形成され、これにより、そうでなければ通信目的のためにしか使用されないであろう空間を利用する。シリコン貫通ビア(TSV:through silicon via)の縦型の表面領域は、ESDイベントに起因する大電圧を緩和するために使用される。一実施形態では、ESDダイオードは、積層型デバイスの半導体ダイのアクティブレイヤ間の縦型TSV内に形成される。このESDダイオードは、積層の半導体ダイの両方の上の回路によって共有され、これによって空間を節約し、そしてESD保護回路によって必要とされるダイ面積を低減し得る。 (もっと読む)

半導体装置及びその作製方法

【課題】絶縁膜中にコンタクトホールを形成せずに、絶縁膜の表面と裏面の間に導電領域を形成することを課題とする。

【解決手段】基板上の半導体素子と、半導体素子上の絶縁膜と、絶縁膜中に、欠陥の多い領域と欠陥の少ない領域とを有し、欠陥の多い領域は、金属元素が拡散され、絶縁膜の表面の一部と裏面の一部をつなぐ導電領域である半導体装置、及び、基板上に半導体素子を形成し、半導体素子上に絶縁膜を形成し、絶縁膜上に、半導体素子と電気的に接続された第1の導電膜を形成し、絶縁膜中にイオンを添加して、あるいはレーザビームを照射して、欠陥の多い領域を形成し、欠陥の多い領域上に、金属元素を含む導電材料を形成し、欠陥の多い領域に、金属元素を拡散させ、絶縁膜中に、第1の導電膜と、金属元素を含む導電材料とを電気的に接続する導電領域を形成する半導体装置の作製方法に関する。

(もっと読む)

高耐圧半導体デバイス、及び高耐圧半導体デバイスの製造方法

【課題】多層配線形成時のプラズマダメージによるVt変動を利用してVtを制御した高耐圧半導体デバイス、及びその製造方法を提供する。

【解決手段】同一のシリコン基板上に、350Å以上のゲート絶縁膜20、40を有する複数のMOSトランジスタ10、30を備え、ゲート電極12、32が前記ゲート絶縁膜20、40と接している部分の面積Sgと、前記ゲート電極20、40側から見たときに前記ゲート電極20、40上に形成されたコンタクト14、34の総開口面積Scと、の面積比が異なるMOSトランジスタ10、30を有することを特徴とする高耐圧半導体デバイス。

(もっと読む)

ナノ構造処理のための導電性補助層の形成及び選択的除去

一又は複数のナノ構造の作成方法が開示されており、当該方法は:基板の上部表面上に導電層を形成すること;導電層上に触媒のパターン層を形成すること;触媒層上に一又は複数のナノ構造を成長させること;及び一又は複数のナノ構造の間及び周囲の導電層を選択的に除去することを含んでなる。デバイスもまた開示されており、該デバイスは、基板、ここで基板は一又は複数の絶縁領域によって隔てられた一又は複数の露出金属島を含んでなる;一又は複数の露出金属島又は絶縁領域の少なくともいくつかを覆う基板上に配された導電性補助層;導電性補助層上に配された触媒層;及び触媒層上に配された一又は複数のナノ構造を含んでなる。 (もっと読む)

窒化物半導体装置及びその製造方法

【課題】窒化物半導体装置において、半絶縁性SiC基板と比較して安価に入手することができる導電性SiC基板を使用してコストを低く抑えながら、良好な出力特性及び高周波特性が得られるようにする。

【解決手段】窒化物半導体装置を、導電性SiC基板1上に形成された窒化物半導体積層構造2と、窒化物半導体積層構造2の活性領域の下方の領域に形成されたアモルファスカーボン層3とを備えるものとする。

(もっと読む)

1 - 20 / 58

[ Back to top ]