Fターム[5F033JJ34]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 化合物 (4,106) | 窒化物 (3,695) | WN (404)

Fターム[5F033JJ34]に分類される特許

1 - 20 / 404

半導体装置、半導体装置の製造方法、および電子機器

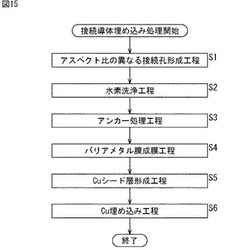

【課題】アスペクト比の異なる複数の開口下部に接続される配線に対して最適な処理を施すことができるようにする。

【解決手段】半導体装置の製造方法において、第1の半導体基板と第2の半導体基板が接合された半導体基板の第1の開口の下部配線と、貫通接続孔と異なるアスペクト比の第2の開口の下部配線に対して、バリアメタル膜の成膜と、スパッタガスによる物理エッチングを同時に行うアンカー処理工程が含まれる。本技術は、例えば、固体撮像装置などの半導体装置に適用できる。

(もっと読む)

半導体装置の製造方法

【課題】接続孔部分における電気的特性のばらつきを低減することにより、半導体装置の信頼性および製造歩留まりを向上させることのできる技術を提供する。

【解決手段】成膜装置のドライクリーニング処理用のチャンバ57に備わるウエハステージ57a上に半導体ウエハSWを置いた後、還元ガスを供給して半導体ウエハSWの主面上をドライクリーニング処理し、続いて180℃に維持されたシャワーヘッド57cにより半導体ウエハSWを100から150℃の第1の温度で熱処理する。次いで半導体ウエハSWをチャンバ57から熱処理用のチャンバへ真空搬送した後、そのチャンバ57において150から400℃の第2の温度で半導体ウエハSWを熱処理することにより、半導体ウエハSWの主面上に残留する生成物を除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトプラグに接続される配線間隔の縮小を可能にする半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板に第1の領域と第2の領域とを定義し、第1の領域に第1のサイズを持つ第1の素子を形成し、第2の領域に、第1のサイズとは異なる第2のサイズを持つ第2の素子を形成し、第1の素子及び第2の素子を覆うように半導体基板上に第1の層間絶縁膜を形成し、第1の領域上の第1の層間絶縁膜を貫通し第1の素子の一部を露出させる第1のコンタクトホールを形成し、第2の領域上の第1の層間絶縁膜を貫通し第2の素子の一部を露出させる第2のコンタクトホールを形成し、第1のコンタクトホール及び第2のコンタクトホールをそれぞれ埋める第1のコンタクトプラグ及び第2のコンタクトプラグを同時に形成する。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】実効的な低配線間容量を維持しつつ、高密着性かつ高い配線間絶縁信頼性を有する多層配線技術を提供する。

【解決手段】第一の絶縁膜は、シリコン、酸素及び炭素を含むシロキサン構造を含む少なくとも1層以上の絶縁膜であり、第一の絶縁膜内部のシロキサン構造は炭素原子数がシリコン原子数よりも多く、第一の絶縁膜と金属との界面及び第一の絶縁膜と第二の絶縁膜との界面のうち少なくとも何れか一方に、第一の絶縁膜内部よりも単位体積当たりの炭素原子数が少なく、且つ酸素原子数が多い改質層が形成されていることを特徴とする半導体装置。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体を含み、高速動作が可能なトランジスタを提供する。または、該トランジスタを含む信頼性の高い半導体装置を提供する。

【解決手段】下地絶縁層の溝に埋め込まれた電極層上に、一対の低抵抗領域及びチャネル形成領域を含む酸化物半導体層を設ける。チャネル形成領域は、サイドウォールを側壁に有するゲート電極層と重なる位置に形成される。溝は、深い領域と浅い領域を有し、サイドウォールは、浅い領域と重なり、配線との接続は、深い領域と重なる。

(もっと読む)

電子装置およびその製造方法

【課題】信頼性の高いコンタクト構造を提供する。

【解決手段】電子装置は第1の絶縁膜と、前記第1の絶縁膜の表面に形成された配線溝と、Cuよりなり前記配線溝を充填する配線パタ―ンと、前記配線パタ―ンの表面に形成され、Cuよりも大きな弾性率を有する金属膜と、前記第1の絶縁膜上に形成された第2の絶縁膜と、Cuよりなり、前記第2の絶縁膜中に形成され、前記金属膜とコンタクトするビアプラグと、を備える。

(もっと読む)

表示装置用配線構造

【課題】450〜600℃程度の高温下に曝されてもヒロックが発生せず高温耐熱性に優れており、配線構造全体の電気抵抗(配線抵抗)も低く抑えられており、更にフッ酸耐性にも優れた表示装置用配線構造を提供する。

【解決手段】本発明の表示装置用配線構造は、基板側から順に、Ta、Nb、Re、Zr、W、Mo、V、Hf、Ti、CrおよびPtよりなる群(X群)から選択される少なくとも一種の元素と、希土類元素の少なくとも一種とを含むAl合金の第1層と;Ti、Mo、Al、Ta、Nb、Re、Zr、W、V、Hf、およびCrよりなる群(Y群)から選択される少なくとも一種の元素の窒化物、またはAl合金の窒化物の第2層と、が積層された表層構造を有する。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】半導体装置の特性を損なうことがない半導体装置およびその作製方法を提供する。

【解決手段】酸化物半導体層を含むトランジスタ(半導体装置)において、電極層を酸化物半導体層の下部に接して形成し、不純物を添加する処理により酸化物半導体層に自己整合的にチャネル形成領域と、チャネル形成領域を挟むように一対の低抵抗領域を形成する。また、電極層および低抵抗領域と電気的に接続する配線層を絶縁層の開口を介して設ける。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜と金属膜との接触抵抗を低減する。オン特性の優れた酸化物半導体膜を用いたトランジスタを提供する。高速動作が可能な半導体装置を提供する。

【解決手段】酸化物半導体膜を用いたトランジスタにおいて、酸化物半導体膜に窒素プラズマ処理を行うことで酸化物半導体膜を構成する酸素の一部が窒素に置換された酸窒化領域を形成し、該酸窒化領域に接して金属膜を形成する。該酸窒化領域は酸化物半導体膜の他の領域と比べ低抵抗となり、また、接触する金属膜との界面に高抵抗の金属酸化物を形成しにくい。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の外部端子に加わる外力により外部端子の下方の絶縁膜にクラックが生じるのを抑制または防止する。

【解決手段】半導体基板1の主面上には複数の配線層が形成されている。この複数の配線層のうちの最上の配線層MHの直下の第5配線層M5において、最上の配線層MHのボンディングパッドPDのプローブ接触領域PAの直下には、導体パターン(第5配線5F、ダミー配線およびプラグ6C)を形成しない。上記第5配線層M5において、最上の配線層MHのボンディングパッドPDのプローブ接触領域PAの直下以外の領域には、導体パターン(第5配線5F、ダミー配線およびプラグ6C)を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】低抵抗の微細配線構造を有する半導体装置を提供する。

【解決手段】第1配線420は、半導体基板100上に設けられている。第1ビア440は、第1配線420上に設けられている。また、第1ビア440の底面は、第1配線420に接している。第1絶縁層330は、半導体基板100上に設けられ、少なくとも第1配線420の上面および第1ビア440の側面と接している。第1配線420および第1ビア440のうち各々の側面の少なくとも一部は、各々の金属の結晶粒を分断している。

(もっと読む)

貫通配線基板および貫通配線基板の製造方法

【課題】貫通孔内に形成された導電層に加わる応力を抑制できるとともに、導電層からの効果的な放熱も促すことができる貫通配線基板、及びこの貫通配線基板の製造方法を提供する。

【解決手段】半導体基板11(基板)の一方の面11aに配された電極層12と、電極層12の少なくとも一部が露呈するように半導体基板11内に開けられた貫通孔20と、貫通孔20の内側面20aを覆い、電極層12の少なくとも一部が露呈するように配された第一絶縁層15と、第一絶縁層15を介して、貫通孔20の内側面20a及び電極層12の露呈部を覆うように配され、電極層12と電気的に接続された導電層5と、導電層5を覆うように配された第二絶縁層16と、を少なくとも備えてなる貫通配線基板10であって、第二絶縁層16は、導電層5の表面形状に沿って形成されていることを特徴とする。

(もっと読む)

低抵抗及び低インダクタンスの裏面貫通ビア及びその製造方法

【課題】裏面コンタクト構造体及びその構造体を製造する方法を提供する。

【解決手段】表面及び対向する裏面を有する基板100の表面上に第1誘電体層105を形成することと、第1誘電体層を貫通して前記基板の表面にまで延びる導電性の第1スタッド・コンタクト140Bを第1誘電体層内に形成することと、基板の裏面から基板を薄くして基板の新しい裏面を形成することと、基板の新しい裏面から前記第1誘電体層まで延びるトレンチ165を基板内に形成して第1スタッド・コンタクトの底面をトレンチ内に露出させることと、基板の新しい裏面、トレンチの側壁、第1誘電体層の露出面、及び第1スタッド・コンタクトの露出面の上に、トレンチを完全に充填するのに十分には厚くない共形導電層170、175を形成することと、を含む前記方法。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、小型化を図ることが可能になると共に、絶縁リングで囲まれた貫通電極を狭ピッチで配置することの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】回路素子層5が形成される表面1a、及び裏面1bを有する半導体基板1と、半導体基板1を貫通し、かつ半導体基板1の表面1a側から半導体基板1の裏面1b側に向かうにつれて幅が広くなる貫通電極7と、貫通電極7を囲むように半導体基板を貫通し、かつ半導体基板1の表面1a側から半導体基板1の裏面1b側に向かうにつれて幅が狭くなる第1の絶縁リング3と、を有し、半導体基板1の厚さ方向Aにおいて、第1の絶縁リング3の少なくとも一部と対向するように貫通電極7を配置する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体層を用いた素子を配線層間に形成し、かつ、ゲート電極の材料を、配線の材料以外の導電体にする。

【解決手段】第1配線層150の表層には、第1配線210が埋め込まれている。第1配線210上には、ゲート電極218が形成されている。ゲート電極218は、第1配線210に接続している。ゲート電極218は、第1配線210とは別工程で形成されている。このため、ゲート電極218を第1配線210とは別の材料で形成することができる。そしてゲート電極218上には、ゲート絶縁膜219及び半導体層220が形成されている。

(もっと読む)

金属付着物の除去方法、基板処理装置、および記録媒体

【課題】有機化合物ガスによる基板処理を清浄に行うことが可能となる金属付着物の除去方法および基板処理装置を提供する。

【解決手段】金属付着物の除去方法は、金属層が形成された被処理基板を処理する処理空間を内部に有する処理容器の内部に付着した金属付着物を昇華させるように、前記処理容器内部の温度と、前記処理空間の圧力とを、制御する。

(もっと読む)

半導体装置の製造方法

【課題】 絶縁膜に、底面及び側面の形状を良好に保って配線溝を形成する技術が望まれている。

【解決手段】 基板の上に、仮のパターンを形成する。仮のパターンを囲むように、基板の上に層間絶縁膜を形成する。層間絶縁膜を形成した後、仮のパターンを除去する。仮のパターンが除去されることによって現れた凹部の側面及び底面に、第1のバリア膜及びシード膜を形成する。シード膜の上に、配線材料を堆積させることにより、凹部を配線材料で埋め込む。

(もっと読む)

半導体装置、電子装置、配線基板、半導体装置の製造方法、及び配線基板の製造方法

【課題】配線基板に半導体素子を形成する場合において、配線基板の製造工程数を少なくする。

【解決手段】コア層200の一面上には、第1配線232が設けられている。第1配線232上、及びその周囲に位置するコア層200の一面上には、半導体層236が形成されている。第1配線232及び半導体層236は、半導体素子を形成している。本実施形態において半導体素子は、第1配線232をゲート電極としたトランジスタ230であり、半導体層236と第1配線232の間に、ゲート絶縁膜234を有している。

(もっと読む)

半導体装置の製造方法

【課題】LTHC膜に由来する基板の汚染を低減する。

【解決手段】基板の第1の主面を光熱変換膜を介して支持基板に張付ける工程と、支持基板上に露出した光熱変換膜を除去する工程と、を有することを特徴とする半導体装置の製造方法。支持基板上に光熱変換膜を形成する工程と、半導体基板より外側に光熱変換膜が延在するように半導体基板を前記支持基板に張付ける工程と、光熱変換膜に汚染防止処理を行う工程と、支持基板と半導体基板とを分離させる工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】基板のエッジ部分での膜剥がれを防止し、半導体装置を効率良く製造する。

【解決手段】基板1の上方に低誘電体膜31を形成する際に、基板1のエッジ部分1Aをエッジカット工程にて洗い流すことで段差部31Aが形成される。低誘電体膜31に配線溝41を形成した後、導電膜43を埋め込む。基板1のエッジ部分1Aの導電膜43を洗い流すと、導電膜43が埋め込まれていない配線溝41Aが形成される。配線溝41Aを保護フィルム51で覆ってから、CMP法にて余分な導電膜43を除去する。この後、保護フィルム51を基板1から取り外す。

(もっと読む)

1 - 20 / 404

[ Back to top ]