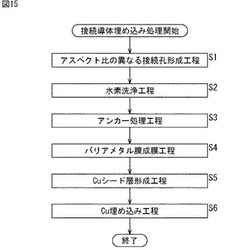

Fターム[5F033JJ36]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 化合物 (4,106) | 炭化物 (89)

Fターム[5F033JJ36]に分類される特許

1 - 20 / 89

半導体装置、半導体装置の製造方法、および電子機器

【課題】アスペクト比の異なる複数の開口下部に接続される配線に対して最適な処理を施すことができるようにする。

【解決手段】半導体装置の製造方法において、第1の半導体基板と第2の半導体基板が接合された半導体基板の第1の開口の下部配線と、貫通接続孔と異なるアスペクト比の第2の開口の下部配線に対して、バリアメタル膜の成膜と、スパッタガスによる物理エッチングを同時に行うアンカー処理工程が含まれる。本技術は、例えば、固体撮像装置などの半導体装置に適用できる。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】実効的な低配線間容量を維持しつつ、高密着性かつ高い配線間絶縁信頼性を有する多層配線技術を提供する。

【解決手段】第一の絶縁膜は、シリコン、酸素及び炭素を含むシロキサン構造を含む少なくとも1層以上の絶縁膜であり、第一の絶縁膜内部のシロキサン構造は炭素原子数がシリコン原子数よりも多く、第一の絶縁膜と金属との界面及び第一の絶縁膜と第二の絶縁膜との界面のうち少なくとも何れか一方に、第一の絶縁膜内部よりも単位体積当たりの炭素原子数が少なく、且つ酸素原子数が多い改質層が形成されていることを特徴とする半導体装置。

(もっと読む)

Cu配線の形成方法および成膜システム

【課題】Cuめっきを用いることなくPVDのみでトレンチまたはホールCuを埋め込んでCu配線を形成すること。

【解決手段】ウエハWに形成されたトレンチ203を有する層間絶縁膜202の全面にバリア膜204を形成する工程と、バリア膜204の上にRu膜205を形成する工程と、Ru膜205の上にPVDによりCuがマイグレーションする条件でトレンチ203内に第1のCu膜206を形成する工程と、第1のCu膜206の上に、第1のCu膜206よりも大きな成膜速度でPVDにより第2のCu膜207を形成する工程と、CMPにより全面を研磨する工程とを有する。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu合金層と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに半導体層との密着性に優れており、且つ電気抵抗率が低減された配線構造を提供すること。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記Cu合金層は、基板側から順に、合金成分としてMnと、X(Xは、Ag、Au、C、W、Ca、Mg、Al、SnおよびNiよりなる群から選択される少なくとも一種)を含有する第一層と、純Cu、またはCuを主成分とするCu合金であって前記第一層よりも電気抵抗率の低いCu合金からなる第二層、とを含む積層構造である。

(もっと読む)

成膜方法及び成膜装置

【課題】 ボイド等の発生を防止できるように凹部内に金属膜の成膜を施すことができる成膜方法である。

【解決手段】 処理容器22内でプラズマにより金属のターゲット76から金属イオンを発生させてバイアスにより引き込んで凹部4が形成されている被処理体に金属の薄膜を堆積させる成膜方法において、ターゲットから金属イオンを生成し、その金属イオンをバイアスにより引き込んで凹部内に下地膜90を形成する下地膜形成工程と、金属イオンを発生させない状態でバイアスにより希ガスをイオン化させると共に発生したイオンを引き込んで下地膜をエッチングするエッチング工程と、ターゲットをプラズマスパッタリングして金属イオンを生成し、その金属イオンをバイアス電力により引き込んで金属膜よりなる本膜92を堆積しつつ、その本膜を加熱リフローさせる成膜リフロー工程とを有する。

(もっと読む)

半導体素子、半導体装置及び半導体素子の作製方法

【課題】半導体領域に酸化物半導体を用いた、高耐圧で、大電流の制御が可能であり、かつ量産性に優れた半導体素子を提供することを課題の一とする。また、該半導体素子を用いた半導体装置を提供することを課題の一とする。また、該半導体素子の作製方法を提供することを課題の一とする。

【解決手段】半導体領域に酸化物半導体を用いたトランジスタと、トランジスタのゲート電極層、ソース電極層及びドレイン電極層の各々と電気的に接続した貫通電極を備えた半導体チップを積層し、トランジスタを電気的に並列接続することによって、実質的にW長の長い半導体素子を提供する。

(もっと読む)

カーボンナノチューブの形成方法及びカーボンナノチューブ成膜装置

【課題】被処理体上のビアホールや配線用溝等の開口部に高密度にカーボンナノチューブ膜を埋め込むことができるカーボンナノチューブの形成方法を提供する。

【解決手段】表面に1又は複数の開口部を有し、当該開口部底面に触媒金属層が形成された被処理体を準備し(STEP1)、触媒金属層に酸素プラズマ処理を施し(STEP2)、酸素プラズマ処理後の触媒金属層に水素含有プラズマ処理を施して、触媒金属層の表面を活性化し(STEP3)、その後、触媒金属層の上にプラズマCVDによりカーボンナノチューブを成長させて、被処理体の開口部内をカーボンナノチューブで充填する(STEP5)。

(もっと読む)

酸化表面層のハイブリッドその場ドライクリーニングプロセス

【課題】 集積回路における酸化表面層の洗浄を行うための新しいドライクリーニングプロセスの提供。

【解決手段】 一の実施例によると、当該方法は、酸化表面層を有する金属含有バリア層を含む基板を供する工程、前記酸化表面層を活性化させるために、プラズマ励起されたアルゴン気体を含む第1処理気体流へ前記酸化表面層を曝露する工程、及び、前記の第1処理気体流へ酸化表面層を曝露する工程中に基板バイアス電力を印加する工程を有する。当該方法は、非プラズマ励起された水素気体を含む第2処理気体へ前記の活性化した酸化表面層を曝露する工程をさらに有する。前記の第1処理気体流へ酸化表面層を曝露する工程は、前記酸化表面層を活性化させるのに加えて、水素気体を含む前記第2処理気体による、前記活性化した酸化表面層の還元を助ける。前記金属含有バリア層の厚さは、ハイブリッドその場ドライクリーニングプロセスによって実質的には変化しない。

(もっと読む)

半導体装置およびその製造方法

【課題】グラフェンのバリスティック伝導性を利用した低抵抗配線を備え、配線と配線接続部材の接続部分の構成の複雑化を抑えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、基板と、基板の上方に設けられ、積層された複数のグラフェンナノリボンシート122からなるグラフェンナノリボン層121を含む下層配線12と、複数のグラフェンナノリボンシート122の少なくとも1枚を貫通し、下層配線12と上層配線13とを接続するビア14およびバリアメタル15と、を有する。

(もっと読む)

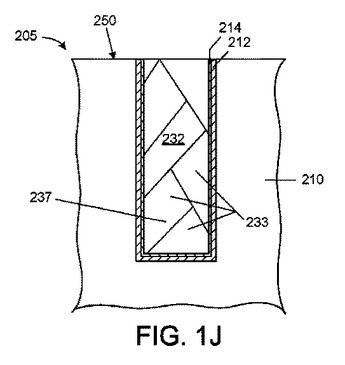

切欠構造のなかで長尺状ルテニウム膜上に多段階式銅鍍金を行う方法。

先端の集積回路にみられる切欠構造(206,207,208,209,211,213,264,275a,275b)において、長尺のルテニウム金属膜(214)に多段階で銅鍍金を行う方法である。長尺のルテニウム金属膜 (214)を利用すると、銅金属がトレンチ(266)及びビア(268)のような高アスペクト比の切欠構造(206,207,208,209,264,275a,275b)を充填するあいだ、不要な微細気泡が形成を防ぎ、前記ルテニウム金属膜(214)上に長尺の銅金属層(228)を含むサイズの大きい銅粒(233)が鍍金形成される。銅粒(233)は銅が充填された切欠構造(206,207,208,209,211,213,275a,275b)の電気抵抗を低下させ、集積回路の信頼性を向上させる。  (もっと読む)

(もっと読む)

電極コンタクト構造、自己走査型発光素子アレイ

【課題】オーミック接触を実現する電極コンタクト構造を提供する。

【解決手段】電極コンタクト構造は、エピタキシャル層100と、エピタキシャル層100上に形成されたコンタクトメタル電極120と、コンタクトホールを有する層間絶縁膜140と、コンタクトメタル電極120上に形成された第1のAl配線160と、第1のAl配線160上に形成された拡散障壁層180と、拡散障壁層180上に形成された第2のAl配線200を有する。電極コンタクト構造は、自己走査型発光素子アレイのカソード電極やゲート電極の構造として用いられる。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、埋込導体構造の密着性とCu拡散防止能を両立する。

【解決手段】 半導体基板上に設けた絶縁膜に設けた埋込導体用の凹部内に埋め込まれたCuまたはCuを最大成分とする合金からなるCu系埋込導体層と、前記凹部に露出する前記絶縁膜との間にCoを最大成分とするとともに、少なくともMn、O及びCを含むCoMn系合金層を設ける。

(もっと読む)

半導体装置及びその製造方法

【課題】自己整合的にバリア膜を形成する配線構造の信頼性を向上できるようにする。

【解決手段】半導体基板の上に酸素及び炭素を含む層間絶縁膜11を形成し、該層間絶縁膜11に溝部13を形成し、溝部13の底面上及び側壁上に所定の第1の金属元素及び第2の金属元素を含む補助膜14を形成し、熱処理を行い、銅を主成分とする配線本体層19を、溝部13の内部を埋め込むように形成する。熱処理を行うことにより、補助膜14中の第1の金属元素を補助膜14と対向する層間絶縁膜11に拡散させ、溝部13の底面及び側壁における層間絶縁膜11の上において、第1の金属元素と層間絶縁膜11の酸素元素との化合物を主成分とする第1のバリア膜15を形成させた後、補助膜14中の第2の金属元素が補助膜14と対向する層間絶縁膜11に拡散させ、第2の金属元素と層間絶縁膜11の炭素元素との化合物を主成分とする第2のバリア膜17を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】信頼性の高い半導体装置を実現する構造およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板(半導体基板1)上に、シラン化合物およびポロジェンを含む膜(有機シリコンポリマー膜2)を設ける工程と、選択的エッチングにより有機シリコンポリマー膜2に孔(配線溝3)を設けるとともに、配線溝3の内部に金属膜(バリア膜4および銅配線5)を設ける工程と、還元ガス雰囲気中で、上記ポロジェンの沸点または分解温度以上の温度で加熱しつつ、有機シリコンポリマー膜2に紫外線6を照射して、多孔質膜7を得る工程と、を含むものである。

(もっと読む)

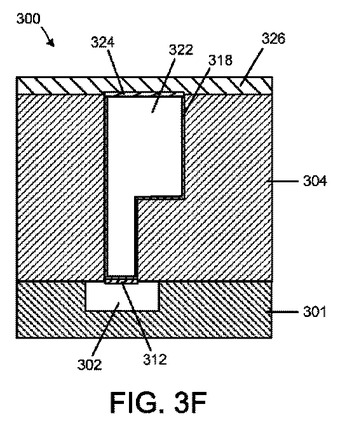

半導体装置及び半導体装置の製造方法

【課題】バリアメタルの被覆性を向上させる。

【解決手段】本発明の半導体装置は、キャップ絶縁膜1d上に形成された絶縁膜と、絶縁膜に形成された配線溝と、配線溝の底面に形成されたビア孔と、少なくともビア孔の側壁を覆うバリアメタル膜と、を有する。ビア孔は、径が異なる複数の孔から構成されており、複数の孔は、下に向けて径が小さくなるように深さ方向に接続し、複数の孔の接続部にキャップ絶縁膜に対してほぼ平行な面を有する。

(もっと読む)

電気的接続構造の製造方法

【課題】 低抵抗の電気的接続構造を提供する。

【解決手段】 ビアホールの底部の導電体上に導電性触媒担持体層を設け、予め微粒子化した触媒微粒子を当該導電性触媒担持体層上に堆積し、その後リフトオフ法により前記ビアホール底部以外の前記触媒粒子を除去して触媒微粒子層となし、当該触媒微粒子層上に炭素細長構造体を設ける電気的接続構造の製造方法において、前記触媒微粒子が、Co、Ni、Feからなる群から選ばれた金属の微粒子であること。

(もっと読む)

配線構造体の製造方法及び配線構造体

【課題】 横方向(基板表面に平行な方向)にカーボンナノチューブを成長させるためには、側壁に平坦かつ微小な表面を持つ触媒膜を形成する必要がある。ところが、このような触媒膜を形成することは困難である。

【解決手段】 基板表面の相互に離隔した2つの縦配線領域に、第1の厚さの縦配線用触媒膜を形成し、1つの縦配線領域から他の縦配線領域まで連続する横配線領域に、第1の厚さよりも厚い第2の厚さの横配線用触媒膜を形成する。縦配線用触媒膜及び横配線用触媒膜の上に、カーボンを含む構造体を気相成長させる。気相成長の初期段階には、縦配線用触媒膜及び横配線用触媒膜の上にグラファイトが形成され、その後、縦配線領域の前記グラファイトと基板との間にカーボンナノチューブが成長し、横配線領域の前記グラファイトが、縦配線領域に成長したカーボンナノチューブによって中空に支持されるように第1の厚さ及び第2の厚さが設定されている。

(もっと読む)

配線構造及びその形成方法、並びに半導体装置

【課題】炭素元素からなる線状構造体を有する接続部の更なる低抵抗化を実現して、更なる接続部の微細化を可能とする。

【解決手段】ビア孔28a内を充填し、配線溝32aの内壁面を覆うように、例えば超臨界CVD法により、ビア孔28a内におけるCNT28d間の空隙及びCNT28dの中空内を導電材料34で埋め込み、ビアプラグ33と、ビアプラグ33上で配線溝32aの内壁面を覆う下地膜32bとを同時形成する。

(もっと読む)

ルテニウム金属キャップ層を形成する方法

ルテニウム(Ru)金属の堆積を半導体デバイスの製造に統合することで、銅(Cu)金属のエレクトロマイグレーション及びストレスマイグレーションを改善する方法が供される。本発明の実施例は、NHx(x≦3)ラジカル及びHラジカルによって、金属層及びlow-k誘電材料を含むパターニングされた基板を処理することで、前記low-k誘電材料に対する前記金属層上でのRu金属キャップ層の選択形成を改善する方法を有する。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】基板に発生する応力を低減できる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体素子が形成される素子領域を有する基板と、素子領域の隣接部分の基板に形成されるビアホールと、ビアホール内に絶縁層を介して設けられる導通部と、基板と絶縁層との間に設けられる緩衝層とを備え、緩衝層は、基板の熱膨張係数と緩衝層の熱膨張係数との差が、基板の熱膨張係数と絶縁層の熱膨張係数との差より小さい材料から形成される。

(もっと読む)

1 - 20 / 89

[ Back to top ]