Fターム[5F033KK13]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 金属及びその合金(シリサイドを除く) (9,842) | Au、Au合金 (399)

Fターム[5F033KK13]に分類される特許

121 - 140 / 399

半導体装置

【課題】大量生産上、大型の基板に適している半導体装置を提供する。

【解決手段】ゲート電極と、チャネルを含む島状半導体層と、島状半導体層上に形成されたドレイン配線およびソース配線とを有し、島状の半導体層は、In−Ga−Zn−Oを含み、ドレイン配線及びソース配線は島状半導体層をキャリアの移動方向と垂直に横断し、チャネルの長さはドレイン配線およびソース配線の間隔に等しいことを特徴としている。

(もっと読む)

半導体装置及びその製造方法

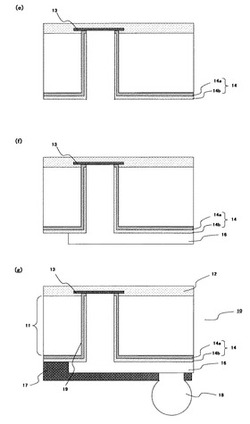

【課題】貫通孔(接続孔)内に形成された絶縁膜上に設けられる配線層と半導体基板との間の電気的絶縁性の不良の発生が低減された半導体装置の製造方法を提供する。

【解決手段】半導体基板11の一方の面上に第1の絶縁層12を介して位置する第1の配線層13と、半導体基板の他方の面から第1の配線層に至る接続孔19を形成する。接続孔の側面から他方の面に亘って半導体基板上に位置し、接続孔内で第1の配線層に接する第2の絶縁層14を形成する。接続孔の側面上から他方の面上に亘って第2の絶縁層上に位置し、接続孔内で第1の配線層に接する第2の配線層16を形成する。この形成において、第2の絶縁層を、膜質の異なる2種の絶縁膜14a、14b又はそれ以上の絶縁膜の積層体から構成する。

(もっと読む)

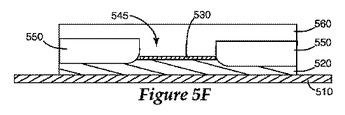

エレクトロマイグレーション耐性を有するビア・ライン相互接続体

【課題】 エレクトロマイグレーション耐性を有するビア・ライン間相互接続構造体及びその製造方法を提供する。

【解決手段】 導電性ビアの上層金属ライナと、下方の金属ラインの下層金属ライナとの間に、ライナ・ライナ間接触を形成する。ライナ・ライナ間接触は、急激なエレクトロマイグレーションによる故障を抑制し、金属相互接続構造体のエレクトロマイグレーション耐性を強化する。少なくとも1つの誘電体材料部分は、上層金属ライナと下層金属ライナの間の直接接触を保証するように配置された複数の誘電体材料部分を含むことができる。代替的に、少なくとも1つの誘電体材料部分は、リソグラフィ・オーバーレイ変動の許容範囲内でライナ・ライナ間直接接触が形成されるのを保証するのに十分な、導電性ビア領域との横方向の重なりを有する領域の単一の誘電体部分を含むことができる。

(もっと読む)

半導体装置

【課題】水分の浸入による半導体装置の信頼性低下を抑制した装置の提供。

【解決手段】GaAs系半導体、InP系半導体、及びGaN系半導体のいずれかからなる半導体層2と、半導体層2上に設けられ、端部4aが半導体層2上に位置する第1窒化シリコン膜4と、第1窒化シリコン膜4の端部4aを覆うように、半導体層2上及び第1窒化シリコン膜4上に設けられたポリイミドまたはベンゾシクロブテンのいずれかからなる保護膜12と、半導体層2の上面及び第1窒化シリコン膜4の端部4aに接するように、半導体層2と保護膜12との間から第1窒化シリコン膜4の端部4aと保護膜12との間にかけて連続的に設けられた第1Ti層14と、を具備することを特徴とする半導体装置。

(もっと読む)

フォトセンサ及び表示装置

【課題】マトリクス状に配置した光電変換素子が捉える光の強度分布を、再現よく電気信号に変換して取り出せる大型のエリアセンサおよび、エリアセンサを搭載した書き込み速度が速く、表示ムラが少ない表示装置を提供する。

【解決手段】インジウム、ガリウム、および亜鉛を含む酸化物半導体を用いた薄膜トランジスタは、大面積基板にマトリクス状に配置することが容易であり、また特性にバラツキが少ない。インジウム、ガリウム、および亜鉛を含む酸化物半導体を用いた薄膜トランジスタで構成した特性にバラツキが少ない増幅回路と表示素子の駆動回路を用いて、マトリクス状に配置したフォトダイオードが捉える光の強度分布を再現よく電気信号に変換して取り出し、マトリクス状に配置した表示素子をムラなく駆動する。

(もっと読む)

半導体装置

【課題】窒化シリコン膜と電極パッドとの界面から水分が浸入することを抑制し、半導体装置の信頼性を向上させること。

【解決手段】半導体層2と、半導体層2上に設けられたAuからなる電極パッド10と、電極パッド10上にその端部が位置するように、半導体層2上及び電極パッド10上に設けられた窒化シリコン膜6と、電極パッド10の上面の一部及び窒化シリコン膜6の端部に接し、かつ電極パッド10の上面の他部が露出するように設けられたTi、Ta及びPtのいずれかからなる金属層14と、を具備する半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】複数の半導体チップを多数積層した半導体装置において、生産性を損なうことなく高性能化する。

【解決手段】シリコン基板1の主面s1上に順に形成された複数の素子、層間絶縁膜2およびパッド3と、パッド3に電気的に接続するバンプ電極4と、シリコン基板1の裏面s2に形成され、バンプ電極4に電気的に接続する裏面電極6とを有する半導体装置である。バンプ電極4は、パッド3を貫通し、シリコン基板1側に向かって突出するような突出部d1を有する。また、裏面電極6は、シリコン基板1の裏面s2側から主面s1側に向かって、バンプ電極4の突出部d1に達し、パッド3には達しないような裏面電極用孔部7の内側を覆うようにして形成されていることで、バンプ電極4と電気的に接続されている。

(もっと読む)

陽極酸化された薄膜構造用の電気的接続

第1の薄膜メタライゼーション層と第2の薄膜メタライゼーション層とを電気的に接続する回路ビアの形成のための手法が述べられる。ビアの形成では、第1のメタライゼーション層の陽極酸化に先立って、ビア接続領域に配置される陽極酸化バリア及び/又は補助パッドを使用する。バリアを形成するために使用される材料は、陽極酸化の際に陽極酸化液を実質的に透過せず、導電層とバリアとの間に酸化物が形成されることを阻止するものである。補助パッドは非陽極酸化性であり、陽極酸化の際に、パッドを通じて電流が流れることを実質的に防止するためにバリアによって覆われる。陽極酸化の後に、バリアは除去される。補助パッドが充分な導電性を有する場合には、バリアの除去後に第1のメタライゼーション層上に残存されてもよい。第2のメタライゼーション層が陽極酸化層上に配置され、ビア接続領域において第1の導電層と電気的に接触する。  (もっと読む)

(もっと読む)

半導体装置

【課題】モールドストレスによる絶縁ゲート型電界効果トランジスタの特性変動を抑制する。

【解決手段】半導体基板上に設けられた絶縁ゲート型電界効果トランジスタと、前記絶縁ゲート型電界効果トランジスタと離間し、前記絶縁ゲート型電界効果トランジスタを取り囲むように前記半導体基板の表面に設けられ、前記絶縁ゲート型電界効果トランジスタのボディと同じ導電型の高不純物濃度層と、前記絶縁ゲート型電界効果トランジスタ及び前記高不純物濃度層上の一面に、前記絶縁ゲート型電界効果トランジスタを覆うように設けられ、ビア及び下層配線を介して前記高不純物濃度層と電気的に接続される最上層配線とを具備することを特徴とする半導体装置が提供される。

(もっと読む)

積層半導体装置及び積層半導体装置の製造方法

【課題】動作の安定した積層半導体装置を提供する。

【解決手段】単結晶シリコンのベース部と、ベース部の上の絶縁層と、絶縁層の上の単結晶シリコン層と、単結晶シリコン層に形成され絶縁層に達する分離溝構造と、分離溝構造で囲まれた単結晶シリコン層のボディ領域と、ボディ領域に形成されるトランジスタと、少なくともベース部および絶縁層を貫通し、ボディ領域に電気的に結合する貫通結合部とを有する第1半導体装置と、貫通結合部に接する外部接続部を有する第2半導体装置と、を備え、第2半導体装置は、貫通結合部を介して第1半導体装置のボディ領域の電位を制御する。

(もっと読む)

半導体装置及びその製造方法

【課題】 高アスペクト比の貫通電極を有する半導体装置を低温プロセスによって製造する。

【解決手段】 半導体基板1の表面側に配置された第1の電極3と裏面側の第2の電極6は、接続孔4に充填された導電物7と、接続孔4内に延在する第2の電極6の延在部6aとによって電気的に接続される。接続孔4が高アスペクト比であっても、第2の電極6を接続孔4の底部まで形成する代わりに導電物7を用いることで、低温プロセスによる成膜が可能となる。

(もっと読む)

集積回路デバイスのヒューズ構造

【課題】 集積回路デバイスのヒューズ構造を提供する。

【解決手段】 本発明のヒューズ構造は、半導体基板の一部の上に配置された金属含有導電性材料のストリップを含み、ストリップは、第1方向に沿って延伸し、均一な線幅を有する。誘電体層は、導電層を覆う。誘電体層内は、第1ビアと第2ビアを有し、第1インターコネクトと第2インターコネクトをそれぞれ含む。第1インターコネクトは、ストリップ上の第1位置と物理的且つ電気的に接触しており、第2インターコネクトは、ストリップ上の第2位置と物理的且つ電気的に接触している。導電ストリップ上の第1と第2位置は、シリコンを含まない。誘電体層の上方は、第1インターコネクトに電気的に接続された第1配線構造と、第2インターコネクトに電気的に接続された第2配線構造である。

(もっと読む)

半導体装置の製造方法

【課題】孔のないキャリア(支持基板)を用いても、キャリアの取り外し時の半導体チップの散乱を防止することができる半導体装置の製造方法を提供する。

【解決手段】半導体素子が形成された素子形成基板の表面に、接着剤11を用いてキャリア(支持基板)12を貼り付ける。その後、素子形成基板の裏面から、素子形成基板の途中まで延びる複数のスルーホール1bを互いに離間して形成する。次に、裏面の処理として、裏面の研磨及びAu層23の形成等を行う。次に、複数のスルーホール1bを接着剤11まで到達させる。そして、複数のスルーホール1bから接着剤11の溶解液を接着剤11まで浸透させて、接着剤11を溶解させる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置及びその製造方法において、半導体装置の収量を増加させると共に、製造工程の簡略化を図る。

【解決手段】半導体基板10の表面における所定の領域内に複数のパッド電極12を形成した後、半導体基板10の表面に接着剤層14を介して支持体15を貼り合わせる。次に、半導体基板10であって上記所定の領域と重畳する領域に開口部10Aを形成する。そして、開口部10A内で各パッド電極12と電気的に接続された配線層18を形成する。その後、所定の工程を経て、最後に、半導体基板10及び支持体15を含む積層体を、開口部10Aの外側に延びるダイシングラインDLに沿ってダイシングする。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタの製造方法、薄膜トランジスタアレイ及び画像表示装置

【課題】溶剤乾燥や熱硬化のための熱処理工程を用いずに形成した欠陥の少ない絶縁層を有する薄膜トランジスタ、薄膜トランジスタの製造方法、薄膜トランジスタアレイ及び画像表示装置を提供すること。

【解決手段】バンプ107と、バンプ107により貫通される層間絶縁層105とを含む薄膜トランジスタにおいて、バンプ107がフッ素化合物を含み、層間絶縁層105がフィルム状ホットメルト接着剤の加熱圧着により形成され、バンプがフッ素化合物を含み、フッ素含有量が、0.01wt%以上5wt%以下であることを特徴とする薄膜トランジスタ。

(もっと読む)

半導体装置

【課題】絶縁体に蓄積した電荷が放電を起こすことにより、アンテナ又は薄膜トランジスタを有する回路を破壊してしまう問題(静電気破壊の問題)を解決することを目的とする。

【解決手段】第1の絶縁体と、前記第1の絶縁体上に設けられた薄膜トランジスタを有する回路と、前記回路上に設けられ、前記回路と電気的に接続されたアンテナと、前記アンテナ上に設けられた第2の絶縁体と、を有し、前記第1の絶縁体と前記回路との間に第1の導電膜が設けられ、前記第2の絶縁体と前記アンテナとの間に第2の導電膜が設けられる。

(もっと読む)

ウェハの金属材料埋込装置及びウェハの金属材料埋込方法

【課題】 容易に貫通穴を埋めることができ、環境負荷を小さくする。

【解決手段】 貫通穴が設けられたウェハの貫通穴の開口の径が小さい側の主面を把持し、前記貫通穴の開口の径が大きい側から貫通穴に金属材料を埋め込むウェハの金属材料埋込装置であって、枠状に形成される第一の吸引部と、貫通穴から金属材料を吸引し第一の吸引部に嵌め込まれる第二の吸引部とを有する把持本体部と、第一の吸引部に沿って形成され、流路と吸引穴と第三の貫通孔とが形成されたアダプター部と、吸引穴に接続される吸引手段と、吸引配管の流量と圧力とを検出する検出手段と、金属材料が吸引されて変化した流量と圧力の値が所定の値となっているか否かを判定する判定手段と、所定の値であると判定された場合に把持本体部で吸引しているウェハからはみ出て入る金属材料を所定の加圧平面に押し当てる加圧手段と、第三の貫通孔接続される吐出手段と、を備えて構成される。

(もっと読む)

ウェハの金属材料埋込装置及びウェハの金属材料埋込方法

【課題】 容易に貫通穴を埋めることができ、環境負荷を小さくする。

【解決手段】 テーパ状の貫通穴を有するウェハの貫通穴の開口の径が小さい側の主面を把持し、貫通穴の開口の径が大きい側から、貫通穴に球状の金属材料を埋め込むウェハの金属材料埋込装置であって、ウェハの表面を吸引把持する第一の吸引部と、ウェハの貫通穴から金属材料を吸引する第二の吸引部とを有する把持本体部と、第一の吸引部と第二の吸引部とに配管を介して接続される吸引手段と、配管を流れる流体の流量と圧力とを検出する検出手段と、金属材料が吸引されて貫通穴を塞ぐことで変化した流量と圧力の値が所定の値となっているか否かを判定する判定手段と、判定手段によって値が所定の値であると判定された場合に把持本体部で吸引している前記ウェハからはみ出て入る金属材料を所定の加圧平面に押し当てる加圧手段と、を備えて構成される。

(もっと読む)

半導体装置の作製方法

【課題】絶縁膜中にコンタクトホールを形成せずに、絶縁膜の表面と裏面の間に導電領域を形成することを課題とする。

【解決手段】基板上の半導体素子及び第1の電極上に絶縁膜を形成し、絶縁膜中に第1の加速電圧で第1のイオンを添加して、絶縁膜中の第1の深さに第1の欠陥の多い領域を形成し、第1の加速電圧とは異なる第2の加速電圧で、第2のイオンを添加して、絶縁膜中の第1の深さとは異なる第2の深さに第2の欠陥の多い領域を形成し、第1及び第2の欠陥の多い領域上に、金属元素を含む導電材料を形成し、第1及び第2の欠陥の多い領域のうちの上方の領域から下方の領域に、金属元素を拡散させることにより、絶縁膜中に、第1の電極と、金属元素を含む導電材料とを電気的に接続する導電領域を形成する半導体装置の作製方法に関する。

(もっと読む)

半導体装置

【課題】別々の配線から電源電力が供給される半導体素子が形成された互いに独立した複数のウェルを配線の延設方向に沿って隣り合わせて配置することを可能とする。

【解決手段】半導体基板20の第1ウェル領域22に形成された複数の半導体素子の少なくとも一部に電源電力を供給する第1配線36と、第1配線36上に形成された第1絶縁層46と、半導体基板20の第1ウェル領域22とは独立している第2ウェル領域24に形成された複数の半導体素子の少なくとも一部に電源電力を供給する第2配線38と、を設け、第1配線36と第2配線38とを第1絶縁層46によって電気的に絶縁する。

(もっと読む)

121 - 140 / 399

[ Back to top ]