Fターム[5F033KK13]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 金属及びその合金(シリサイドを除く) (9,842) | Au、Au合金 (399)

Fターム[5F033KK13]に分類される特許

141 - 160 / 399

半導体装置及びその製造方法

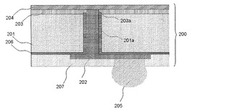

【課題】半導体基板に形成される貫通孔底部での絶縁層のノッチの発生、貫通孔下の配線層へのダメージを抑制し、電気的絶縁性の低下や配線層の接続不良を低減できる半導体装置及びその製造方法を提供する。

【解決手段】第一の絶縁層203と、第一の絶縁層上の第一の配線層204と、半導体基板201を貫通し、底部に第一の絶縁層を厚さ方向に除去した部分的なエッチ部を備えた貫通孔201aと、貫通孔の部分的なエッチ部の底部を除く内壁部から半導体基板の第二の面までを覆う第二の絶縁層206と、貫通孔の底部に、第一の配線層が露出するように第一の絶縁層に形成された開口部203aと、該開口部で第一の配線層と接すると共に貫通孔の第二の絶縁層上から半導体基板の第二の面の第二の絶縁層上に亘る第二の配線層202とを有し、開口部に接する第一の絶縁層が、半導体基板に接する第一の絶縁層より小さい厚さを有する。

(もっと読む)

半導体装置、その半導体装置の製造方法及びパワーモジュール

【課題】絶縁層を厚くして電極間の寄生容量を低く抑えることができ、かつ、当該絶縁層に精度良く開口部を形成して作製される小型の半導体装置、その半導体装置の製造方法、及びその半導体装置を含むパワーモジュールを提供する。

【解決手段】セル160は、基板104と、基板104上に形成されるドレイン電極180、ソース電極182、及びゲート電極184と、基板104及び各電極上に形成され、ドレイン電極180の表面を露出する開口部220が形成された絶縁層142とを含む。開口部220は、ドレイン電極180の表面から絶縁層142の表面に向かってその径を広げながら所定高さまで立上がる壁面222と、基板104の表面から当該所定高さで基板104の表面に平行となった踊り場状の平坦面224と、平坦面224から絶縁層142の表面に向かってその径を広げながら立ち上がる壁面226とを有する。

(もっと読む)

半導体装置の製造方法

【課題】Alを含む金属配線の形成において、サイドエッチ量を低減した微細な金属配線を形成でき、金属配線上に形成するビアホールが金属膜を突き抜けるのを抑制することができる半導体装置の製造方法を提供する。

【解決手段】基板上に第一TiN膜3、Alを含む金属膜4、第二TiN膜5を順次積層した金属配線層6を形成する工程と、前記金属配線層6の上にストッパー膜7、シリコン酸化膜8を順次積層したハードマスク層12を形成する工程と、前記ハードマスク層12を選択的にエッチングして前記金属配線層6の上にハードマスク12aを形成する工程と、前記ハードマスク12aをマスクとしてエッチングし金属配線6aを形成する工程と、前記ハードマスク12aおよび前記金属配線6aの上に層間絶縁膜14を形成する工程と、前記ストッパー膜7をエッチングストッパとして前記層間絶縁膜14にビアホール17aを形成する工程とを含む。

(もっと読む)

耐性評価用ウェハ及び耐性評価方法

【課題】 外部からの荷重による絶縁膜の耐圧力を短時間かつ正確に評価することができる耐性評価用ウェハ及び耐性評価方法を提供するものである。

【解決手段】 耐性評価用ウェハ100は、基板1上にlow−k絶縁膜2を介して対向して配設される一対の第1の配線3及び第2の配線4と、一対の配線のうち第1の配線3に第1のビア5を介して接続され、最上層に配設される第1の接続パッド6と、一対の配線のうち第2の配線4に第2のビア7を介して接続され、最上層に配設される第2の接続パッド8と、基板1に対して垂直な方向における第1の配線3及び第2の配線4の一部に重畳し、low−k絶縁膜2を介して最上層に電気的に浮遊状態で平面端子として複数配設され、所定の荷重で押圧される押圧パッド9と、を備えている。

(もっと読む)

トランジスタアクティブ基板およびその製造方法並びに電気泳動ディスプレイ

【課題】活性層を保護するとともにドレイン電極と画素電極との電気的導通を十分確保できるような保護層を設けたトランジスタアクティブ基板を提供する。

【解決手段】トランジスタアクティブ基板は、基板301、ゲート電極302、ゲート絶縁膜303、ソース電極304、ドレイン電極305および活性層306から構成される薄膜トランジスタ上に、保護膜307および画素電極308が配置されており、ドレイン電極305の表面粗さをRa(M)、保護膜307の膜厚をD(I)としたときに、D(I)≦Ra(M)×15の関係にある。

(もっと読む)

TFTアレイ基板の製造方法

【課題】簡単な工程で画素電極とコンタクトホールとを形成するTFTアレイ基板の製造方法を提供する。

【解決手段】絶縁膜を成膜する工程と、絶縁膜の上に導電膜を成膜する工程と、導電膜をパターニングして開口が設けられた画素電極を形成する工程と、開口が設けられた画素電極をエッチングマスクとしてエッチング法により絶縁膜に開口と連通するコンタクトホールを形成する工程と、を有することを特徴とするTFTアレイ基板の製造方法。

(もっと読む)

パターン形成方法

【課題】無駄を省いた状態で、所望とする微細なパターンに電着による膜が形成できるようにする。

【解決手段】まず、容器151内に電着液152を収容し、電着液152の中で、白金からなる対向電極153に基板101の金属パターン104形成面を対向させて配置する。この状態で、定電圧源154により、対向電極153に正電圧を印加し、シード層102に負電圧を印加する。ここで、金属パターン105に必要な配線を接続することで、シード層102に対する負電圧の印加を行う。このようなカチオン電着により、金属パターン104および金属パターン105の露出している面(上面)に、電着液152中の電着成分が付着(析出)し、電着絶縁膜106が形成される。

(もっと読む)

半導体装置とその製造方法

【課題】半導体基板の表裏両面間を貫通電極で接続するにあたって、貫通孔底部の角部におけるリーク電流の発生や絶縁膜のクラック等を抑制する。

【解決手段】半導体装置1は貫通孔3を有する半導体基板2を備える。貫通孔3は半導体基板2の第1の面2aに開口された第1の開口3aの開口径が第2の面2bに開口された第2の開口3bに近い側の内径より大きくなるように、第1の面2aの近傍を拡張させる拡張部4を備える。半導体基板2の第1の面2aには第1の絶縁層5と第1の配線層6とが設けられている。貫通孔3には拡張部4を充填しつつ内壁面を覆う第2の絶縁層7が設けられており、さらに第1および第2の絶縁層5、7の開口を介して第1の配線層6と接続された第2の配線層8が設けられている。

(もっと読む)

半導体装置

【課題】電極の断線が生じても動作可能であり、かつ大電力で動作することが可能な、小型の半導体装置を提供する。

【解決手段】セル160は、六角形の素子形成領域を画定する開口部を形成するように形成されたソース電極182と、素子形成領域に、ソース電極182と一定距離を隔てて帯状に形成されたドレイン電極180と、ソース電極182とドレイン電極180との双方から所定の距離を隔てて形成されたゲート電極184とを含む。ゲート電極184の各辺の中央部分からソース電極182に重畳するようにゲート引出電極186を形成し、ゲート引出電極186とソース電極182との間には絶縁膜を形成する。

(もっと読む)

電子デバイス及びその製造方法

【課題】層間絶縁膜に形成した空隙部を導電材料で充填して配線・接続部を形成する際に問題となる、下層の導電領域と配線・接続部との接続状態に起因する不都合を生ぜしめることなく、微細な配線及び接続部が所望の状態に正確且つ容易に実現されてなる信頼性の高い電子デバイスを実現する。

【解決手段】ダミー構造物16を形成し、ダミー構造物16の側面のみに側壁膜17を形成する。このダミー構造物16を覆うように層間絶縁膜18を形成する。そして、側壁膜17が残るようにダミー構造物16のみを除去し、下層配線14の表面の一部を露出させ、層間絶縁膜18に形成された開口18aをCuで埋め込み、Cuの表層を層間絶縁膜18の表面に合わせて平坦化する。以上により、下層配線14と直接的に接続されるCu接続部22を形成する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】配線材との密着性が良く、バリア性の高い金属膜をもつ半導体装置、およびその製造方法を提供する。

【解決手段】基板上に絶縁膜、金属からなるバリアメタル膜、及びCu配線金属膜がこの順で積層された積層構造を具備してなり、バリアメタル膜の酸化物のX線回折測定による回折強度が、バリアメタル膜とCu配線金属膜との化合物の回折強度の10倍以下である。

(もっと読む)

半導体装置及びその製造方法

【課題】後工程の熱によるクラックの発生を抑制し、製造歩留り及び製品品質を向上する。

【解決手段】GaAs基板10(基板)の表面上にソース電極12(表面電極)が形成されている。GaAs基板10の裏面からソース電極12に達するようにビアホール18が形成されている。GaAs基板10の裏面上及びビアホール18内にストレス緩和層20が形成されている。GaAs基板10の裏面上及びビアホール18内に、ストレス緩和層20を介して、Auメッキ22が形成されている。ストレス緩和層20は、線膨張係数が6×10−6〜14×10−6/Kの金属材料からなる。

(もっと読む)

半導体装置とその製造方法

【課題】 ヘテロ接合を有する半導体装置において、素子領域から電流がリークすることを抑制する。

【解決手段】 半導体装置100は、バンドギャップを異にする窒化物半導体層6、10が積層されている半導体積層部11を有しており、半導体積層部11が素子領域100aと素子領域100aの周囲に形成されている素子分離領域100bを備えている。素子領域100aは、素子分離領域100bにより他の領域から絶縁されている。半導体装置100は、素子領域100a内の半導体積層部11の表面に、主電極に接続する一対の電極群24,16を形成する電極群形成工程と、素子分離領域100b内の半導体積層部11の表面に、スパッタ法を用いてスパッタ層12を形成するスパッタ工程を備えている。

(もっと読む)

半導体装置

【課題】ビアホールに起因し基板に生じる亀裂を抑制し、かつチップ面積を削減することが可能な半導体装置を提供すること。

【解決手段】本発明は、長方形の基板10と、楕円形状または直線部分をその長軸方向に有するトラック形状からなり、その長軸が基板10の長辺方向に沿って配置されてなるビアホール12と、を具備することを特徴とするである。本発明によれば、ビアホールに起因した基板に生じる亀裂を抑制し、かつチップ面積を削減することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】細く深いバイアホールが設けられる場合でも、ソースインダクタンスを十分に低減し、高い放熱効率を得ることができる半導体装置及びその製造方法を提供する。

【解決手段】SiC基板1上に化合物半導体領域2を形成し、その後、化合物半導体領域2上にゲート電極4g、ソース電極4s及びドレイン電極4dを形成し、更に、化合物半導体領域2上にソース電極4sに接続されるAu膜10を形成する。次に、SiC基板1の裏面にレーザビームを照射して、SiC基板1、化合物半導体領域2及びAu層を貫通するバイアホール21を形成する。次に、バイアホール21の側面及びSiC基板1の裏面にわたってビア配線14を形成する。次に、バイアホール21内に溶融金属滴32を充填し凝固させることにより、導通ビアを形成する。そして、溶融金属滴32を充填する際に、SiC基板1を溶融金属滴32に対して相対的に振動させる。

(もっと読む)

半導体装置、ウエハ構造体および半導体装置の製造方法

【課題】微細プロセスよりも前に個片化用の溝を形成した場合でも、微細プロセスにおけるフォトリソグラフィで使用するフォトレジストを均一に形成することを可能にする。

【解決手段】配列された複数の素子形成領域AR1を含むp型半導体層103における隣り合う素子形成領域AR1間に平行な2つの溝TRを形成し、個片化時には2つの溝TRの間に形成された凸部120を切断する。この構成により、スクライブ領域SR全体に溝TRを形成する必要が無くなるため、溝TRの幅を例えばダイシングブレードの厚さやレーザスポットの径よりも小さくすることが可能となる。この結果、微細プロセスよりも前に個片化用の溝を形成した場合でも、微細プロセスにおけるフォトリソグラフィで使用するフォトレジストを均一に形成することが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極の周囲に形成される空洞と保護膜に形成されるホールとの境界部分の開口を封止しやすい構造を実現する。

【解決手段】半導体装置を、ゲート電極3と、高さが低い部分6Aと高さが高い部分6Bとを有する階段状の空間6をゲート電極3の周囲に有する保護膜4と、高さが低い部分6Aに接するように保護膜4に形成されたホール5とを備えるものとする。

(もっと読む)

半導体装置、通信モジュールおよび電子機器

【課題】安定した利得が得られるアンテナ素子を備えた半導体装置、通信モジュールおよび電子機器を提供すること。

【解決手段】半導体装置10は、能動素子が形成された能動面1aを有する半導体基板1と、能動面1a上に少なくとも1層以上の絶縁性樹脂層を介して設けられた第1の配線層8と、第1の配線層8に形成されたスロットアンテナ11と、スロットアンテナ11に接続された共振用キャパシタ13とを備え、スロットアンテナ11は、矩形状の開口部11bを有する平面型のアンテナ素子である。

(もっと読む)

積層構造体、半導体装置、積層構造体の製造方法及び半導体装置の製造方法

【課題】密着性ガードリングを有する積層構造体及び半導体装置を提供する。

【解決手段】基板上において、エネルギーを付与することにより臨界表面張力が変化し、低表面エネルギー状態から高表面エネルギー状態へと変化する材料を含むものであって、エネルギーの付与により、高表面エネルギー領域と、低表面エネルギー領域とが形成されている濡れ性変化層と、濡れ性変化層の高表面エネルギー領域上に形成された導電層と、導電層を覆うように形成された絶縁層を有し、基板上に形成された濡れ性変化層において、導電層が複数形成される回路形成領域の周囲を囲むように、高表面エネルギー領域が形成され、高表面エネルギー領域上に絶縁層を形成することにより、濡れ性変化層と絶縁層との間に密着性ガードリング領域が形成されていることを特徴とする積層構造体を提供することにより上記課題を解決する。

(もっと読む)

配線構造、半導体装置及び半導体装置の製造方法

【課題】 高周波信号の伝達も含めた配線抵抗を低減することができると共に、良好な遮蔽導体として機能する配線構造及びその配線構造を有する半導体装置を提供する。

【解決手段】 複数の配線層にそれぞれ設けられた配線1,3が互いに重複し、互いに電気的に複数層に亘り並列接続された配線構造であって、複数の配線層の少なくとも下層の一つの配線層が、少なくとも2本以上の並列配線に分離されて延伸しているスリット配線部を有し、上層の配線3からスリット配線部の並列配線の間隙に浸入して両側の並列配線と接続しているスリット接続部2aを有する配線構造とする。

(もっと読む)

141 - 160 / 399

[ Back to top ]