Fターム[5F033KK15]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 金属及びその合金(シリサイドを除く) (9,842) | Co、Co合金 (187)

Fターム[5F033KK15]に分類される特許

121 - 140 / 187

表示装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な表示装置及びその作製技術を提供することを目的とする。

【解決手段】光吸収層を形成し、光吸収層上に絶縁層を形成し、光吸収層及び絶縁層に選択的にレーザ光を照射し、光吸収層の照射領域及び絶縁層の照射領域を除去し光吸収層及び絶縁層に開口を形成し、開口に光吸収層と接するように導電膜を形成する。露出した光吸収層と接するように開口に導電膜を形成することによって、光吸収層及び導電膜は絶縁層を介して電気的に接続することができる。

(もっと読む)

表示装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な表示装置及びその作製技術を提供することを目的とする。

【解決手段】光吸収層を形成し、光吸収層上に絶縁層を形成し、光吸収層及び絶縁層に選択的にレーザ光を照射し、絶縁層の照射領域を除去し絶縁層に開口を形成し、開口に光吸収層と接するように導電膜を形成する。露出した光吸収層と接するように開口に導電膜を形成することによって、光吸収層及び導電膜は絶縁層を介して電気的に接続することができる。

(もっと読む)

表示装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な表示装置及びその作製技術を提供することを目的とする。

【解決手段】光吸収層を形成し、光吸収層上に絶縁層を形成し、光吸収層及び絶縁層に選択的にレーザ光を照射し、絶縁層の照射領域を除去し絶縁層に第1の開口を形成し、第1の開口を有する絶縁層をマスクとして光吸収層を選択的に除去し、絶縁層及び光吸収層に第2の開口を形成し、第2の開口に光吸収層と接するように導電膜を形成する。露出した光吸収層と接するように第2の開口に導電膜を形成することによって、光吸収層及び導電膜は絶縁層を介して電気的に接続することができる。

(もっと読む)

半導体装置および多層配線基板

【課題】低比誘電率の熱ビアを提供し、もって層間絶縁の低誘電率化と高熱伝導率化を同時に実現することができる多層配線基板および半導体装置を提供する。

【解決手段】多層配線構造の第1の配線層101と第2の配線層102との間に比誘電率が平均して2.5以下の気体または絶縁物を介在させるとともに、第1の配線層101における配線と第2の配線層102における配線との間に所望の導電接続体を設け、さらに第1の配線層101における所定の配線と第2の配線層102における所定の配線との間に比誘電率が5以下の絶縁物熱伝導体を設ける。

(もっと読む)

表示装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な表示装置及びその作製技術を提供することを目的とする。また、それらの表示装置を構成する配線等のパターンを、所望の形状で制御性よく形成できる技術を提供することも目的とする。

【解決手段】導電層を形成する際、形成したいパターンの外側(パターンの輪郭、端部に相当する)に液状の導電性材料を含む組成物を付着させ、枠状の第1の導電層(又は絶縁層)を形成する。枠状の第1の導電層の内側の空間を充填するように、液状の第2の導電性材料を含む組成物を付着させ第2の導電層を形成する。第1の導電層及び第2の導電層は接して形成され、第2の導電層の周囲を囲むように第1の導電層が形成されるので、第1の導電層及び第2の導電層は連続した一つの導電層として用いることができる。

(もっと読む)

表示装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な表示装置及びその作製技術を提供することを目的とする。また、それらの表示装置を構成する配線等のパターンを、所望の形状で制御性よく形成できる技術を提供することも目的とする。

【解決手段】マスク層を形成する際、形成したいパターンの外側(パターンの輪郭、端部に相当する)に液状のマスク層形成材料を含む組成物を付着させ、枠状の第1のマスク層を形成する。枠状の第1のマスク層の内側の空間を充填するように、液状の第2のマスク層形成材料を含む組成物を付着させ第2のマスク層を形成する。第1のマスク層及び第2のマスク層は接して形成され、第2のマスク層の周囲を囲むように第1のマスク層が形成されるので、第1のマスク層及び第2のマスク層は連続した一つのマスク層として用いることができる。

(もっと読む)

半導体装置

【課題】 本発明は、同一基板上に同時に異なるLDD構造を有する生産性の高いTFTの作製方法およびその構造を提供することを目的としている。即ち、本発明はTFTの新規な構造と生産性の高い製造工程を提供するものである。

【解決手段】 耐熱性の高いTa膜またはTaを主成分とする膜を配線材料に用い、さらに保護層で覆うことで、高温(400〜700℃)での加熱処理を施すことが可能となり、且つ保護層をエッチングストッパーとして用いることで周辺駆動回路部においては、サイドウォール126を用いた自己整合プロセス(セルフアライン)によるLDD構造を備えたTFTを配置する一方、画素マトリクス部においては、絶縁物125を用いた非自己整合プロセス(ノンセルフアライン)によるLDD構造を備えたTFTを配置する

(もっと読む)

半導体装置およびその製造方法

【課題】高集積化、微細加工化等の技術が今後進展した場合であっても、消費電力を低く抑えることのできるDRAM等の半導体装置およびその製造方法を提供すること。

【解決手段】半導体基板1と、前記半導体基板1に形成されたトランジスタ100と、前記トランジスタ100と電気的に接続されている容量コンタクトである第一の電気素子3と、前記第一の電気素子と電気的に接続されている容量素子である第二の電気素子400と、を有する半導体装置であって、 前記第一の電気素子3と前記第二の電気素子400とは、前記第一の電気素子3と前記第二の電気素子400との双方を通る前記半導体基板表面と平行な平面aーa、bーbが少なくとも二つ存在する様に接続されていることを特徴とする半導体装置。

(もっと読む)

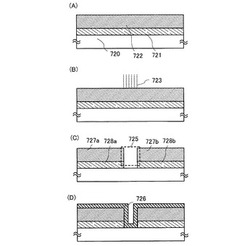

半導体装置の製造方法

【課題】犠牲層残渣の発生や配線細りなどの不具合を抑制する、エアギャップ構造を有する半導体装置の製造方法を提供する。

【解決手段】基板1上に複数の配線を形成する半導体装置の製造方法であって、基板1上に、複数の配線と、複数の配線に対して選択してエッチングできる金属からなり、複数の配線の間隙に埋め込まれている犠牲層とを形成する工程と、犠牲層を複数の配線に対して選択比を有するエッチングにより除去して、複数の配線の間隙にエアギャップ構造を形成する工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】高い信頼性を有する半導体装置と、当該半導体装置を歩留まり良く製造する方法とを提供する。

【解決手段】半導体装置の製造方法は、第1の層間絶縁膜1に埋め込まれ、上面に第1のキャップメタル6が設けられた配線材料膜5を形成する工程(a)と、配線材料膜5の上方に設けられた第2の層間絶縁膜8に溝10およびビアホール9を形成する工程(b)と、溝10およびビアホール9の内面にバリアメタル11を形成する工程(c)と、ビアホール9の底部に位置するバリアメタル11の部分と配線材料膜5および第1のキャップメタル6の一部とを除去する工程(d)と、配線材料膜5の上面に第2のキャップメタル21を形成する工程(f)とを備える。配線材料膜5の上面に酸素との結合力が強い金属の酸化膜が形成される場合でも、当該金属の酸化物は工程(d)で除去できる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】DRAMメモリセル形成時の熱処理による負荷を低減させ、メモリセルおよびこれと同一基板上に形成されるMISFETの特性を向上させる。

【解決手段】メモリセル形成領域に、情報転送用MISFETQsとキャパシタCからなるメモリセルが形成され、論理回路形成領域に、論理回路を構成するnチャネル型MISFETQnとpチャネル型MISFETQpとが形成される半導体集積回路装置の、キャパシタCが形成される酸化シリコン膜41を、450℃〜700℃の温度で、プラズマCVD法を用いて形成する。その結果、酸化シリコン膜41からの脱ガス量を低減でき、脱ガスによってキャパシタCの下部電極43を構成するシリコン膜表面のシリコン粒の成長が阻害されず、容量を大きくすることができ、また、酸化シリコン膜41の成膜後に、水分等を除去するための熱処理工程を省くことができ、MISFETの特性の劣化を防止することができる。

(もっと読む)

固体及び気体誘電体の組み合わせによって離間された相互接続した導電性配線及びビアを含む多層相互接続構造を形成する方法、及び、空隙を含む複数レベルの相互接続構造(空隙を含む多層相互接続構造及びその製造方法)

【課題】本発明は、空隙を含む複数レベルの相互接続構造及びその製造方法を提供する。

【解決手段】空隙を含む複数レベルの相互接続構造は、散在したライン・レベル及びビア・レベルの集合を含み、ビア・レベルは、1つ以上の誘電体層に埋め込まれた導電性ビアを含み、ビア・レベルの誘電体層は、隣接レベルのライン機構の上下に位置する固体であり、ライン機構の間でミシン目が入れられている。ライン・レベルは導電性ラインと、空隙を含む誘電体とを含む。導電性接点を含み、有孔誘電体層内に充填することによって形成された固体誘電性ブリッジ層は、散在したライン及びビア・レベルの集合上に配置されている。

(もっと読む)

膜パターンの形成方法、アクティブマトリクス基板の製造方法、デバイス、電気光学装置、及び電子機器

【課題】製造コストの低減に寄与する製造方法を提供する。

【解決手段】基板18上に設けられたバンク34によって区画されたパターン形成領域に

、機能液を配置して膜パターンを形成する。基板18上に第1のバンク形成材料を配置し

て第1バンク層35を形成する工程と、第1バンク層35上に第2バンク層36を形成す

る工程とを有する。第1のバンク形成材料は有機材料であり、第2バンク層36は第1バ

ンク層35を被覆するフッ素系の樹脂材料からなる。

(もっと読む)

半導体装置

【課題】バイポーラトランジスタにおける高利得化および低雑音化を同時に実現できる技術を提供する。

【解決手段】ベースパッド31およびコレクタパッド32の下部にエミッタ(基準(接地)電位)と電気的に接続された配線24が設けられた基板シールド構造とすることにより、ベースパッド31およびコレクタパッド32と配線24との間では容量が設けられた構造として電力消費をなくし、基板1からの熱雑音は、配線24を介して基準(接地)電位へと逃がし、ベースパッド31およびコレクタパッド32へは届かないようにする。

(もっと読む)

半導体集積回路装置

【課題】SRAMのメモリセルの蓄積ノード容量を増やしてソフトエラー耐性を向上させる。

【解決手段】6個のMISFETでメモリセルを構成した完全CMOS型のSRAMにおいて、メモリセルの駆動用MISFETQd1,Qd2、転送用MISFETQt1,Qt2および負荷用MISFETQp1,Qp2のそれぞれのゲート電極を構成する第1導電層の上層に形成した高融点金属シリサイド層でCMOSインバータの相互の入出力端子間を接続する一対の局所配線L1,L2を形成し、この局所配線L1,L2の上層に形成した基準電圧線を局所配線L1,L2と重なるように配置して蓄積ノード容量素子を形成する。局所配線L1,L2の一方は、この蓄積ノード容量素子の一方の電極を構成する。

(もっと読む)

障壁冗長構成要素を有する相互接続構造体および相互接続構造体を形成する方法

【課題】障壁冗長構成要素を有する相互接続構造体と、相互接続構造体を形成する方法とを提供する。

【解決手段】導電性ライン20の部分の上にバイア拡散障壁30が存在する。導電性ライン20の上で障壁30がない部分に存在する導電性材料54は、導電性ライン拡散障壁22とバイア拡散障壁30との間の電気的経路を提供する。従って、導電性材料54、導電性ライン拡散障壁22およびバイア拡散障壁30を用いて、内部障壁冗長構成要素が形成される。障壁冗長構成要素によって提供されるこの電気的経路によって、バイア底部のEM不良から生じる突然の回路開放を回避することができる。従って、監視デバイスによってEM不良が検出された後、チップ交換またはシステム操作調節のために十分な時間を提供する障壁冗長構成要素が相互接続構造体に提供される。

(もっと読む)

半導体装置及びその製造方法

【課題】プロービング時にもクラックが発生しにくいパッド構造を持つ半導体装置を提供する。

【解決手段】半導体基板の上に形成された第1の絶縁膜に凹部が形成されている。凹部内に導電部材が充填されている。第1の絶縁膜及び導電部材の上に第2の絶縁膜が形成されている。凹部の上方の、第2の絶縁膜の表面上にパッドが形成されている。平面視において、凹部の外周線よりも内側に、凹部の底面から突出し、絶縁材料で形成された複数のピラーが配置されている。ピラーの各々の平面形状は、角部に曲率半径0.2μmよりも大きな丸みを付した多角形である第1の形状、90°よりも大きな内角のみからなる多角形である第2の形状、曲率半径0.2μm以上の湾曲部のみからなる曲線で囲まれた第3の形状、及び該第1〜第3の図形の外周線の一部同士を滑らかに接続した連続線で囲まれた第4の形状のいずれかである。

(もっと読む)

半導体装置

【課題】ラッチアップ防止用のガードリングにシリサイドを形成しつつ、ESDサージによってそのガードリングが破壊されないようにする。

【解決手段】ラッチアップ防止用の第2ガードリング71の表面において、トランジスタ形成領域20と対向する側には幅W3だけシリサイドを形成しない構造とする。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜の誘電率を上昇させるダメージを受けた領域の除去量を適正化することで除去領域への絶縁膜の埋め込み性を改善するとともに配線間の絶縁膜の低誘電率化を図って、配線信頼性の向上を図る。

【解決手段】基板上に第1絶縁膜11を形成した後に前記第1絶縁膜11に対して選択的にエッチングされる犠牲膜12を形成する工程と、前記犠牲膜12と前記第1絶縁膜11に凹部(第1配線溝13)を形成する工程と、前記第1配線溝13内にバリア膜14を介して導電体(第1配線16)を形成する工程と、前記犠牲膜12を前記第1絶縁膜11に対して選択的にエッチングして除去する工程と、前記犠牲膜の除去領域17を埋め込むように前記第1絶縁膜11上に第2絶縁膜18を形成する工程とを有することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】エアギャップ構造において酸化に起因する配線信頼性劣化を抑制することができる半導体装置およびその製造方法を提供する。

【解決手段】本実施形態に係る半導体装置は、基板1上に形成された第1配線5と、第1配線5の上層に形成され、第1配線5との間にエアギャップ20を介在させて配置された第2配線16と、エアギャップ20内に形成され、第1配線5と第2配線16とを接続するカーボンナノチューブ11とを有する。

(もっと読む)

121 - 140 / 187

[ Back to top ]