Fターム[5F033KK15]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 金属及びその合金(シリサイドを除く) (9,842) | Co、Co合金 (187)

Fターム[5F033KK15]に分類される特許

141 - 160 / 187

半導体装置

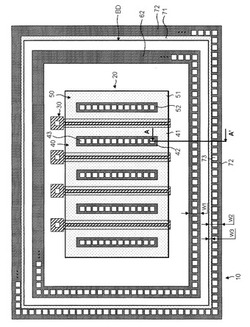

【課題】ラッチアップ防止用のガードリングにシリサイドを形成しつつ、ESDサージによってそのガードリングが破壊されないようにする。

【解決手段】ラッチアップ防止用の第2ガードリング71の表面において、トランジスタ形成領域20と対向する側には幅W3だけシリサイドを形成しない構造とする。

(もっと読む)

アライメントマークおよびアライメントマークの製造方法

【課題】ビアファーストデュアルダマシンプロセスを用いた半導体装置の製造における、配線マスク工程で使用するアライメントマークの視認性を高める。

【解決手段】アライメントマークを不透明な金属や金属化合物を含んで形成し、アライメントマークのパターン開口領域と非開口領域とに色彩が相違して視認される材料を配置することにより、高い視認性のアライメントマークを得ることが可能で、マスク工程の合わせずれを低減させ、デバイスの歩留まりおよび信頼性を向上することができる。

(もっと読む)

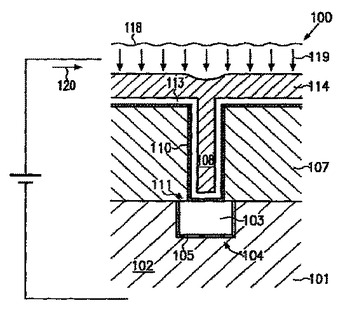

低抵抗及び低インダクタンスの裏面貫通ビア及びその製造方法

【課題】 低抵抗及び低インダクタンスの裏面貫通ビア及びその製造法

【解決手段】 裏面コンタクト構造体及びその構造体を製造する方法を提供する。この方法は、表面及び対向する裏面を有する基板(100)内に誘電体分離(250)を形成するステップと、基板(100)の表面上に第1誘電体層(105)を形成するステップと、誘電体分離(250)の周囲上及び内部に位置合せされ、誘電体分離(250)まで延びるトレンチ(265C)を第1誘電体層(105)内に形成するステップと、第1誘電体層(105)内に形成されたトレンチ(265C)を、誘電体分離(250)を貫通して基板(100)の厚さより小さな深さ(D1)まで基板(100)内部に延ばすステップと、トレンチ(265C)を充填し、且つトレンチ(265C)の上面を第1誘電体層(105)の上面と同一平面にして、導電性貫通ビア(270C)を形成するステップと、基板(100)の裏面から基板(100)を薄くして貫通ビア(270C)を露出させるステップとを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】ビア・配線間の重ね合わせがずれた場合にもTDDBを抑制できる半導体装置およびその製造方法を提供する。

【解決手段】順次積層された絶縁膜1,2内に形成された溝11内には、バリアメタル3およびCuからなる配線4が埋め込まれている。配線4上にはメタルキャップ9が配置され、メタルキャップ9上には、絶縁膜5,6が順次積層されている。絶縁膜5,6内に形成された溝14内には、バリアメタル7およびCuからなる配線8が埋め込まれている。この絶縁膜5は、Cuが拡散されないものとする。バリアメタル7は、ビア・配線間の重ね合わせにおいて位置ずれが生じた場合にも、メタルキャップ9には接触するが配線層21の絶縁膜2やバリアメタル3には接触しないように形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチ配線の配線幅のバラツキなく、デュアルダマシン構造を形成できる半導体装置及びその製造方法を提供する。

【解決手段】第1配線4が形成された層間膜1上に、第1配線4を覆うように絶縁膜6を形成した後、第1配線4上の絶縁膜6のみを除去する。そして、ビアホール及びトレンチを形成後、Cuの埋め込みによりビア18及び第2配線(トレンチ配線)26を形成する。ビアホール及びトレンチ形成前に第1配線4上の絶縁膜6が除去されているため、第2配線26を第1配線4と電気的に接続するための第1配線4上の絶縁膜6を除去する工程が必要ない。その結果、第1配線4上の絶縁膜6を除去する工程によって生じる第2配線26の配線幅のバラツキを抑制できる。

(もっと読む)

無電解フェーズと電流供給フェーズとを含むウェット化学堆積によりパターニングされた絶縁体上の金属層

無電解堆積および電気堆積プロセスをインサイチュで実行することによって、非常に信頼性のあるメタライゼーションが供給され、その際に、シード層を形成する、従来の化学気相堆積(CVD)、原子層堆積(ALD)ならびに物理気相堆積(PVD)技術にみられるような、汚染物質ならびにデバイススケーリングに関する欠点を克服することができる。ある実施例では、バリア層はさらに、ウェット堆積プロセスに基づいて堆積される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】特性にばらつきが生じることを抑制して歩留まりを向上させることができる半導体装置の製造方法を提供する。

【解決手段】半導体基板10上に膜40を形成するステップと、膜40上に、所定のパターンを有するマスクを形成するステップと、マスクを用いて、膜40又は半導体基板10にエッチングを行うステップと、第1級乃至第4級アミンのうちの少なくとも1つと、フッ素とを含む薬液によって処理を行うステップとを備える。

(もっと読む)

半導体集積回路装置の製造方法

【課題】空洞(Air−Gap)構造を有する多層のダマシン配線における目外れビアのメタル形成不良を防止する。

【解決手段】接続孔の形成領域に、選択的に除去可能な絶縁膜で犠牲膜ピラー42を形成した後に、隣接するダマシン配線間に空洞(Air−Gap)45を有する層間絶縁膜44を形成することで、ビアと空洞45を完全に分離する。

【効果】本発明によれば、信頼性の高いビア接続を有し、空洞による寄生容量の低減がなされた多層の埋込配線を形成することができる。

(もっと読む)

多層構造の形成方法

基板に電気化学エッチングまたは電気めっきを施すことにより多層構造を形成する方法。基板上にシード層を形成し、その上に主電極を形成する。主電極は、基板から複数の電気化学セルを形成するためのパターン層を有する。電圧が印加され、シード層がエッチングされて、またはシード層に材料がめっきされて形成された構造(8)の間に誘電体(9)が堆積される。誘電体層は下層構造を露出するために平坦化され、別の構造層が第1の構造層上に形成される。または、誘電体層は2層の厚さで形成され、下層構造の上端部を選択的に露出するために選択的にエッチングされる。また、複数の構造層を1工程で形成しても良い。 (もっと読む)

半導体装置およびその製造方法

【課題】 多層配線構造を含む半導体装置のマイグレーション耐性を高めて歩留まりを向上させる。

【解決手段】 半導体装置100は、半導体基板(不図示)上の第1の層間絶縁膜106中に設けられた第1の配線112と、第1の配線112上に、第1の配線112に接続して設けられたビア128と、第1の配線112の上部において、ビア128の底部との接続箇所に選択的に形成され、第1の配線112を構成する主成分の金属と当該金属と異なる異種元素とを含む異種元素含有導電膜114とを含む。

(もっと読む)

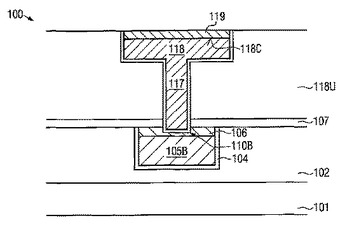

導電性キャッピング層を含む銅ベースのメタライゼーション層を形成する技術

金属ベースの相互接続線に対して導電性キャッピング層(106)を設けることで、エレクトロマイグレーションに対するパフォーマンスを強化することができる。さらに、銅ベースの材料などの下方の金属(105b)を露出せずにビア開口部(110)をキャッピング層(106)に確実にエッチングし、これによりエレクトロマイグレーションパフォーマンスを具体的には銅線とビアの間の遷移において強化することができる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】バリアメタルがない場合であっても、配線の平坦性を向上させることができる半導体装置の製造方法を提供する。

【解決手段】本実施例の半導体装置の製造方法は、半導体基板1上に層間絶縁膜2を形成し、層間絶縁膜2上に金属を含むメタルマスク3を形成し、メタルマスク3および層間絶縁膜2の一部をエッチングして、メタルマスク3および層間絶縁膜2にパターン溝2aを形成し、パターン溝2a内を埋め込むように、層間絶縁膜2上に導電層5を形成し、パターン溝2a内に導電層5を残すように、層間絶縁膜2上の余剰の導電層5を研磨する。

(もっと読む)

配線及びその形成方法と薄膜トランジスタ基板及びその製造方法

【課題】接着性が向上し、伝導性に優れた配線及びその形成方法とこれを用いて形成された薄膜トランジスタ基板及びその製造方法を提供する。

【解決手段】 配線は、酸化反応性金属またはシリサイド化反応性金属、及び銀を含む接着層と、前記接着層上に形成される銀導電層と、前記銀導電層上に形成され、前記酸化反応性金属及び前記銀を含んで形成される保護層とを有する。

(もっと読む)

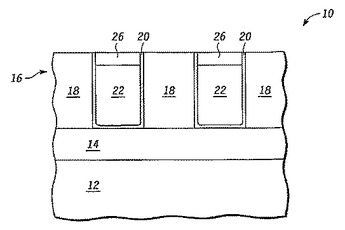

キャップ層を半導体素子の上に形成するための方法

半導体素子を形成する方法は、複数の空洞(15)を有するパターニング済み誘電体(18)を能動回路の上に形成する工程を含む。拡散バリア(20)をパターニング済み誘電体(18)の上に形成する。導電層(22)を複数の空洞の中の拡散バリアの上に形成する。導電層を、導電層が誘電体の上部表面の下方に位置するようにエッチバックして、後退領域(24)を、複数の空洞の中の導電層の上に形成する。次に、後退領域にキャップ膜(26)を充填する。キャップ膜及び拡散バリアを除去すると、非常に平滑な平坦化表面が得られる。非常に平滑な平坦化表面を形成することにより、複数の導体の間のリーク電流を低減する。  (もっと読む)

(もっと読む)

半導体装置

【課題】銅配線を覆って設けられるバリアメタル膜のバリア性能が向上されており、低比誘電率層間絶縁膜から放出されるガスによりバリアメタル膜が酸化されても、銅配線の信頼性や性能、および品質等が低下するおそれの殆ど無い半導体装置を提供する。

【解決手段】比誘電率が3以下である絶縁膜3が基板1上に少なくとも1層設けられている。少なくとも一部がこの絶縁膜3内に形成されている凹部10の内面を覆って第1のバリアメタル膜6が設けられている。この第1のバリアメタル膜6の表面を覆って凹部10内に第2のバリアメタル膜7が設けられている。この第2のバリアメタル膜7の表面を覆って凹部10内に第3のバリアメタル膜8が設けられている。この第3のバリアメタル膜8の表面を覆って凹部10内にCu膜11が埋め込まれて設けられている。

(もっと読む)

半導体装置

【課題】 埋込銅配線を有する半導体装置の信頼性を向上させる。

【解決手段】 絶縁膜14,15に配線溝を形成し、その配線溝の底面および側面上を含む絶縁膜15上に導電性バリア膜18と銅の主導体膜19を形成し、CMP法により不要な部分を除去して配線20を形成する。そして、主導体膜19上にタングステンからなる金属キャップ膜22を選択成長させてから、配線20を埋込んだ絶縁膜15上に絶縁膜23〜26を形成し、ビア30が金属キャップ膜22を貫通して主導体膜19を露出するようにビア30及び配線溝31を形成し、ビア30の底部で露出した主導体膜19上にタングステンからなる金属キャップ膜32を選択成長させた後に、ビア30および配線溝31の内部を含む絶縁膜26上に導電性バリア膜33と銅の主導体膜34を形成し、CMP法により不要な部分を除去して配線35を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】多層配線を有する半導体装置において、空孔率の高い配線間構造を用い、配線間の電気的短絡を抑制する。

【解決手段】基板上にそれぞれ同一レベルに備えられた第一および第二の配線層110、310と空孔率60%以上を有する第一および第二の空洞層120、320を有する配線構造において、第一および第二の空洞層120、320と接する配線層の側壁に第一および第二の酸化チタン層160、360からなる絶縁層を備え、配線層と接する側壁に第二および第四のチタン層150a、350aを備え、バリアメタル層と絶縁層の間に酸素バリア層として第一のおよび第二の窒化チタン層150b、350bを備えることにより、隣り合う配線間の電気的耐圧を向上し、配線間短絡を抑制する。

(もっと読む)

半導体装置およびその製造方法

【課題】 表面にキャップメタル膜が形成された銅配線を含む半導体装置において、ビア接続の歩留まりや抵抗の均一性を良好にする。

【解決手段】 本発明の半導体装置の製造方法は、半導体基板上に形成された絶縁膜に、配線溝を形成する工程(S100)と、絶縁膜上全面に、バリアメタル膜を形成する工程(S102)と、バリアメタル膜上全面に、配線溝内を埋め込むように銅膜を形成する工程(S104)と、絶縁膜表面に、バリアメタル膜が残る条件で、配線溝部外の銅膜を研磨により除去する工程(S106)と、銅膜を研磨により除去する工程の後に、配線溝部内に形成された銅膜上に、選択的にキャップメタル膜を形成する工程(S108)と、キャップメタル膜を研磨により平坦化する工程(S110)とを含む。

(もっと読む)

半導体装置の製造方法

【課題】銅の溝配線の上面バリア膜を形成するための触媒金属の置換めっきに起因する銅配線のエッチング損傷を容易に防止できる半導体装置の製造方法を提供する。

【解決手段】銅を含む配線上に銅拡散防止機能を有するバリア膜を有する半導体装置の製造方法であって、まず、基板に配線溝TR1を形成し、配線溝の内壁面にバリアメタル層16を堆積した後、上面バリア膜形成のための置換めっき用触媒金属17aを含むシード層を形成する。次に配線溝を埋め込んで全面に銅を含む金属層18を形成し、触媒金属を金属層中に熱拡散させ、触媒金属と合金化した金属層19とする。配線溝の外部における金属層19を除去して配線パターンに加工し、合金化された金属からなる配線を形成する。この後、配線の表面に銅拡散防止機能を有する上面バリア膜を置換めっきにより形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】薄膜トランジスタにおいて、ソース/ドレイン領域へのコンタクトの方法を改良することにより、配線抵抗を減らす。

【解決手段】ガラス基板上に第1の絶縁膜、島状の結晶性珪素膜、ゲイト絶縁層、ゲイト電極、第1の配線、ゲイト電極及び第2の絶縁膜を形成し、第2の絶縁膜及びゲイト絶縁層をエッチングしてゲイト電極及び第1の配線の側面に側壁を形成するとともに、島状の結晶性珪素膜のソース領域及びドレイン領域を露出し、ゲイト電極、第1の配線、側壁、島状の結晶性珪素膜及び第1の絶縁膜上に金属層を形成し、ソース領域及びドレイン領域と、金属層とを反応させて島状の結晶性珪素膜の側面から上面にわたって密着したシリサイド層を形成し、金属層をエッチングして、ソース領域又はドレイン領域の一方のシリサイド層と第1の配線とを接合する第2の配線を形成する。

(もっと読む)

141 - 160 / 187

[ Back to top ]