Fターム[5F033KK17]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 金属及びその合金(シリサイドを除く) (9,842) | 高融点金属 (3,578)

Fターム[5F033KK17]の下位に属するFターム

Fターム[5F033KK17]に分類される特許

1 - 20 / 342

薄膜トランジスタアレイおよびその製造方法、並びに表示装置

【課題】配線密度を高くしすぎることなく断線を修復することが可能であり、フレキシブル性を持たせる場合に短絡や断線などを抑えることが可能な薄膜トランジスタアレイおよびその製造方法、並びに表示装置を提供する。

【解決手段】第1導電層と、前記第1導電層の少なくとも一部に対向して、前記第1導電層に合わせた平面形状の開口を有する絶縁膜と、前記開口を塞ぐと共に前記開口内で前記第1導電層に接するパッチ部を含む第2導電層とを備えた薄膜トランジスタアレイ。

(もっと読む)

配線構造及びそれを備える薄膜トランジスタアレイ基板並びに表示装置

【課題】透明導電膜上における絶縁膜の膜浮きの発生を抑え、且つ、透明導電膜と金属膜との良好な電気的接続性を得ることができる配線構造を提供する。

【解決手段】それぞれ配線として機能する第1の導電膜2と第2の導電膜5と接続する配線変換部45において、第2の導電膜5の内側には刳り抜き部13が形成される。第2の導電膜5の上に設けられる第2の導電膜5は、第2の導電膜5の上面および刳り抜き部13に露出した端面を覆い、且つ、第2の導電膜5の外周の端面を覆わないように形成される。第1の透明導電膜6の上層の第2の透明導電膜7が、第2の導電膜5と第1の導電膜2とに接続することにより、第1の導電膜2と第2の導電膜5とが電気的に接続される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子上の配線層の設計自由度に優れた半導体装置を提供する。

【解決手段】半導体装置は、基板、層間絶縁層、第1トランジスタ、多層配線層、容量素子、金属配線、及び第1コンタクトを備える。基板1上には、層間絶縁層4、5が設けられている。第1トランジスタ3aは、半導体基板1に設けられており、層間絶縁層内に埋め込されている。第1トランジスタは、少なくともゲート電極32及び拡散層を有する。層間絶縁層上には、多層配線層が設けられている。容量素子19は、多層配線層内に設けられている。金属配線(ゲート裏打ち配線)30は、ゲート電極32の上面と接しており、層間絶縁層4内に埋設されている。第1コンタクト10aは、第1トランジスタ3aの拡散層に接続しており、層間絶縁層4内に埋設される。金属配線(ゲート裏打ち配線)30は、第1コンタクト10aと同じ材料で構成されている。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法

【課題】大型化に適した薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法を提供する。

【解決手段】フレキシブルな樹脂基板60に形成された薄膜トランジスタ200であって、周面の一部又は全部が導電性材料20により覆われたワイヤー10と、前記導電性材料を覆う絶縁膜30と、該絶縁膜を介して前記導電性材料上に形成された薄膜半導体40と、が一体的に構成されたゲート・チャネル一体形成部50を有し、該ゲート・チャネル一体形成部が前記樹脂基板の表面上又は内部の所定位置に設けられ、前記薄膜半導体の両側に第1及び第2の電極70、80が接続されて形成されたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】貫通電極を有する半導体装置の製造方法において、埋設導電部間のショートが起き難くすること。

【解決手段】半導体素子を有する素子領域と貫通電極が形成される貫通電極領域とを有する基板の上に第1絶縁膜を形成し、前記素子領域上の前記第1絶縁膜に凹部を形成し、前記貫通電極領域上の前記第1絶縁膜にダミー凹部を形成し、前記第1絶縁膜上、前記凹部内、および前記ダミー凹部内に第1導電材を形成し、前記第1導電材および前記第1絶縁膜の上部を研磨して、前記凹部内に導電部を形成すると共に前記ダミー凹部内にダミー導電部を形成し、前記貫通電極領域上の前記第1絶縁膜および前記貫通電極領域をエッチングして前記基板内に至る貫通電極ホールを形成した後、前記貫通電極ホール内に第2導電材を形成し、前記貫通電極ホール内に形成された第2導電材が露出するまで前記基板の裏面を研磨して、前記貫通電極を形成すること。

(もっと読む)

半導体磁気記憶装置

【課題】磁気記憶素子を構成する層を、周辺回路部内で有効に活用する。

【解決手段】実施形態によれば、半導体磁気記憶装置は、セルトランジスタを含むセル部と、周辺トランジスタを含む周辺回路部とが形成された半導体基板を備える。さらに、前記装置は、前記セル部内に配置され、下部電極と、前記下部電極上に形成された電極間層と、前記電極間層上に形成された上部電極とを含む磁気記憶素子を備える。さらに、前記装置は、前記周辺回路部内に配置され、前記下部電極を形成している第1の層と、前記電極間層を形成している第2の層と、前記上部電極を形成している第3の層とを含む構造体を備える。さらに、前記装置は、前記第1の層に電気的に接続された第1及び第2のプラグを備える。さらに、前記第1の層は、前記第1のプラグと前記第2のプラグを電気的に接続する配線として機能する。

(もっと読む)

半導体ウエハ及び半導体装置並びに半導体装置の製造方法

【課題】ダイシング工程におけるチッピング不良を低減させる。

【解決手段】一面側に複数の回路素子3が形成され、この回路素子が形成された領域間に第一スクライブライン領域R1が設けられたウエハ状の半導体基板2と、この半導体基板の他面2bから半導体基板の一面2aまで貫通する貫通孔7と、この貫通孔の内面及び半導体基板の他面側に形成された絶縁膜5と、この絶縁膜上に形成された配線6とを備えた半導体ウエハにおいて、半導体基板の他面側に形成された絶縁膜に、第一スクライブライン領域に沿って絶縁膜が離間した領域である第二スクライブライン領域R2が設けられている半導体ウエハを提供する。

(もっと読む)

半導体装置

【課題】酸化物半導体層を用いた表示装置に代表される半導体装置において、画面サイズの大型化や高精細化に対応し、表示品質が良く、安定して動作する信頼性のよい半導体装置を提供する。

【解決手段】引き回し距離の長い配線にCuを含む導電層を用いることで、配線抵抗の増大を抑える。また、Cuを含む導電層を、TFTのチャネル領域が形成される酸化物半導体層と重ならないようにし、窒化珪素を含む絶縁層で包むことで、Cuの拡散を防ぐことができ、信頼性の良い半導体装置を作製することができる。特に、半導体装置の一態様である表示装置を大型化または高精細化しても、表示品質が良く、安定して動作させること

ができる。

(もっと読む)

半導体装置とその製造方法

【課題】 実施形態は、製造工程が簡便な手法によって製造した半導体装置を提供することを目的とする。

【解決手段】 実施形態の半導体装置は、実施形態にかかる半導体装置は、基板と、基板上に触媒金属膜と、触媒金属膜上にグラフェンと、前記グラフェン上に層間絶縁膜と、前記層間絶縁膜を貫通するコンタクトホールと前記コンタクトホールにカーボンナノチューブを水素、窒素、アンモニアと希ガスの中から選ばれる1種以上のガスのプラズマで処理した前記触媒金属膜上に又は前記層間絶縁膜を貫通するカーボンナノチューブを水素、窒素、アンモニアと希ガスの中から選ばれる1種以上のガスのプラズマで処理した前記触媒金属膜上に備えることを特徴とする。

(もっと読む)

貫通配線の検査方法、貫通配線基板の製造方法

【課題】1つの貫通配線のみの抵抗を測定できる貫通配線の検査方法、及び該貫通配線の検査方法を行う工程を含む貫通配線基板の製造方法の提供。

【解決手段】基板1の一方の面1aに配された導電部2と、基板1を貫通し、導電部2と接続される第一貫通配線3、第二貫通配線4および第三貫通配線5とを少なくとも備えた貫通配線基板10を用い、基板1の他方の面1b側から第一貫通配線3及び第二貫通配線4に、定電流源6の一組の端子6a,6bを電気的に接続して、第一貫通配線3、導電部2、第二貫通配線4の経路に電流を流すと同時に、基板1の他方の面1b側から第一貫通配線3及び第三貫通配線5に、電圧計7の一組の端子7a,7bを電気的に接続して、第一貫通配線3における電圧降下を測定することを特徴とする貫通配線の検査方法。

(もっと読む)

半導体装置

【課題】層間絶縁膜のエッチングの際に半導体層がエッチングされることによるコンタク

ト抵抗の増大を防ぎ、書き込み特性及び電荷保持特性に優れた不揮発性半導体記憶装置及

びその作製方法を提供する。

【解決手段】ソース領域又はドレイン領域とソース配線又はドレイン配線との間に導電層

を設ける。また、該導電層は、制御ゲート電極を形成する導電層と同じ導電層からなる。

また、該導電層を覆うように絶縁膜が設けられており、該絶縁膜は該導電層の一部が露出

するコンタクトホールを有する。また、該ソース配線又はドレイン配線は、該コンタクト

ホールを埋めるように形成されている。

(もっと読む)

貫通配線基板および貫通配線基板の製造方法

【課題】貫通孔内に形成された導電層に加わる応力を抑制できるとともに、導電層からの効果的な放熱も促すことができる貫通配線基板、及びこの貫通配線基板の製造方法を提供する。

【解決手段】半導体基板11(基板)の一方の面11aに配された電極層12と、電極層12の少なくとも一部が露呈するように半導体基板11内に開けられた貫通孔20と、貫通孔20の内側面20aを覆い、電極層12の少なくとも一部が露呈するように配された第一絶縁層15と、第一絶縁層15を介して、貫通孔20の内側面20a及び電極層12の露呈部を覆うように配され、電極層12と電気的に接続された導電層5と、導電層5を覆うように配された第二絶縁層16と、を少なくとも備えてなる貫通配線基板10であって、第二絶縁層16は、導電層5の表面形状に沿って形成されていることを特徴とする。

(もっと読む)

集積回路装置の作製方法

【課題】薄膜回路の下方に外部と接続するための電極を容易に形成できる薄膜回路部品の

構造及び薄膜回路部品の作製方法を提供することを課題とする。

【解決手段】第1の絶縁膜と、第1の絶縁膜の一方の面上に形成された薄膜回路と、薄膜

回路上に形成された第2の絶縁膜と、第2の絶縁膜上に形成された電極と、電極上に形成

された樹脂膜とを有する積層物を形成し、積層物の第1の絶縁膜の他方の面側に、電極と

重なるように導電膜を形成し、導電膜にレーザーを照射する。

(もっと読む)

回路基板、回路基板の製造方法、表示装置および電子機器

【課題】被蒸着膜を高精細なパターンで形成することが可能な蒸着用マスクを提供する。

【解決手段】蒸着用マスクは、1または複数の第1開口部を有する基板と、この基板の一主面側に設けられると共に、各第1開口部と対向して1または複数の第2開口部を有する高分子膜とを備える。蒸着の際には、蒸着材料が第1開口部および第2開口部を順に通過することにより、第2開口部に対応した所定のパターンで被蒸着膜が形成される。基板と高分子膜とを組み合わせて用いることにより、機械的強度を保持しつつも、金属膜のみで構成されている場合に比べ、第2開口部において微細かつ高精度な開口形状を実現できる。

(もっと読む)

半導体装置の作製方法

【課題】信頼性が高く、ソースとドレインの間にリーク電流が生じにくく、コンタクト抵抗が小さい半導体装置を提供する。

【解決手段】酸化物半導体膜により形成されるトランジスタの電極膜上に酸化物半導体膜に接して設けられた第1の絶縁膜、及び第2の絶縁膜を積層して形成し、第2の絶縁膜上にエッチングマスクを形成し、エッチングマスクの開口部と重畳する部分の第1の絶縁膜及び第2の絶縁膜をエッチングして電極膜を露出する開口部を形成し、第1の絶縁膜及び第2の絶縁膜の開口部をアルゴンプラズマに曝し、エッチングマスクを除去し、第1の絶縁膜及び第2の絶縁膜の開口部に導電膜を形成し、第1の絶縁膜は加熱により酸素の一部が脱離する絶縁膜であり、第2の絶縁膜は第1の絶縁膜よりもエッチングされにくく、第1の絶縁膜よりもガス透過性が低い。または逆スパッタリングを行ってもよい。

(もっと読む)

半導体装置の製造方法

【課題】膜厚の厚い応力緩和層を有するウェハレベルCSPと称される半導体装置において、第1電極と外部電極との接続不良が発生しにくい半導体装置の製造方法を提供する。

【解決手段】(1)応力緩和層を半導体ウェハの上に形成する工程、(2)応力緩和層の一部を除去した開口部を形成し、半導体ウェハ上の第1電極を露出する工程、(3)第1電極と接続し、開口部を充填するポスト部を形成する工程、(4)外部電極とポスト部を接続するための再配線層を応力緩和層の上に形成する工程、(5)再配線層の上に再配線保護層を形成する工程、(6)再配線保護層の一部を除去して、外部電極を形成するための第2電極を露出する工程、(7)第2電極上に外部電極を形成する工程を含む半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】半導体層と電極の接続部に生じる寄生抵抗を抑制し、配線抵抗による電圧降下の

影響や画素への信号書き込み不良や階調不良などを防止し、より表示品質の良い表示装置

を代表とする半導体装置を提供することを課題の一つとする

【解決手段】上記課題を解決するために、本発明は酸素親和性の強い金属を含むソース電

極、及びドレイン電極と、不純物濃度を抑制した酸化物半導体層とを接続した薄膜トラン

ジスタと、低抵抗な配線を接続して半導体装置を構成すればよい。また、酸化物半導体を

用いた薄膜トランジスタを絶縁膜で囲んで封止すればよい。

(もっと読む)

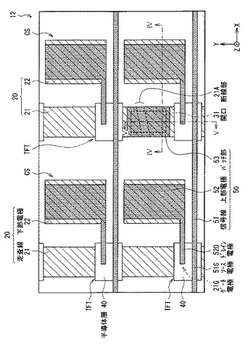

半導体装置およびその製造方法、並びに表示装置

【課題】3層以上の配線を接続する際に、最も効率的にかつ最小面積で接続を行えるコンタクト構造を実現可能な半導体装置およびその製造方法、並びに表示装置を提供する。

【解決手段】基板201上に3層以上のn層の導電層202〜204が積層して形成され、n層の導電層がコンタクトパターンを介して接続され、コンタクトパターンが形成される一つの主コンタクト領域には、(n−1)個の導電層202,203を接続する(n−1)個の接続領域211,212を有し、(n−1)個の導電層のうち基板201に対する積層方向(基板201の主面に対する法線方向)において第1層より上層の導電層は、その終端部がコンタクトパターンCPTNの縁の一部に臨むように形成され、(n−1)個の導電層は、第n層の導電層により電気的に接続されている。第n層の導電層は、コンタクトパターンCPTNであるコンタクト孔を埋めつくよう形成されている。

(もっと読む)

液晶表示装置及び液晶表示装置の作製方法

【課題】新規な電極構造を有する、横電界方式の液晶表示装置とその作製方法の提案。

【解決手段】絶縁表面を有する第1基板と、絶縁表面上の第1導電膜及び第2導電膜と、第1導電膜上の第1絶縁膜と、第2導電膜上の第2絶縁膜と、第1基板と対峙する第2基板と、第1基板と第2基板の間に位置する液晶層と、を有し、第1導電膜の一部は第1絶縁膜の側部にも位置し、なおかつ、第2導電膜の一部は第2絶縁膜の側部にも位置し、液晶層は、ブルー相を示す液晶を含んでいる液晶表示装置。

(もっと読む)

回路基板の製造方法

【課題】絶縁膜に形成されるヴィアホールの直径を縮小化することが可能で、高密度化に寄与することのできる回路基板の製造方法を提供する。

【解決手段】本発明の回路基板の製造方法は、基板10上に第1導電体を形成する第1導電体形成工程と、第1導電体を被覆する様にゲート絶縁膜21を成膜する第1絶縁膜成膜工程と、第1導電体上のゲート絶縁膜21に貫通孔32を開口して、当該貫通孔32を介して第1導電体の表面および基板の表面を部分的に露出させる貫通孔形成工程と、貫通孔32内に露出する第1導電体の表面を撥液化させる撥液化工程と、貫通孔32内に露出する第1導電体以外の領域に第2絶縁膜を形成する第2絶縁膜形成工程と、を含むことを特徴とする。

(もっと読む)

1 - 20 / 342

[ Back to top ]