Fターム[5F033KK23]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 金属及びその合金(シリサイドを除く) (9,842) | 高融点金属 (3,578) | 高融点金属の合金 (175) | TiW (132)

Fターム[5F033KK23]に分類される特許

1 - 20 / 132

銅を含む電極連結構造体

半導体チップ、これを含む半導体パッケージ、及びその製造方法

【課題】信頼性を向上させることができる高集積化された半導体チップ及びこれを含む半導体パッケージが提供される。

【解決手段】本発明にしたがう半導体チップは、基板と、前記基板を貫通している貫通ビアと、前記貫通ビアと前記基板との間に介在されたウェッティング膜と、前記ウェッティング膜と前記貫通ビアとの間に介在されたシード膜と、を含む。本発明の実施形態による半導体チップは突出された貫通ビアをウェッティング膜が覆っているので、導電パッドを追加に形成する必要がない。したがって、半導体チップの厚さを減らすことができ、構造が単純化されて半導体装置の高集積化により有利である。また、工程を単純化することができるので、生産収率を増大させ得る。

(もっと読む)

半導体ウエハ及び半導体装置並びに半導体装置の製造方法

【課題】ダイシング工程におけるチッピング不良を低減させる。

【解決手段】一面側に複数の回路素子3が形成され、この回路素子が形成された領域間に第一スクライブライン領域R1が設けられたウエハ状の半導体基板2と、この半導体基板の他面2bから半導体基板の一面2aまで貫通する貫通孔7と、この貫通孔の内面及び半導体基板の他面側に形成された絶縁膜5と、この絶縁膜上に形成された配線6とを備えた半導体ウエハにおいて、半導体基板の他面側に形成された絶縁膜に、第一スクライブライン領域に沿って絶縁膜が離間した領域である第二スクライブライン領域R2が設けられている半導体ウエハを提供する。

(もっと読む)

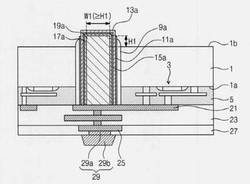

貫通配線基板および貫通配線基板の製造方法

【課題】貫通孔内に形成された導電層に加わる応力を抑制できるとともに、導電層からの効果的な放熱も促すことができる貫通配線基板、及びこの貫通配線基板の製造方法を提供する。

【解決手段】半導体基板11(基板)の一方の面11aに配された電極層12と、電極層12の少なくとも一部が露呈するように半導体基板11内に開けられた貫通孔20と、貫通孔20の内側面20aを覆い、電極層12の少なくとも一部が露呈するように配された第一絶縁層15と、第一絶縁層15を介して、貫通孔20の内側面20a及び電極層12の露呈部を覆うように配され、電極層12と電気的に接続された導電層5と、導電層5を覆うように配された第二絶縁層16と、を少なくとも備えてなる貫通配線基板10であって、第二絶縁層16は、導電層5の表面形状に沿って形成されていることを特徴とする。

(もっと読む)

貫通配線の検査方法、貫通配線基板の製造方法

【課題】1つの貫通配線のみの抵抗を測定できる貫通配線の検査方法、及び該貫通配線の検査方法を行う工程を含む貫通配線基板の製造方法の提供。

【解決手段】基板1の一方の面1aに配された導電部2と、基板1を貫通し、導電部2と接続される第一貫通配線3、第二貫通配線4および第三貫通配線5とを少なくとも備えた貫通配線基板10を用い、基板1の他方の面1b側から第一貫通配線3及び第二貫通配線4に、定電流源6の一組の端子6a,6bを電気的に接続して、第一貫通配線3、導電部2、第二貫通配線4の経路に電流を流すと同時に、基板1の他方の面1b側から第一貫通配線3及び第三貫通配線5に、電圧計7の一組の端子7a,7bを電気的に接続して、第一貫通配線3における電圧降下を測定することを特徴とする貫通配線の検査方法。

(もっと読む)

半導体装置の製造方法

【課題】信頼性を低下することなく、高集積化が可能な半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、薄膜抵抗体と配線層とが、接続層とビアホールに埋設されたタングステンプラグとを介して電気的に接続されてなる半導体装置の製造方法である。従来、接続層は、バリアメタル層を介して薄膜抵抗体と接続された構成である。この接続層としてアルミニウムを用いたものでは、接続層とタングステンプラグとの線膨張係数の差異に起因してストレスマイグレーションにより、接続層にボイドが発生する懸念があった。本発明では、接続層を除去する工程を実施し、タングステンプラグをバリアメタル層と直接接続する。これにより、タングステンプラグは、アルミニウムよりなる接続層を介することなく、薄膜抵抗体と電気的に接続される。したがって、接続層におけるボイドの発生を抑制し、半導体装置の接続信頼性を向上することができる。

(もっと読む)

半導体装置の製造方法

【課題】膜厚の厚い応力緩和層を有するウェハレベルCSPと称される半導体装置において、第1電極と外部電極との接続不良が発生しにくい半導体装置の製造方法を提供する。

【解決手段】(1)応力緩和層を半導体ウェハの上に形成する工程、(2)応力緩和層の一部を除去した開口部を形成し、半導体ウェハ上の第1電極を露出する工程、(3)第1電極と接続し、開口部を充填するポスト部を形成する工程、(4)外部電極とポスト部を接続するための再配線層を応力緩和層の上に形成する工程、(5)再配線層の上に再配線保護層を形成する工程、(6)再配線保護層の一部を除去して、外部電極を形成するための第2電極を露出する工程、(7)第2電極上に外部電極を形成する工程を含む半導体装置の製造方法。

(もっと読む)

配線基板、赤外線センサー及び貫通電極形成方法

【課題】基板と貫通電極との間で形成される浮遊容量が小さい基板を提供する。

【解決手段】第1面2aと第1面2aと対向する第2面2bとを貫通して開口するビアホール2cを有する基板2と、基板2の第1面2aに設置され熱酸化膜を含む第1絶縁膜3と、ビアホール2c内の面とに設置され熱酸化膜を含む第3絶縁膜5と、ビアホール2c内で第3絶縁膜5に囲まれた導電体7と、を有し、第1面2aにおける第1絶縁膜3の厚みに比べてビアホール2c内の面における第3絶縁膜5の厚みが厚くなっている。

(もっと読む)

能動領域ボンディングの両立性のある高電流構造体

【課題】ボンディング・パッド下方に各回路を有する集積回路。

【解決手段】一実施例において、集積回路は基板と、最上部導電層と、1つ以上の中間導電層と、絶縁材料から成る各層と、各デバイスとを具備する。最上部導電層は少なくとも1個のボンディング・パッド及び比較的硬質の材料から成る副層を有する。1つ以上の中間導電層は最上部導電層及び基板の間に形成する。絶縁材料から成る各層は各導電層を分離する。更に、絶縁材料から成る各層のうちの1つの層は比較的硬質で、最上部導電層及びこの最上部導電層に最も近接した中間導電層の間に位置する。各デバイスは集積回路に形成する。また、最上部導電層に最も近接した少なくとも中間導電層は、ボンディング・パッド下方の各選択デバイスの機能的相互接続部に対して適合する。

(もっと読む)

半導体装置の製造方法

【課題】水素又はカルボン酸を用いたリフロー時の導電部と絶縁層の密着力低下を抑制する。

【解決手段】半導体基板の上に設けられた第1導電部上に絶縁層を形成し(ステップS1)、その絶縁層を被覆するようにバリア層を形成した後(ステップS2)、そのバリア層の上に第2導電部を形成する(ステップS3)。そして、第1導電部上の絶縁層がバリア層で被覆されている状態で、第2導電部を水素又はカルボン酸を含む雰囲気中で溶融し(ステップS4)、その後、その第2導電部をマスクにして、絶縁層の上からバリア層を除去する(ステップS5)。

(もっと読む)

貫通配線基板の製造方法及び貫通配線基板

【課題】貫通孔の底面部付近において、導電層をカバレッジ良く形成し、接触不良がなく、電気的な安定性を向上させた貫通配線を、工程やコストを増加することなく形成する。

【解決手段】半導体基板の一方の面に第一絶縁層を介して導電部を形成する第一工程、ドライエッチング法により半導体基板の他方の面側から第一絶縁層が露呈するように貫通孔を形成する第二工程、貫通孔の内壁面および底面に第二絶縁層を形成する第三工程、第二絶縁層及び第一絶縁層のうち貫通孔の底面に位置する部分を除去し導電部を露呈する第四工程、第二絶縁層上に導電層を形成し該導電層を導電部と電気的に接続する第五工程、を有し、第四工程において、第二絶縁層に続いて導電部の一部をエッチングすると共に、エッチングにより除去された第一金属成分とエッチングガス成分とからなる第一副生成物を、貫通孔の底面部及びその近傍に位置する内壁面部に堆積させ、テーパー部を形成する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の配線間の容量低減を実現するとともに、ミスアライメント・ビアを対策する。

【解決手段】配線上及び配線間のスペース領域に絶縁膜74を形成し、隣接配線間隔が狭い配線の上面を露出するスルーホールの周辺領域の絶縁膜74をリザーバーとして残して、周辺領域以外の絶縁膜74を除去し、絶縁膜74が除去された配線間のスペース領域に空隙を残しつつ、配線上に絶縁膜77を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線の検査効率を向上させる。

【解決手段】複数の接続パッド12が設けられた半導体デバイスウエハ10と、半導体デバイスウエハ10の接続パッド12が設けられた面を被覆するとともに、接続パッド12を露出させる開口14aが設けられた絶縁膜14Aと、開口14aから露出された接続パッド12及び絶縁膜14Aの上部に設けられた配線15Aと、を備える半導体装置である。配線15Aは、無電解めっき用シード層16Aと、無電解めっき用シード層16Aを核とする無電解めっきにより形成される配線層19Aと、を含む。

(もっと読む)

半導体集積回路装置の製造方法

【課題】プラズマCVD法を用いてCu配線上に良好な拡散バリア膜を形成する技術を提供する。

【解決手段】ダマシン法を用いて形成したCu配線19上にCuの拡散を防止する窒化シリコン膜21を形成する工程は、Cu配線19が形成された基板1をプラズマCVD装置のチャンバ内に搬入し、基板1を所定の温度に加熱する工程と、チャンバ内にアンモニアを供給し、第1のRFパワーでアンモニアをプラズマ分解することによって、Cu配線19の表面を還元処理する工程と、RFパワーが印加された状態で、チャンバ内にアンモニアとモノシランとを含む原料ガスを供給し、第2のRFパワーでアンモニアとシラン系ガスとをプラズマ分解することによって、Cu配線19上に窒化シリコン膜21を形成する工程とを含んでいる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】半導体装置の信頼性を向上させる。

【解決手段】複数のゲート電極3bを覆うように窒化シリコン膜(第1絶縁膜)5を形成した後、オゾンTEOS膜(第1酸化シリコン膜)6、プラズマTEOS膜(第2酸化シリコン膜)を順次積層する。ここで、オゾンTEOS膜6を積層後、プラズマTEOS膜を積層する前に、窒化シリコン膜5をCMPストッパ膜として、CMP法により研磨する。これにより、プラズマTEOS膜の膜厚を均一化させることができるので、半導体装置の信頼性を向上させることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通電極を有する半導体装置及びその製造方法において、処理時間及び処理コストを大幅に低減できる半導体装置及びその製造方法を提供する。

【解決手段】貫通電極19を有する半導体装置及びその製造方法において、半導体基板5の裏面の貫通電極19を含む再配線層18の周囲を囲むように配線同士を絶縁する絶縁部形成用ダミー溝穴部7bを有することにより、配線間を絶縁するためには絶縁部形成用ダミー溝穴部7bの底部に存在する金属層のみを除去すれば良く、大幅な処理時間及び処理コストの低減が実現できる。

(もっと読む)

半導体装置およびその製造方法

【課題】無機材料を用いてコストの低減を図りながら、応力集中によるクラックを回避しつつ、銅配線を覆うことができるパッシベーション膜を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置10は、層間絶縁膜25と、層間絶縁膜25上に突出して形成され、銅を主成分とする材料からなる配線27と、配線27を覆うように形成されたパッシベーション膜30とを含む。パッシベーション膜30は、配線27側から順に第1窒化膜31、中間膜33および第2窒化膜32を積層した積層膜からなる。中間膜33は、第1および第2窒化膜31,32とは異なる絶縁材料(たとえば酸化物)からなる。

(もっと読む)

EM保護が施された半導体ダイを形成する方法

【課題】電磁(EM)妨害あるいはEMIに対してある程度の保護を具備した半導体装置において、低コストで、半導体ウエハからEM保護の施されたダイを形成する方法を提供する。

【解決手段】半導体ダイ12,13,14は、傾斜したサイドウォール35,36,37を有するように形成される。この傾斜サイドウォール上、および、半導体ダイの底部表面上に導体40が形成される。導電材料である導体40は、ダイ12−14に対しEMIから保護する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通電極とパッド電極との接続信頼性を高める。

【解決手段】一方の面と、前記一方の面と対向する他方の面とを有する半導体基板と、前記半導体基板の前記一方の面に設けられた絶縁膜と、前記半導体基板と前記絶縁膜とを貫通する貫通孔と、前記貫通孔の内壁に設けられ、平面視において前記貫通孔と重なる位置に接続孔を有する樹脂膜と、前記絶縁膜上に設けられ、平面視において前記貫通孔と重なる位置に第1凹部を有する配線層と、前記配線層に接続され、前記第1凹部内と前記樹脂膜を介して前記貫通孔内とに設けられた貫通電極とを含む半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】放熱性が向上した半導体装置およびその製造方法の提供。

【解決手段】第1の辺を有する第1の面を有する半導体基板10と、前記半導体基板上に設けられた電極14と、前記電極の上に位置する第1の開口部24を有する第1の絶縁層16と、前記第1の絶縁層の上であって、前記電極の少なくとも一部を避けて設けられた樹脂層20と、前記樹脂層の上に設けられた第1の部分31と、前記第1の部分と前記電極とを電気的に接続する第2の部分32と、前記第1の部分または前記第2の部分と電気的に接続する第3の部分33と、を有する導電層と、前記導電層の前記第2の部分を覆うように設けられ、前記導電層の前記第1の部分の少なくとも一部の上に位置する第2の開口部41を有し、かつ、前記導電層の前記第3の部分を避けて設けられた第2の絶縁層40と、前記導電層の前記第3の部分は、前記第1の面の前記第1の辺と、前記第2の絶縁層との間に位置する。

(もっと読む)

1 - 20 / 132

[ Back to top ]