Fターム[5F033KK26]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | シリサイド (1,324) | 高融点金属のシリサイド (608)

Fターム[5F033KK26]の下位に属するFターム

Fターム[5F033KK26]に分類される特許

1 - 20 / 51

半導体装置の製造方法

【課題】信頼性を低下することなく、高集積化が可能な半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、薄膜抵抗体と配線層とが、接続層とビアホールに埋設されたタングステンプラグとを介して電気的に接続されてなる半導体装置の製造方法である。従来、接続層は、バリアメタル層を介して薄膜抵抗体と接続された構成である。この接続層としてアルミニウムを用いたものでは、接続層とタングステンプラグとの線膨張係数の差異に起因してストレスマイグレーションにより、接続層にボイドが発生する懸念があった。本発明では、接続層を除去する工程を実施し、タングステンプラグをバリアメタル層と直接接続する。これにより、タングステンプラグは、アルミニウムよりなる接続層を介することなく、薄膜抵抗体と電気的に接続される。したがって、接続層におけるボイドの発生を抑制し、半導体装置の接続信頼性を向上することができる。

(もっと読む)

半導体装置

【課題】半導体装置において、高電圧の配線層とその下方を横切るように配置された抵抗層との間の絶縁膜の耐圧を確保し、この配線層と抵抗層との間で破壊が起きるのを抑制することを目的とする。

【解決手段】第1半導体領域10に接続され第2半導体領域11上を通過するように第3配線層22が配置されている。第3配線層22と第2半導体領域11との間に配置される絶縁膜14内には、一端が第3配線層22に接続されると共に、他端が第1半導体領域11よりも電位の低い制御端子12に接続され、且つ第3配線層22とSOI層2との間において第3配線層22を少なくとも1回以上横切る構成で抵抗層25が配置されている。この抵抗層25は、第3配線層22を横切る部位の上面が他の部位よりも下方位置となるように段差状に形成されている。

(もっと読む)

抵抗回路を有する半導体装置

【課題】高抵抗・高精度の抵抗素子からなる抵抗回路を提供する。

【解決手段】500Å以下に薄膜化した薄膜材料からなる抵抗素子の上にシリコン窒化膜などの絶縁膜を形成する。この窒化膜により抵抗素子に対するコンタクトホールの突き抜けを防止する。

(もっと読む)

半導体装置およびその製造方法

【課題】シェアードコンタクトの接触不良を防止して、半導体装置の製造歩留まりを向上させることのできる技術を提供する。

【解決手段】高密度版回路における電界効果トランジスタTr3のゲート電極G3と電界効果トランジスタTr4のゲート電極G4とのピッチは、高速版回路における電界効果トランジスタTr1のゲート電極G1と電界効果トランジスタTr2のゲート電極G2のピッチよりも小さいが、シェアードコンタクトホールSCが達する部分のゲート電極G3に切欠を設けることにより、シェアードコンタクトホールSCと不純物領域S/Dとの接触面積を広くする。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタのチャネル部に印加される応力を増加させて、電流増加効果を高めることを可能とする。

【解決手段】半導体基板上にダミーゲートを形成した後、該ダミーゲートの側壁に側壁絶縁膜を形成し、該ダミーゲートの両側の前記半導体基板にソース・ドレイン領域を形成する工程と、前記ダミーゲートおよび前記ソース・ドレイン領域の上に応力印加膜を形成する工程と、前記ダミーゲートの上の領域に形成された前記応力印加膜と前記ダミーゲートを除去して溝を形成する工程と、前記溝内の前記半導体基板上にゲート絶縁膜を介してゲート電極を形成する工程と、を備えた半導体装置の製造方法。

(もっと読む)

薄膜抵抗を備えた半導体装置の製造方法

【課題】薄膜抵抗と配線部との接触抵抗が高抵抗化することを抑制できる薄膜抵抗を備えた半導体装置の製造方法を提供する。

【解決手段】スパッタ装置内において事前にチタンの表面を窒化させておくことで窒化チタンを形成しておき、その後、窒素の導入を停止した状態で窒化チタンをターゲットとしたスパッタにより、窒化チタン膜によって構成される第1金属層5を形成する。これにより、薄膜抵抗Rと接触する第1金属層5を形成する際に、スパッタ装置内に窒化ラジカルが基本的には存在していない条件で第1金属層5の成膜を行うことができるため、薄膜抵抗Rの露出部分に窒化物が形成されないようにできる。したがって、薄膜抵抗Rと配線部の一部を構成する第1金属層5との接触抵抗が高抵抗化することを抑制することが可能となる。

(もっと読む)

コンタクトプラグ、配線、半導体装置およびコンタクトプラグ形成方法

【課題】金属シリサイド膜と銅コンタクトプラグ本体との間の拡散バリア層として、薄膜の酸化マンガンで構成された拡散バリア層を用いてはいるものの、金属シリサイド膜への銅原子の拡散、侵入を確実に抑止することができるようにする。

【解決手段】本発明のコンタクトプラグ10は、半導体装置の絶縁膜4に設けられたコンタクトホール5に形成され、コンタクトホール5の底部に形成された金属シリサイド膜3と、コンタクトホール5内で金属シリサイド膜3上に形成され、非晶質でシリコンを含む第1の酸化マンガン膜6aと、その第1の酸化マンガン膜6a上に形成され、微結晶を含む非晶質の第2の酸化マンガン膜6bと、その第2の酸化マンガン膜6b上に、コンタクトホール5を埋め込むように形成された銅プラグ層7と、を備えることを特徴としている。

(もっと読む)

半導体装置

【課題】SRAM回路の動作速度を向上させる。

【解決手段】駆動MISFETと転送MISFETとそれらの上部に形成された縦型MISFETとでメモリセルを構成したSRAMにおいて、周辺回路を構成するMISFET間の電気的接続を、メモリセルの縦型MISFET(SV1、SV2)よりも下部に形成されるプラグ28および中間導電層46、47で行うとともに、縦型MISFET(SV1、SV2)よりも上部に形成されるプラグ、第1および第2金属配線層を用いて行うことにより、配線の自由度を向上でき、高集積化できる。また、MISFET間の接続抵抗を低減でき、回路の動作スピードを向上できる。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の設計自由度が高く、ゲート電極及びソース/ドレイン領域に接続されるコンタクト部の形成に問題が生じ難く、微細化プロセスに適した半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、(a)基体21上にゲート電極31を形成し、基体にソース/ドレイン領域37及びチャネル形成領域35を形成し、ソース/ドレイン領域37上にゲート電極31の頂面と同一平面内に頂面を有する第1層間絶縁層41を形成した後、(b)第1層間絶縁層41に溝状の第1コンタクト部43を形成し、(c)全面に第2層間絶縁層51を形成した後、(d)第1コンタクト部43の上の第2層間絶縁層51の部分に孔状の第2コンタクト部53を形成し、その後、(e)第2層間絶縁層51上に、第2コンタクト部53と接続された配線61を形成する各工程から成る。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1に形成したnチャネル型MISFETQnのソース・ドレイン用のn+型半導体領域7bおよびゲート電極GE1上と、pチャネル型MISFETQpのソース・ドレイン用のp+型半導体領域8bおよびゲート電極GE2上とに、ニッケル白金シリサイドからなる金属シリサイド層13bをサリサイドプロセスで形成する。その後、半導体基板1全面上に引張応力膜TSL1を形成してから、pチャネル型MISFETQp上の引張応力膜TSL1をドライエッチングで除去し、半導体基板1全面上に圧縮応力膜CSL1を形成してからnチャネル型MISFETQn上の圧縮応力膜CSL1をドライエッチングで除去する。金属シリサイド層13bにおけるPt濃度は、表面が最も高く、表面から深い位置になるほど低くなっている。

(もっと読む)

半導体装置及びその製造方法

【課題】不純物層が浅く形成された場合にも接合リーク電流の増大を抑制できるようにすると共に、コンタクトホール形成時に位置合わせずれが生じた場合にもコンタクト抵抗の上昇を抑制できるようにする。

【解決手段】基板100上に素子分離領域102及び不純物層103が互いに隣接するように形成されている。不純物層103上にシリサイド層106Bが形成されており、シリサイド層106B上に形成されたコンタクト109が形成されている。不純物層103とシリサイド層106Bとの界面は、素子分離領域102の上面よりも低く、シリサイド層106Bは素子分離領域102の上部コーナーを覆っている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の絶縁膜の上に形成される金属配線または金属電極の接着力を向上させる。

【解決手段】窒化タングステン6bをタングステン6cの側面にまで設けて、タングステン6cと窒化タングステン6bとが接触している面積を増やす。ゲート絶縁膜2上に、ゲート絶縁膜2との接着力が強いポリシリコンサイドウォール5を配置する。タングステン6cの側面にある窒化タングステン6bにはポリシリコンサイドウォール5を密着させる。

(もっと読む)

半導体装置およびフォトマスク

【課題】シェアードコンタクトホールの開口不良を抑制できる半導体装置およびフォトマスクを提供する。

【解決手段】シェアードコンタクトホールSC1、SC2は、ゲート電極層GE1、GE2とドレイン領域PIRとの双方に達している。平面視において、ゲート電極層GE1、GE2の一方側壁E2が、一方側壁E1の仮想延長線E1aよりも他方側壁E4側にずれて位置している。平面視において、ゲート電極層GE1、GE2のシェアードコンタクトホールSC1、SC2が達する部分の線幅D1の中心線(C2−C2)が、ゲート電極層GE1、GE2のチャネル形成領域CHN1、CHN2上に位置する部分の線幅D2の中心線(C1−C1)に対してずれて位置している。

(もっと読む)

半導体装置の製造方法

【課題】ゲート間のピッチが狭い場合における短チャネル効果の劣化を抑制する。

【解決手段】基板上に、第1ゲートと、第1ゲートに隣接する第2ゲートを形成する工程、第1ゲートの側壁に第1サイドウォールを、第2ゲートの側壁に第2サイドウォールを形成する工程、第1ゲート、第1サイドウォール、第2ゲート、第2サイドウォールをマスクとして、基板に第1不純物の注入を行う工程、全面に絶縁膜を堆積した後、絶縁膜をエッチングして、第1サイドウォールの側面に第3サイドウォールを、第2サイドウォールの側面に第4サイドウォールを、第1ゲートと第2ゲートの間において第3サイドウォールと第4サイドウォールとが接触するように形成する工程、第1ゲート、第1及び第3サイドウォール、第2ゲート、第2及び第4サイドウォールをマスクとして、基板に第2不純物の注入を行う工程、第3及び第4サイドウォールを除去する工程、を有する。

(もっと読む)

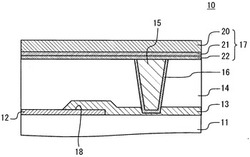

半導体装置の製造方法および固体撮像装置の製造方法

【課題】本発明は、コンタクト抵抗の安定性を確保して、コンタクト抵抗にばらつきを抑えることを可能にする。

【解決手段】基板11のシリコン領域12上に第1金属シリサイド層13を形成する工程と、前記基板11上に前記第1金属シリサイド層13を被覆する絶縁膜14を形成する工程と、前記絶縁膜14に前記第1金属シリサイド層13に通じるコンタクトホール15を形成する工程と、前記コンタクトホール15の内面および前記絶縁膜14上にシリサイド化される第2金属層16を形成する工程と、前記第2金属層16と前記コンタクトホール15の底部のシリコンとを反応させて前記第1金属シリサイド層13上に第2金属シリサイド層17を形成する工程とを有する。

(もっと読む)

半導体装置

【課題】 容量低減とビア加工マージンの確保を効率的に達成する。

【解決手段】 複数の配線層を有する半導体装置であって、所定領域を有する第1配線層26と、第1配線層の上層に位置する第2配線層47と、第1配線層と第2配線層との間に設けられる層間絶縁膜36と、層間絶縁膜と第1配線層の配線との間に設けられるバリア絶縁膜(29,31)とを有し、所定領域における配線上部のバリア絶縁膜の厚さは、所定領域以外の領域における配線上部のバリア絶縁膜の厚さよりも厚く、所定領域においては隣接する配線間にエアギャップ35が形成され、所定領域以外においては隣接する配線間にエアギャップが形成されない。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、絶縁膜のホール内に形成される導電性プラグ等の導電性材料のコンタクト抵抗が基板面内でばらつくのを防止すること。

【解決手段】シリコン基板30の上方に第1の層間絶縁膜45を形成する工程と、第1の層間絶縁膜45の上方に強誘電体キャパシタQを形成する工程と、強誘電体キャパシタQの上方に、水素バリア絶縁膜55、57、62と第2の層間絶縁膜58とを有する積層膜を形成する工程と、エッチングにより積層膜にホール58b、58cを形成する工程と、ホール58b、58c内に金属配線(導電性材料)69を埋め込む工程とを有し、ホール58b、58cを形成する工程において、水素バリア絶縁膜55、57、62のエッチングを、第2の層間絶縁膜58のエッチングとは異なるエッチング手法で行う半導体装置の製造方法による。

(もっと読む)

半導体装置及びその製造方法

【課題】抵抗上昇や表面の電極パッドの突き抜けを防止できる構造を備えた固体撮像装置を提供する。

【解決手段】 半導体装置は、半導体基板6を貫通して形成された貫通電極5と、貫通電極5の上に形成され、貫通電極5と電気的に接続する導電体からなる導電体パッド14と、半導体基板6の表面に形成され、導電体パッド14と電気的に接続する配線層3とを備える。

(もっと読む)

コンタクト構造物の形成方法、及びこれを利用した半導体装置の製造方法

【課題】コンタクト構造物の形成方法及びこれを利用した半導体装置の製造方法を提供する。

【解決手段】コンタクト領域103を有する対象体100上に絶縁層106を形成した後、絶縁層106をエッチングしてコンタクト領域103を露出させる開口を形成する。露出されたコンタクト領域103上にシリコン及び酸素を含む物質膜を形成した後、シリコン及び酸素を含む物質膜上に金属膜を形成する。シリコン及び酸素を含有する物質膜と金属膜を反応させて、少なくともコンタクト領域103上に金属酸化物シリサイド膜121を形成した後、金属酸化物シリサイド膜121上の開口を埋める導電膜を形成する。コンタクト領域とコンタクトとの間に金属、シリコン、及び酸素が三成分系を成す金属酸化物シリサイド膜を均一に形成することができるため、改善された熱安定性及び電気的特性を有する。

(もっと読む)

薄膜半導体装置およびその製造方法

【課題】コンタクトおよび配線形成時の合わせマージンがゼロであり、集積度を大幅に向上し、パターンレイアウトの自由度の拡大を可能とする薄膜半導体素子及びその製造方法を提供する。

【解決手段】透明絶縁性基板10上に形成され、第1導電型の不純物を含むソース領域及びドレイン領域を有する島状半導体層、前記ソース領域及びドレイン領域の間の島状半導体層上に形成されたゲート絶縁膜及びゲート電極18、前記ソース領域又はドレイン領域の表面に形成された高融点金属と半導体との化合物からなる層、前記島状半導体層及びゲート電極を覆う層間絶縁膜29、及び前記ソース領域又はドレイン領域に接続された局所配線28を具備し、前記局所配線28は、前記ソース領域又はドレイン領域の表面に形成された前記化合物層と高融点金属層との2層構造、及び前記ソース領域又はドレイン領域の外側に形成された前記高融点金属層の延長からなることを特徴とする。

(もっと読む)

1 - 20 / 51

[ Back to top ]