Fターム[5F033KK31]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 化合物 (2,201)

Fターム[5F033KK31]の下位に属するFターム

Fターム[5F033KK31]に分類される特許

1 - 20 / 63

半導体装置およびその作製方法

【課題】酸化物半導体膜と金属膜との接触抵抗を低減する。オン特性の優れた酸化物半導体膜を用いたトランジスタを提供する。高速動作が可能な半導体装置を提供する。

【解決手段】酸化物半導体膜を用いたトランジスタにおいて、酸化物半導体膜に窒素プラズマ処理を行うことで酸化物半導体膜を構成する酸素の一部が窒素に置換された酸窒化領域を形成し、該酸窒化領域に接して金属膜を形成する。該酸窒化領域は酸化物半導体膜の他の領域と比べ低抵抗となり、また、接触する金属膜との界面に高抵抗の金属酸化物を形成しにくい。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】低抵抗の微細配線構造を有する半導体装置を提供する。

【解決手段】第1配線420は、半導体基板100上に設けられている。第1ビア440は、第1配線420上に設けられている。また、第1ビア440の底面は、第1配線420に接している。第1絶縁層330は、半導体基板100上に設けられ、少なくとも第1配線420の上面および第1ビア440の側面と接している。第1配線420および第1ビア440のうち各々の側面の少なくとも一部は、各々の金属の結晶粒を分断している。

(もっと読む)

半導体装置の製造方法、半導体装置、及びこれらの層間絶縁層の形成に用いる溶液

【課題】配線間の間隙又は配線の下面と基板の上面との間隙に、絶縁膜を埋設することが困難であった。

【解決手段】半導体装置100の製造方法は、次の工程を含む。すなわち、基板上に絶縁層(絶縁層106)を形成する工程。絶縁層106の一部を選択的に除去して凹部(配線溝107及び配線溝110)を形成し、当該凹部内にバリアメタル膜112と金属膜114とをこの順で埋め込むことにより配線(配線115a、115b)を形成する工程。配線(配線115a、115b)を残しつつ、絶縁層106を除去する工程。絶縁層106を除去する前記工程後、下記の溶液を用いて、配線(配線115a、115b)の周囲を埋設する層間絶縁層118を形成する工程。溶液は、シラン化合物と、界面活性剤からなるポロジェンと、シラン化合物の溶質濃度の増加に応じて、アルコールと比較して、シラン化合物を表面に析出させやすく、かつ増粘しにくいシーター溶媒(アルコール及び水を除く)と、を含むことにより特定される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】本発明は、銅合金配線とビアとの接続面に、窒素を含むバリヤメタル膜が形成されている構造を有する半導体装置であって、銅合金配線とビアとの間における電気抵抗の上昇を抑制することができる半導体装置等を提供する。

【解決手段】本発明に係る半導体装置では、第一の層間絶縁膜内に配設されており、主成分であるCuにAlを添加した第一の銅合金配線と、第一の層間絶縁膜上に形成される第二の層間絶縁膜と、第二の層間絶縁膜内に配設されており、主成分であるCuにAlを添加した第二の銅合金配線とを、備えている。そして、第二の銅合金配線のAlの濃度は、第一の銅合金配線の前記Alの濃度未満である。

(もっと読む)

半導体装置の製造方法、配線用銅合金、及び半導体装置

【課題】半導体装置の歩留まりと信頼性を向上させる。

【解決手段】配線凹部に埋め込まれた部分以外のバリアメタル膜3b上のCu膜5bを化学機械研磨によって除去する。そして配線凹部内のCu膜5b上に、添加元素からなる層6bを形成する。添加元素を層6bからCu膜5b中に拡散させて、Cu表面、及びCu結晶粒の粒界及び該粒界近傍の位置においてCu結晶粒内部よりも添加元素の濃度が高い界面及びその近傍を形成するとともに、Cu膜5b中の酸素を層6bにゲッタリングさせる。その後、余剰な層6bを除去し、さらに絶縁膜上のバリアメタル膜3bを除去する。

(もっと読む)

制御された気孔を形成するための材料及び方法

【課題】基材の内部に空隙を形成するための方法を提供する。

【解決手段】基材を用意する工程;少なくとも1つの犠牲材料前駆体の堆積によって犠牲材料を堆積する工程;複合層を堆積する工程;該複合層中のポロゲン材料を除去して多孔質層を形成する工程;及び積層基材を除去媒体と接触させて前記犠牲材料を実質的に除去し、前記基材の内部に空隙を与える工程を含み、前記少なくとも1つの犠牲材料前駆体が、有機ポロゲン、シリコン、極性溶媒に可溶な金属酸化物、及びそれらの混合物からなる群より選択される方法が提供される。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】絶縁膜の比誘電率を容易かつ十分に低下させる。

【解決手段】半導体装置の製造方法では、それぞれ環状SiO構造を主骨格とし互いに構造が異なる2種類以上の有機シロキサン化合物原料を混合した後で気化する。又は、それら2種類以上の有機シロキサン化合物原料の混合と気化とを一度に行うことによって、気化ガスを生成する。そして、その気化ガスをキャリアガスとともに反応炉に輸送する。そして、反応炉にてその気化ガスを用いたプラズマCVD法又はプラズマ重合法によって多孔質絶縁膜を成膜する。

(もっと読む)

半導体装置の製造方法

【課題】 組み立て工程やCMP工程時における剥離を抑制した、低誘電率層間絶縁膜の製造方法とそれを用いた半導体装置を提供する。

【解決手段】低誘電率層間絶縁膜の成膜の際、高周波と低周波の2周波を切り替え、膜厚方向に膜特性の変調をかけることで、低誘電率を保持したまま密着強度を向上させる。プラズマ発生のための高周波と低周波が同一電極から印加される。そして絶縁膜の成膜開始時あるいは成膜終了時の少なくとも一方において、低周波の入力が成膜開始時及び成膜終了時を除いた他のタイミングより高い。例えば絶縁膜は、厚さ方向における少なくともどちらか一方の端部が、高周波と低周波の2周波により密着層となり、密着層以外の部分は低周波の入力を低下あるいは0にすることで低誘電率絶縁膜となる。

(もっと読む)

半導体装置及びその製造方法

【課題】層間絶縁膜を備えた半導体装置において、膜剥がれの発生及びリークパスの形成を抑制する。

【解決手段】半導体装置は、複数の空孔を含む層間絶縁膜16を備えている。層間絶縁膜16は、単層構造の膜である。層間絶縁膜16における、下面領域に含まれる空孔の空孔径及び上面領域に含まれる空孔の空孔径は、上面領域と下面領域との間に介在する中央領域に含まれる空孔の空孔径よりも小さい。

(もっと読む)

相互接続用自己整合バリアおよびキャッピング層

集積回路に使用する銅線のための集積回路用相互接続構造およびこれを作る方法が提供される。Mn、Cr、またはV含有層が、線からの銅の拡散に対しバリアを形成し、それにより、絶縁体の早期絶縁破壊を防ぎ、銅によるトランジスタの劣化を保護する。また、Mn、Cr、またはV含有層は、銅と絶縁体の間の強い接着を促進し、その結果、製造と使用中のデバイスの機械的健全性を保ち、さらに、デバイスの使用中の銅のエレクトロマイグレーションによる故障を防ぎ、また、環境からの酸素または水による銅の腐食を防ぐ。このような集積回路の形成に関しては、本発明の特定の実施形態により、Mn、Cr、V、またはCoを銅表面上に選択的に堆積させ、一方で、絶縁体表面上のMn、Cr、V、またはCoの堆積を減らす、または防ぎさえもする方法が提供される。また、Mn、Cr、またはV含有前駆物質およびヨウ素または臭素含有前駆物質を使った銅の触媒堆積も提供される。 (もっと読む)

半導体装置の製造方法及びそれを用いた半導体装置

【課題】MIPS構造を採るメタル膜とコンタクトプラグとの界面抵抗を低減できるようにする。

【解決手段】まず、半導体基板1の上に、ゲート絶縁膜3を形成し、形成したゲート絶縁膜3の上に、TiN膜4及びポリシリコン膜5を順次形成する。続いて、ポリシリコン膜5にTiN膜4を露出するコンタクトホール5aを形成する。続いて、ポリシリコン膜5における第1のコンタクトホール5aの少なくとも底面及び壁面上に金属膜7を形成する。

(もっと読む)

半導体装置

【課題】同一の半導体基板上に容量素子を備えたメモリ回路部と論理回路部を有する半導体集積回路装置において、論理回路部のみからなる半導体集積回路装置と完全互換の配線設計パラメーターを確保し、かつ微細化が進んでもセル容量を確保する。

【解決手段】容量素子を備えたメモリ回路部と論理回路部を同一の半導体基板上に有する半導体集積回路装置において、論理回路部に形成される多層配線を絶縁分離する層間絶縁膜の少なくとも複数の配線層にまたがる領域に該容量素子を埋め込むことで、該容量素子の接続に必要な配線をすべて論理回路部の多層配線で構成することにより、論理回路部の設計パラメーターを、該メモリ回路部を有しない半導体集積回路装置と完全に同一とする。また多層配線の複数層に渡るように該容量素子を配置させることで該容量素子の高さを確保し、スケーリングが進んでも必要な容量値を確保する。

(もっと読む)

薄膜トランジスタアレイの製造方法

【課題】凹凸のあるスルーホール部分であっても、層間絶縁膜の上下の導電層間で良好な電気的な接続が得られる、版を用いた印刷法による薄膜トランジスタアレイの製造方法を提供すること。

【解決手段】版に形成された画素電極パターンのスルーホールに対向する位置に保持されたインクの量を、画素電極パターンのスルーホールに対向する位置以外の部分に保持されたインクの量よりも多くすることによって、凹凸のあるスルーホール部分であっても、層間絶縁膜の上下の導電層間で良好な電気的な接続が得られる、版を用いた印刷法による薄膜トランジスタアレイの製造方法を提供することができる。

(もっと読む)

半導体装置の洗浄方法

【課題】ゲートメタル材料の溶解抑制と良好なコンタクト抵抗取得とを両立可能な半導体装置の洗浄方法を提供する。

【解決手段】半導体装置の洗浄方法は、以下の工程を備えている。シリコンを含み、かつ主表面MSを有する半導体基板SBが準備される。主表面MSの上にメタル層GMとシリコン層GPとを下から順に積層した積層ゲートGE2が形成される。主表面MSとシリコン層GP表面との各々にシリサイド層SCLが形成される。主表面MSと積層ゲートGE2表面との各々のシリサイド層SCLの上に絶縁層ILが形成される。半導体基板SBの主表面MSと積層ゲートGE2の表面との各々のシリサイド層SCLが絶縁層ILから露出するようにシェアードコンタクトホールSC2が絶縁層ILに形成される。シェアードコンタクトホールSC2に硫酸洗浄、過酸化水素水洗浄およびAPM洗浄をそれぞれ別工程で行うことによりシェアードコンタクトホールSC2に形成された変質層ALが除去される。

(もっと読む)

半導体装置およびその製造方法

【課題】リーク電流の増加と絶縁耐圧の劣化を抑制し、かつ配線容量の増加を抑制する、信頼性の高い半導体装置を提供する。

【解決手段】半導体基板1上の層間絶縁膜11,13に、第2の配線溝20内の第2の銅配線24、および第2の配線溝20に接続したビアホール15内のプラグとを設ける。ビアホール15の側壁に設けられた第1のサイドウォール17および第2のサイドウォール22と、第2の配線溝20の側壁に設けられた第2のサイドウォール22とを備える。これによりビアホール15のサイドウォールの膜厚を、第2の配線溝20のサイドウォールの膜厚より厚くする。

(もっと読む)

半導体装置およびその製造方法

【課題】実効誘電率を低減させて、高速かつ消費電力の低い半導体装置を実現する。

【解決手段】本発明の半導体装置は、基板と、基板上に形成された層間絶縁膜51、52と、層間絶縁膜51、52に埋め込まれたCu配線1と、Cu配線1上に形成された第二のバリア絶縁膜4と、を有する。第二のバリア絶縁膜4は、炭素二重結合、アモルファスカーボン構造及び窒素を含む有機シリカ膜である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】バリアメタルの被覆性を向上させる。

【解決手段】本発明の半導体装置は、キャップ絶縁膜1d上に形成された絶縁膜と、絶縁膜に形成された配線溝と、配線溝の底面に形成されたビア孔と、少なくともビア孔の側壁を覆うバリアメタル膜と、を有する。ビア孔は、径が異なる複数の孔から構成されており、複数の孔は、下に向けて径が小さくなるように深さ方向に接続し、複数の孔の接続部にキャップ絶縁膜に対してほぼ平行な面を有する。

(もっと読む)

半導体装置、下層配線設計装置、下層配線設計方法およびコンピュータプログラム

【課題】MIMキャパシタの構造破壊に起因するリーク電流の上昇を低減する構成を備えた半導体装置を提供することを課題とする。

【解決手段】複数の下層配線11を備える下層配線層10と、下層配線層10の上方に設けられる、下部電極21と容量誘電膜22と平面形状が下部電極21より小さい上部電極23とを下からこの順に積層したMIMキャパシタ20と、MIMキャパシタ20の上方に設けられ、ビア40、41を介して下部電極21および上部電極23のそれぞれに接続する複数の上層配線31を備える上層配線層30と、を備えた半導体装置であって、上部電極23の平面形状は矩形に構成され、上部電極23の平面のいずれか一以上の辺であるエッジ部の直下には下層配線11が配置されていない半導体装置を提供する。

(もっと読む)

半導体装置の製造方法、半導体装置、アクティブマトリクス装置、電気光学装置および電子機器

【課題】生産性に優れた半導体装置の製造方法、半導体装置、アクティブマトリクス装置、電気光学装置および電子機器を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板7の一方の面側に、トランジスタ4のゲート絶縁体層44を形成する第1の工程と、ゲート絶縁体層44上に、厚さ方向に貫通する貫通部91を備える絶縁体層9を形成する第2の工程と、貫通部91内の底部付近のゲート絶縁体層44上、および、貫通部91の周囲の絶縁体層9上に、気相成膜法により同時にかつ互いに接触しないようにそれぞれ電極を形成し、ゲート絶縁体層44上に形成された電極を用いて、ゲート電極45を形成するとともに、絶縁体層9上に形成された電極を用いて、画素電極6を形成する第3の工程とを有する。また、平面視で、貫通部91の開口部の縁が、当該貫通部91の底部の縁より内側に位置する。

(もっと読む)

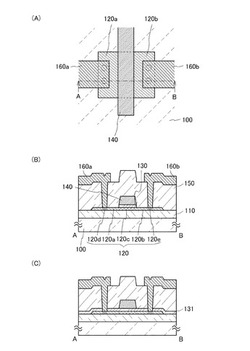

半導体装置及び半導体装置の製造方法

【課題】ビアと配線の間に位置ずれが生じても、エアギャップとビアが繋がることを抑制できるようにする。

【解決手段】配線162は第1絶縁層120に埋め込まれており、上面が第1絶縁層120の上面より高い。エアギャップ128は、配線162と第1絶縁層120の間に位置している。第2絶縁層200は、少なくとも第1絶縁層120上及びエアギャップ128上に形成されている。本図に示す例では、第2絶縁層200は配線162を被覆していない。エッチングストッパー膜210は、少なくとも第2絶縁層200上に形成されている。本図に示す例では、エッチングストッパー膜210は、第2絶縁層200上及び配線162上に形成されている。第3絶縁層220はエッチングストッパー膜210上に形成されている。ビア262は第3絶縁層220に埋め込まれており、配線162に接続している。

(もっと読む)

1 - 20 / 63

[ Back to top ]