Fターム[5F033KK32]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 化合物 (2,201) | 窒化物 (1,946)

Fターム[5F033KK32]の下位に属するFターム

Fターム[5F033KK32]に分類される特許

201 - 220 / 801

半導体装置及び半導体装置の作製方法

【課題】安定した電気特性を有する薄膜トランジスタを有する、信頼性のよい半導体装置を提供することを課題の一とする。また、高信頼性の半導体装置を低コストで生産性よく作製することを課題の一とする。

【解決手段】薄膜トランジスタを有する半導体装置において、薄膜トランジスタの半導体層を、金属元素が添加された酸化物半導体層とする。金属元素として鉄、ニッケル、コバルト、銅、金、モリブデン、タングステン、ニオブ、及びタンタルの少なくとも一種類以上の金属元素を用いる。また、酸化物半導体層はインジウム、ガリウム、及び亜鉛を含む。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】本発明は、しきい値電圧のばらつきが大きいトランジスタのしきい値電圧を調整してしきい値電圧のばらつきを低減することを可能にする。

【解決手段】基板11と絶縁層12とシリコン層13が積層されてなるSOI基板10の該シリコン層13の表面側にトランジスタ20を形成する工程と、SOI基板10上に、トランジスタ20を被覆する第1絶縁膜30と、トランジスタ20に電気的に接続される配線部40とを形成する工程と、配線部40を通じてトランジスタ20のしきい値電圧を測定する工程と、第1絶縁膜30表面に第2絶縁膜を介して支持基板を形成する工程と、SOI基板10の裏面側の基板11と絶縁層12の少なくとも一部を除去する工程と、測定されたしきい値電圧に基づいてトランジスタ20のしきい値電圧を調整する工程を有する。

(もっと読む)

薄膜トランジスタ、表示装置、およびそれらの作製方法

【課題】薄膜トランジスタの電気特性の信頼性を高めることが可能な薄膜トランジスタ及びその作製方法を提供する。また、画質を向上させることが可能な表示装置及びその作製方法を提供する。

【解決手段】また、ゲート電極と、ゲート電極上に形成されるゲート絶縁層と、ゲート電極に重畳し、且つゲート絶縁層上に形成される酸化物半導体層と、ゲート絶縁層及び酸化物半導体層上に形成される配線と、酸化物半導体層及び配線に接する有機樹脂層とを有する薄膜トランジスタである。

(もっと読む)

配線構造及びその形成方法、並びに半導体装置

【課題】炭素元素からなる線状構造体を有する接続部の更なる低抵抗化を実現して、更なる接続部の微細化を可能とする。

【解決手段】ビア孔28a内を充填し、配線溝32aの内壁面を覆うように、例えば超臨界CVD法により、ビア孔28a内におけるCNT28d間の空隙及びCNT28dの中空内を導電材料34で埋め込み、ビアプラグ33と、ビアプラグ33上で配線溝32aの内壁面を覆う下地膜32bとを同時形成する。

(もっと読む)

半導体装置

【課題】製造ばらつきに関わらず、切断箇所を制御できる構成の電気ヒューズを得る。

【解決手段】半導体装置は、基板(不図示)に形成された電気ヒューズ100を含む。電気ヒューズ100は、一端側に設けられた第1の配線112と、第1の配線112とは異なる層に形成された第2の配線122と、第1の配線112と第2の配線122と接触してこれらを接続する第1のビア130と、他端側に設けられ、第1の配線112と同層に第1の配線112から離間して形成された第3の配線142と、第3の配線142と第2の配線122と接触してこれらを接続し、第1のビア130よりも抵抗が低くなるよう構成された第2のビア132と、を含み、切断時に電気ヒューズ100を構成する導電体が外方に流出してなる流出部が形成されて切断される。

(もっと読む)

半導体装置及びその製造方法

【課題】配線が形成された層間絶縁膜を有する半導体装置において、層間絶縁膜と、層間絶縁膜下に形成された下層との界面に、剥離が発生することを防止する。

【解決手段】半導体基板上に形成された第1の層間絶縁膜10と、第1の層間絶縁膜10上に形成された第2の層間絶縁膜14と、第2の層間絶縁膜14の上部領域に形成された第1の配線21とを備え、第2の層間絶縁膜14は、空孔14bを含有する多孔質領域14Bと、非多孔質領域14Aとで構成され、多孔質領域14Bは、第2の層間絶縁膜14のうち、第1の配線21の周囲に位置する領域に形成され、非多孔質領域14Aは、少なくとも第1の層間絶縁膜10と多孔質領域14Bとの間に介在して形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】絶縁信頼性の劣化を低減し、銅配線の信頼性を改善する。

【解決手段】本発明の半導体装置は、半導体基板10と、シリコン(Si)と炭素(C)と酸素(O)とを含み、半導体基板10に形成された第一の多孔質絶縁膜11a及び第二の多孔質絶縁膜11bと、第一の多孔質絶縁膜11a中に埋め込まれた第一の銅配線12aと、第二の多孔質絶縁膜11b中に、それぞれ、埋め込まれた第二の銅配線12b及び銅ビア22と、第二の銅配線12a上に形成された第一のメタルキャップ膜13aと、第二の銅配線12b上に形成された第二のメタルキャップ膜13bと、を有する。第一、第二の多孔質絶縁膜11a、11bは、少なくとも上層のC/Si比が1.5以上であり、かつ、第一、第二の多孔質絶縁膜11a、11bの少なくとも上層に含有される空孔の最大径が1.3nm以下である。

(もっと読む)

半導体装置

【課題】PIDの影響を遮断することのできるレイアウト手法を用いてアンテナダイオードを配置することにより、PIDに起因する電界効果トランジスタの特性劣化を防止して、信頼度の高い半導体装置を実現する。

【解決手段】第1アンテナダイオードAD1とnMISのゲート電極16とを第1層目の配線M1を介して電気的に接続し、第2アンテナダイオードAD2と他の半導体素子とを第1層目の配線M1から第4層目の配線(アナログブロック内の最上層配線から1層下の配線)M4を介して電気的に接続する。さらに第1アンテナダイオードAD1と電気的に繋がる第4層目の配線M4と第2アンテナダイオードAD2と電気的に繋がる第4層目の配線M4とをアナログブロック内の最上層配線である第5層目の配線25によって結線する。

(もっと読む)

薄膜多層配線基板およびその製造方法

【課題】 剥離の発生の少ない薄膜多層配線基板とその製造方法を提案する。

【解決手段】 少なくとも一つの前記配線層が、下層の配線層上に形成された第一のSiO2薄膜と、前記第一のSiO2薄膜上に形成されたSiON薄膜と、前記SiON薄膜上に形成された第二のSiO2薄膜と、前記第二のSiO2薄膜に埋め込まれて形成された配線導体と、前記配線導体と接続しかつ前記第一のSiO2薄膜、前記SiON薄膜および前記第二のSiO2薄膜を貫通して前記下層の配線層の配線導体と電気的に接続するビア導体と、前記第二のSiO2薄膜上に形成されたSiN薄膜と、で構成されている。

(もっと読む)

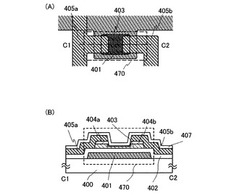

半導体装置の作製方法、半導体装置

【課題】アクティブマトリクス型の液晶表示装置に代表される電気光学装置な

らびに半導体装置において、TFTを作製する工程数を削減して製造コストの低

減および歩留まりの向上を実現することを目的としている。

【解決手段】 基板上に逆スタガ型のTFT上に無機材料から成る第1の層間絶

縁層と、第1の層間絶縁膜上に形成された有機材料から成る第2の層間絶縁層と

、前記第2の層間絶縁層に接して形成された画素電極とを設け、前記基板の端部

に他の基板の配線と電気的に接続する入力端子部とを有し、該入力端子部は、ゲ

ート電極と同じ材料から成る第1の層と、画素電極と同じ材料から成る第2の層

とから形成されていることを特徴としている。このような構成とすることで、フ

ォトリソグラフィー技術で使用するフォトマスクの数を5枚とすることができる

。

(もっと読む)

表示装置

【課題】動作特性に優れ低温で製造可能な酸化物半導体を用いた表示装置の特性を活かすには、適切な構成を備え、占有面積が小さい保護回路等が必要となる。

【解決手段】ゲート電極を被覆するゲート絶縁膜と、ゲート絶縁膜上においてゲート電極と端部が重畳する第1配線層及び第2配線層と、少なくともゲート電極と重畳しゲート絶縁膜及び該第1配線層及び該第2配線層における導電層の側面部及び上面部と接する酸化物半導体層とを有する非線形素子を用いて保護回路を構成する。非線形素子のゲート電極は走査線又は信号線と接続され、非線形素子の第1配線層又は第2配線層がゲート電極の電位が印加されるようにゲート電極層と直接接続されていることで、接続抵抗の低減による安定動作と接続部分の占有面積を縮小する。

(もっと読む)

半導体装置およびその製造方法

【課題】 従来のエアギャップ構造より、さらに容量及び容量ばらつきを低減することができる。

【解決手段】 基板上の絶縁膜17上に、銅を主成分として含む配線26を形成する。それから、リザーバーパターン用絶縁膜21、22及びバリア絶縁膜29を形成し、配線26の上面および側面上と絶縁膜17及び絶縁膜29上に銅の拡散を抑制または防止する機能を有する絶縁膜31を形成する。このとき、狭い配線間スペース底部の絶縁膜17の膜厚保は、配線26上の絶縁膜31の膜厚より、薄く成膜することで細線ピッチの配線容量を効率良く低減する。その後、低誘電率からなる絶縁膜36及び絶縁膜37を成膜する。その際、配線26の隣接配線間において、対向する配線側面の上方での堆積速度が下方での堆積速度より大きくなるように絶縁膜36を形成し、エアギャップを形成する。最後に、層間CMPによって、絶縁膜37を平坦化する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通電極のショート不良を引き起こすことなく、貫通電極とパッド電極との密着性を向上させる。

【解決手段】開口部22が設けられたパッド電極21b上にエッチストッパ膜23を積層し、半導体基板11に形成された貫通孔41に貫通電極45を埋め込む際に、貫通電極45の先端が、開口部22を介してパッド電極21bの一部を突き抜け、エッチストッパ膜23で止められるように構成する。

(もっと読む)

半導体装置

【課題】製造バラツキに関わらず、切断箇所を制御できる構成の電気ヒューズを得る。

【解決手段】半導体装置200は、基板(不図示)上に形成された上層ヒューズ配線112、下層ヒューズ配線122、および上層ヒューズ配線112の一端と接続され、上層ヒューズ配線112と下層ヒューズ配線122とを接続するビア130から構成される電気ヒューズ100を含む。上層ヒューズ配線112には、一端側で配線幅が狭くなった幅変動領域118が設けられている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】低誘電率膜を用いた層間絶縁膜SiOCH膜をCMPプロセスにおけるダメージから保護しつつ、配線間層間絶縁膜SiOCH膜の実効誘電率を低減する。

【解決手段】半導体装置100は、SiOCH膜10の表層が改質されることにより形成された、SiOCH膜10よりも炭素濃度が低くかつSiOCH膜10よりも酸素濃度が高い表面改質層20が設けられるとともに、Cu配線50の表面及び表面改質層20の表面に接するキャップ絶縁膜60を有している。このため、SiOCH膜10全体の誘電率の上昇を低減しつつ、CMPプロセスにおいて親水性の表面改質層20が露出することによって水滴が残りにくくなり、CMPプロセス後のパーティクルの残留やウォーターマークの発生を低減できる。

(もっと読む)

半導体装置

【課題】配線層を薄くした場合にも電極パッド形成領域で配線層がなくなることを確実に防止できるようにし、配線層と電極パッドとを安定して電気的に接続させる。

【解決手段】半導体基板1上の第4層間絶縁膜10中に複数のコンタクト用配線11Bが形成されている。各コンタクト用配線11Bの上及び第4層間絶縁膜10の上に第1保護絶縁膜12が形成されており、第1保護絶縁膜12には、各コンタクト用配線11Bを露出させる第1開口部12aが形成されている。第1開口部12aの内部にはバリアメタル膜13を介して、コンタクト用配線11Bと電気的に接続する電極パッド14が形成されている。第1開口部12aの下側には、コンタクト用配線11Bが配置されていない領域が存在している。

(もっと読む)

半導体装置

【課題】金属パッドの下方に位置する層間絶縁膜にクラックが発生し、クラック内に水分が進入することがあっても、金属パッドの近傍の配線の信頼性が低下することを防止する。

【解決手段】半導体基板10上に形成された層間絶縁膜18と、層間絶縁膜18を貫通して設けられたリング用金属配線20Aと、層間絶縁膜18を貫通して設けられたコンタクト用金属配線20Bと、層間絶縁膜18上及びリング用金属配線20Aの全上面上に形成された第1の保護絶縁膜21と、第1の保護絶縁膜21上に形成された金属パッド23とを備え、リング用金属配線20Aは、層間絶縁膜18のうち金属パッド23の下方に位置する領域にリング状に設けられており、金属パッド23は、第1の保護絶縁膜21に形成された第1の開口部21aを通じてコンタクト用金属配線20Bに接続されている。

(もっと読む)

表示装置

【課題】動作特性に優れ低温で製造可能な酸化物半導体を用いた表示装置の特性を活かすには、適切な構成を備えた保護回路等が必要となる。

【解決手段】ゲート電極15を被覆するゲート絶縁層37と、ゲート絶縁層37上においてゲート電極15と端部が重畳し、第2酸化物半導体層40と導電層41が積層された一対の第1配線層38及び第2配線層39と、少なくともゲート電極15と重畳しゲート絶縁層37及び該第1配線層38及び該第2配線層39における導電層41の側面部及び上面部の一部と第2酸化物半導体層40の側面部と接する第1酸化物半導体層36とを有する非線形素子30aを用いて保護回路を構成する。

ゲート絶縁層37上において物性の異なる酸化物半導体層同士の接合を形成することで、ショットキー接合に比べて安定動作をさせることが可能となり、接合リークが低減し、非線形素子30aの特性を向上させることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】ダマシン法による配線パターン形成の際、低誘電率膜を層間絶縁膜に使った場合においてもビアホールや配線溝の側壁面における損傷や変形の発生を抑制し、同時に、下側配線パターンと上側配線パターンとのコンタクト抵抗を低減する半導体装置の提供。

【解決手段】活性素子を有する基板と、前記基板上において前記活性素子を覆う第1の層間絶縁膜と、前記第1の層間絶縁膜中に埋設された第1の配線層43Cuと、前記第1の層間絶縁膜上に形成された第2の層間絶縁膜52と、前記第2の層間絶縁膜中に埋設された第2の配線層と、を備え、前記第2の配線層は配線パターンと、前記配線パターンから延在し前記第1の配線層を構成する導体パターンの表面と直接に接触するビアプラグ50Vとを有し、前記配線パターンの底面および側壁面、および前記ビアプラグの側壁面は拡散バリア膜49A,49Bにより覆われることを特徴とする半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】Cu配線パターンとキャップ層との界面を伝うCuの拡散を抑制し、同時にCu配線パターンの抵抗の増大を抑制するCuダマシン配線の製造法を提供する。

【解決手段】基板41上に側壁面と底面とにより画成された凹部を有する絶縁膜45を形成する。側壁面のうち、上端部を含む上側の第1の部分Dを覆い、凹部の底面と下側の第2の部分においては前記絶縁膜が露出するように覆う、金属膜47を形成する。凹部の側壁面と底面とを連続的に覆う導電性拡散障壁膜48を形成する。銅を充填し銅配線パターン49A、49B、49Cとする。絶縁膜上と銅配線パターンの表面を覆う絶縁性拡散障壁膜49を形成する。熱処理により、銅配線パターンと絶縁性拡散障壁膜との界面に、金属元素の濃集領域49Dを形成する。金属元素の濃集領域では、金属膜を構成する金属元素の濃度が、銅配線パターン中よりも高い。

(もっと読む)

201 - 220 / 801

[ Back to top ]