Fターム[5F033KK32]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 化合物 (2,201) | 窒化物 (1,946)

Fターム[5F033KK32]の下位に属するFターム

Fターム[5F033KK32]に分類される特許

141 - 160 / 801

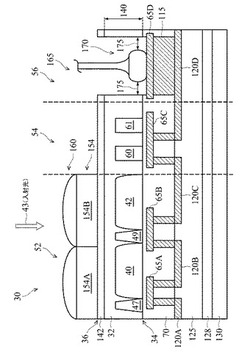

AlCuプロセスのCMOSイメージセンサーの大ビアボンディングパッドのアプリケーション

【課題】AlCuプロセスのCMOSイメージセンサーの大ビアボンディングパッドのアプリケーションを提供する。

【解決手段】集積回路は、ボンディングパッド領域と非ボンディングパッド領域とを有する基板からなる。“大ビア”と称される相対して大きいビアが、ボンディング領域の基板上に形成される。大ビアは、基板向きの上面図にて、第一寸法を有する。集積回路は、非ボンディング領域の基板上に形成された複数のビアも有する。複数のビアは、それぞれ、上面図にて、第二寸法を有し、第二寸法は、第一寸法より相当小さい。

(もっと読む)

半導体装置の製造方法

【課題】

太幅配線の添加元素を細幅配線の添加元素とは独立に制御する。

【解決手段】

層間絶縁膜に、第1の幅を有する第1の配線溝および第1の幅より広い第2の幅を有する第2の配線溝を形成し、第1の配線溝および第2の配線溝内に、第1の添加元素を含む第1のシード層を形成し、第1のシード層上に第1の銅層を形成し、第1の配線溝内の第1の銅層および第1のシード層を残存させつつ、第2の配線溝内の第1の銅層および第1のシード層を除去し、その後、第2の配線溝内に、第2の添加元素を含む又は添加元素を含まない第2のシード層を形成し、第2のシード層の上に第2の銅層を形成する。

(もっと読む)

構造体および構造体を形成する方法

【課題】 サブリソグラフィ・ピッチの構造体とリソグラフィ・ピッチの構造体との相互接続を形成する。

【解決手段】 サブリソグラフィ・ピッチを有する複数の導電線をリソグラフィでパターン形成し、複数の導電線の縦方向から45度より小さい角度の線に沿って切断することができる。代わって、ホモポリマーと混合した共重合体を陥凹エリア内に入れて自己整合し、一定幅領域内にサブリソグラフィ・ピッチを有し、台形領域で隣接線間にリソグラフィ寸法を有する複数の導電線を形成することができる。さらに代わって、サブリソグラフィ・ピッチを有する第1の複数の導電線と、リソグラフィ・ピッチを有する第2の複数の導電線は、同じレベルでまたは異なるレベルで形成することができる。

(もっと読む)

表示装置およびその作製方法

【課題】表示装置の高精細化に伴い、画素数が増加し、ゲート線数、及び信号線数が増加する。ゲート線数、及び信号線数が増加すると、それらを駆動するための駆動回路を有するICチップをボンディング等により実装することが困難となり、製造コストが増大するという問題がある。

【解決手段】同一基板上に画素部と、画素部を駆動する駆動回路とを有し、画素部に酸化物半導体を用いた薄膜トランジスタを用い、さらに駆動回路の少なくとも一部の回路も酸化物半導体を用いた薄膜トランジスタで構成する。同一基板上に画素部に加え、駆動回路を設けることによって製造コストを低減する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】疎水化のために配線層間絶縁膜の表面に形成する層をできるだけ薄くし、且つ、Cu配線上に支障なくキャップメタルを成膜できるようにする。

【解決手段】配線層間絶縁膜(第1の配線層間絶縁膜3)に配線形成用溝(第1層配線形成用溝21)を形成する。配線形成用溝内にCu配線(第1層配線4)を形成し、Cu配線の構成材料のうち配線形成用溝以外の箇所に形成された部分を除去する。Cu配線上及び配線層間絶縁膜上にSi−O、C−O、Si−CH3、Si−H、Si−C及びC−Hのうちの少なくとも何れか1つの結合を含む絶縁膜層(第1の有機ポリマー層6)を形成する。Cu配線上の絶縁膜層を選択的に除去し、Cu配線上にキャップメタル(第1のキャップメタル5)を選択的に形成する。

(もっと読む)

半導体装置の製造方法

【課題】露光によるフォトレジスト膜のパターニングに際し、下地層からの反射光を抑制することができ、かつ、製造コストが抑えられる半導体装置の製造方法を提供する。

【解決手段】半導体基板2上の第1層間絶縁膜3に第1導電層7を形成する工程と、第1導電層7上にストッパー膜8を形成する工程と、ストッパー膜8上にビアホール14が形成された第2層間絶縁膜9を形成する工程と、染料が含有されているフォトレジスト膜を、前記ビアホール内に埋め込むとともに、第2層間絶縁膜9上に形成する工程と、フォトレジスト膜に配線パターンを形成する工程と、配線パターンが形成されたフォトレジスト膜をマスクとして、第2層間絶縁膜9をエッチングして、第2溝部18を形成する工程と、ビアホール14内及び第2溝部18内に第2導電層20を形成する工程と、を備えることを特徴とする。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法においてSRAMのセルサイズを縮小することを目的とする。

【解決手段】メモリセルCの活性領域31a、31bが画定されたシリコン基板31と、素子分離絶縁膜32上に形成され、第1の方向に延在するゲート電極35と、シリコン基板31とゲート電極35の上に形成された第1の絶縁膜42と、第1の絶縁膜42を貫通し、ゲート電極35と第1の活性領域31aに重なり、第1の方向に直交する第2の方向に延在する第1の銅プラグ45aと、第2の活性領域35b上の第1の絶縁膜42を貫通する第2の銅プラグ45bと、第1の絶縁膜42上に形成された第2の絶縁膜44と、第2の絶縁膜44に埋め込まれ、第1の銅プラグ45aの側面45xから第2の延在方向に後退して形成され、第1の銅プラグ45aの上面の一部のみを覆う銅配線48aとを有する半導体装置による。

(もっと読む)

ビアがガウジングされた相互接続構造体及びその製造方法

【課題】 ビア開口部の底部にガウジング構造部を含む相互接続構造体、及びその形成方法を提供する。

【解決手段】 本発明の方法は、ビア開口部の上に配置されるライン開口部内の堆積されたトレンチ拡散バリアの被覆率に影響を与えず、及び/又は、ビア開口部及びライン開口部を含む相互接続誘電体材料内にスパッタリングを行なうことによりビア開口部の底部にガウジング構造部を生成することに起因する損傷を生じさせない。こうした相互接続構造体は、最初に相互接続誘電体内にライン開口部を形成し、その後、ビア開口部、次いでガウジング構造部を形成することによって、ビア開口部の底部内にガウジング構造部を提供することにより達成される。

(もっと読む)

半導体デバイスのための電力グリッド構造体及びその製造方法

【課題】 半導体デバイスに電力を提供する電力グリッド構造体及びその製造方法を提供する。

【解決手段】 本発明の一実施形態は、誘電体層の内部に形成された第1の導電性材料のスタッドと、底部及び側壁を有する第2の導電性材料のビアであって、底部及び側壁は導電性ライナで覆われ、底部はスタッドの直接上に形成され、かつ、導電性ライナを通してビアと接触した状態にある、ビアと、ビアの側壁において導電性ライナを通してビアに接続する第3の導電性材料の1つ又は複数の導電性パスとを含むことができる半導体構造体を提供する。半導体構造体を製造する方法も提供される。

(もっと読む)

配線構造及びその形成方法

【課題】良質な配線構造、及びその形成方法を提供する。

【解決手段】第1の導電材及び第1の絶縁層を有する第1の配線層と、前記第1の絶縁層上の第2の配線層とを備え、前記第2の配線層は第2の絶縁層と、ヴィア及びトレンチを有する開口部とを有し、前記開口部は、第2の導電材と、前記第2の導電材と、前記第2の絶縁層との間の2層以上のバリア層とを有し、前記第2の導電材は、前記第1の導電材と電気的に接続され、前記2層以上のバリア層は、前記開口内の前記第2の絶縁層と第1のバリア層とが接触し、且つ前記第1のバリア層とMnOx含有バリア層とが接触する領域と、前記第2の絶縁層と前記MnOx含有バリア層が接触する領域とを有する。

(もっと読む)

半導体装置

【課題】半導体装置の外部端子に加わる外力により外部端子下の絶縁膜にクラックが生じるのを抑制または防止する。

【解決手段】シリコン基板1の主面s1上に形成された配線層のうちの最上の配線層MHは、アルミニウムからなる導体パターン3によって形成されたパッドPD1を有し、パッドPD1の下面には、下層から順に積層された第1バリア導体膜bm1および第2バリア導体膜bm2からなるバリア導体膜BMaが配置されている。最上の配線層MHの一つ下の第5配線層M5のうち、パッドPD1のプローブ接触領域PAと平面的に重なる領域には導体パターン3は配置されていない。また、第1バリア導体膜bm1はチタン、第2バリア導体膜bm2は窒化チタンをそれぞれ主体とする導体膜であり、第1バリア導体膜bm1の方が、第2バリア導体膜bm2よりも厚く形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】信頼性の高い半導体装置およびその製造方法を提供すること。

【解決手段】半導体基板と、半導体基板の第1面側に形成された半導体素子と、半導体基板の第1面側に形成されて半導体素子と電気的に接続された配線を有する配線層と、半導体基板の第1面側に形成された電極パッド部と、半導体基板の第1面からその反対側の第2面まで貫通する貫通孔内に形成された貫通電極とを備え、前記電極パッド部は、半導体基板の第1面に部分的に積層された単一導電層と、単一導電層に積層された混成導電層とを有し、前記単一導電層は、貫通電極と電気的に接続する導電領域部からなり、前記混成導電層は、単一導電層と前記配線とを電気的に接続する導電領域部と、単一導電層と配線とを電気的に絶縁する絶縁領域部とが混成されてなる半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】実効誘電率を低減させて、高速かつ消費電力の低い半導体装置を実現する。

【解決手段】本発明の半導体装置は、基板と、基板上に形成された層間絶縁膜51、52と、層間絶縁膜51、52に埋め込まれたCu配線1と、Cu配線1上に形成された第二のバリア絶縁膜4と、を有する。第二のバリア絶縁膜4は、炭素二重結合、アモルファスカーボン構造及び窒素を含む有機シリカ膜である。

(もっと読む)

半導体装置およびその製造方法

【課題】リーク電流の増加と絶縁耐圧の劣化を抑制し、かつ配線容量の増加を抑制する、信頼性の高い半導体装置を提供する。

【解決手段】半導体基板1上の層間絶縁膜11,13に、第2の配線溝20内の第2の銅配線24、および第2の配線溝20に接続したビアホール15内のプラグとを設ける。ビアホール15の側壁に設けられた第1のサイドウォール17および第2のサイドウォール22と、第2の配線溝20の側壁に設けられた第2のサイドウォール22とを備える。これによりビアホール15のサイドウォールの膜厚を、第2の配線溝20のサイドウォールの膜厚より厚くする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】バリアメタルの被覆性を向上させる。

【解決手段】本発明の半導体装置は、キャップ絶縁膜1d上に形成された絶縁膜と、絶縁膜に形成された配線溝と、配線溝の底面に形成されたビア孔と、少なくともビア孔の側壁を覆うバリアメタル膜と、を有する。ビア孔は、径が異なる複数の孔から構成されており、複数の孔は、下に向けて径が小さくなるように深さ方向に接続し、複数の孔の接続部にキャップ絶縁膜に対してほぼ平行な面を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の外部からの水分がパッド上の開口部に浸入した場合でも、開口部の側面に露出している窒化チタン膜が酸化チタン膜に変化することを抑制することができ、半導体装置の信頼性を向上できる技術を提供する。また、パッドの表面保護膜にクラックが発生することを抑制し、半導体装置の信頼性を向上できる技術を提供する。

【解決手段】開口部OP2の径を開口部OP1の径よりも小さくし、かつ、開口部OP2を開口部OP1に内包されるように形成する。これにより、開口部OP1の側面に露出する反射防止膜ARの側面を、開口部OP2を形成している表面保護膜PAS2で覆うことができる。この結果、反射防止膜ARの側面を露出することなく、パッドPDを形成することができる。

(もっと読む)

ポリマの指向性自己組織化を利用するサブリソグラフィ構造の形成方法

【課題】 ポリマの指向性自己組織化を利用するサブリソグラフィ構造の形成方法を提供する。

【解決手段】 ブロック・コポリマの自己組織化を含む方法であって、目標とするCD(限界寸法)を有する開口部(1つ又は複数の基板内の)から開始して、ホールを規則的な配列又は任意の配列に形成する方法を説明する。重要なことに、形成されたホールの平均直径の百分率ばらつきは、最初の開口部の平均直径の百分率ばらつきより小さくなる。形成されたホール(又はビア)を下層の基板に転写することができ、次にこれらのホールを金属導体のような材料で埋め戻すことができる。本発明の好ましい態様は、22nm以下の技術ノードにおいても、より狭いピッチ及びより優れたCDの均一性を有するビアの作成を可能にする。

(もっと読む)

薄膜トランジスタ基板の製造方法、薄膜トランジスタ基板、及び表示装置

【課題】コンタクトエッチングの加工精度を上げて、精度良くコンタクトホールが形成されたTFT基板及び、そのTFT基板を工程が煩雑にならずに製造コストが抑制可能なTFT基板の製造方法を提供する。

【解決手段】厚膜レジスト部21と厚膜レジスト部よりも厚みの薄い薄膜レジスト部22と、開口部23とからなる膜厚差を有するパターンのレジスト層20を設け、レジスト層20の開口部の絶縁膜のエッチングと、レジスト層20の薄膜レジスト部22の除去と、薄膜レジスト部22の下層の絶縁膜のエッチングとを同じエッチング工程で行うことにより、ゲートコンタクトホール8及びシリコンコンタクトホール9を共に形成してTFT基板1を製造した。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁破壊に至らない微量の電荷の蓄積を抑制した半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11の上に形成された半導体素子1及び保護ダイオード2を備えている。半導体基板11の上には、半導体素子1及び保護ダイオード2を覆うように第1の層間絶縁膜22が形成されている。第1の層間絶縁膜22には、半導体素子1と電気的に接続された第1のプラグ25と、保護ダイオード2と電気的に接続された第2のプラグ23、24とが形成されている。第2のプラグ23、24の上面の面積は、第1のプラグ25の上面の面積よりも大きい。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の埋め込み不良及び配線抵抗の上昇を抑えると共に、信頼性を向上した半導体装置を実現できるようにする。

【解決手段】半導体装置は、基板101の上に形成された絶縁膜105と、絶縁膜105中に形成された、銅を含む材料からなる埋め込み配線115とを備えている。絶縁膜105と埋め込み配線115との間には、白金族元素を含む材料からなるバリア膜110が形成されている。絶縁膜105とバリア膜110との間には、絶縁膜105よりも密度が高い高密度絶縁膜109が形成されている。

(もっと読む)

141 - 160 / 801

[ Back to top ]