Fターム[5F033KK32]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 化合物 (2,201) | 窒化物 (1,946)

Fターム[5F033KK32]の下位に属するFターム

Fターム[5F033KK32]に分類される特許

161 - 180 / 801

半導体構造体及びその形成方法

【課題】 相互接続構造の信頼性及び拡張性を改善する相互接続構造のための冗長金属拡散バリア層を提供する。

【解決手段】 冗長金属拡散バリア層は、誘電体材料内に設けられた開口内に配置され、且つ開口内に存在する拡散バリア層及び導電性材料の間に配置される。冗長拡散バリア層は、Ru並びに純粋なCo若しくはN,B及びPのうちの少なくとも1つを含むCo合金からなる単層若しくは多層構造である。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法における新規な平坦化処理を提供する。

【解決手段】半導体装置の製造方法は、半導体基板を有する半導体装置の製造方法であって、前記半導体基板の上に絶縁膜を形成する第1の工程と、前記絶縁膜に第1の穴を形成する第2の工程と、前記絶縁膜に前記第1の穴より浅い第2の穴を形成する第3の工程と、前記第1の穴に導電部材を埋め込むことにより導電部を形成するとともに、前記第2の穴に前記導電部材を埋め込むことにより平坦化補助部を形成する第4の工程と、前記導電部、前記絶縁膜、及び前記平坦化補助部を前記平坦化補助部が除去されるまで研磨することにより、前記導電部及び前記絶縁膜のそれぞれの上面を平坦化する第5の工程とを備えている。

(もっと読む)

半導体装置

【課題】電極部と貫通電極層の間の抵抗値ばらつきに依存しない信頼性に優れた半導体装置を提供する。

【解決手段】半導体基板表面2aの第1絶縁膜8の中に、外部接続端子を有する電極部18が形成され、基板をビアホール10が貫通し、ビアホール側壁10a及び基板裏面の第2絶縁膜12とビアホール底面の第1絶縁膜とに貫通電極層11が形成され、電極部と貫通電極層との間にシリサイド層9を接続形成し、ビアホール中心軸を含む平面で切断された断面において、シリサイド層の幅A≦ビアホール底部の幅Bである。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。また、該薄膜トランジスタの作製方法を提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層より導電率の高いバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層を介して電気的に接続されるように薄膜トランジスタを形成する。また、バッファ層に逆スパッタ処理及び窒素雰囲気下での熱処理を行うことにより、酸化物半導体層より導電率の高いバッファ層を形成する。

(もっと読む)

気相成長装置と半導体装置の製造方法

【課題】シランとアンモニアの混合ガスソークによる銅拡散防止絶縁膜形成前の銅配線表面処理を改善できる気相成長装置、および表面状態がよく、抵抗が低い銅配線を有する半導体装置の製造方法を提供する。

【解決手段】シランを供給できるガス供給系1aと反応室を接続する、2つ以上のバルブを含む連続バルブの1つをノーマリオープンとし、ガス供給系と排気系を接続する捨てガスライン3のノーマリクローズのバルブV14と連動させることにより、反応室内の残留ガスの影響を抑制する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層の上に高抵抗領域及び低抵抗領域を有するバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層の低抵抗領域を介して接触するように薄膜トランジスタを形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ビアと配線の間に位置ずれが生じても、エアギャップとビアが繋がることを抑制できるようにする。

【解決手段】配線162は第1絶縁層120に埋め込まれており、上面が第1絶縁層120の上面より高い。エアギャップ128は、配線162と第1絶縁層120の間に位置している。第2絶縁層200は、少なくとも第1絶縁層120上及びエアギャップ128上に形成されている。本図に示す例では、第2絶縁層200は配線162を被覆していない。エッチングストッパー膜210は、少なくとも第2絶縁層200上に形成されている。本図に示す例では、エッチングストッパー膜210は、第2絶縁層200上及び配線162上に形成されている。第3絶縁層220はエッチングストッパー膜210上に形成されている。ビア262は第3絶縁層220に埋め込まれており、配線162に接続している。

(もっと読む)

半導体装置の製造方法

【課題】個片化時に切断部分が欠けてしまうことを防止できる半導体装置の製造方法を提供する。

【解決手段】複数の素子領域と複数の素子領域を区画する区画領域とを具える上面(第1面)と、上面(第1面)の反対側の裏面(第2面)とを有する半導体ウエハ101Aを準備する工程と、上面(第1面)の各素子領域上に、上層配線102をそれぞれ形成する工程と、裏面(第2面)側から半導体ウエハ101Aを例えばDeep−RIEなどによりエッチングすることで、上層配線102を露出する貫通孔A2を形成すると共に、上面(第1面)の区画領域に対応する裏面(第2面)の領域に半導体ウエハ101Aを貫通する溝B22を形成する工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】配線構造における強度の向上と層間絶縁膜の低誘電率化との両立を図れるようにする。

【解決手段】半導体基板100の上に絶縁膜104を形成し、該絶縁膜104の上に金属からなる犠牲膜105を形成する。その後、犠牲膜105を選択的にエッチングすることにより犠牲膜105にトレンチパターン105aを形成する。続いて、トレンチパターン105aが形成された犠牲膜105をマスクとして、絶縁膜104に対して紫外線又は電子線を照射する。その後、トレンチパターン105aが形成された犠牲膜105をマスクとして、絶縁膜104に配線形成溝104aを形成し、該配線形成溝104aに金属膜106bを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】配線遅延の増大を防止すると共に、配線信頼性の低下を抑制する。

【解決手段】半導体装置は、基板の上に形成され、第1の配線2を有する第1の絶縁膜1と、第1の絶縁膜1及び第1の配線2の上に形成された第2の絶縁膜3と、第2の絶縁膜3の上に形成された第3の絶縁膜4とを有している。第2の絶縁膜3は、空孔を含んでいる。

(もっと読む)

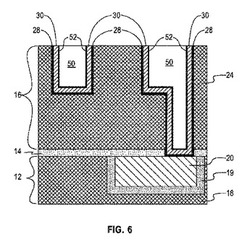

信頼性向上のためのケイ化銅パッシベーション

【課題】その表面をケイ化銅に転化することにより、銅相互接続構造の露出銅表面を直接不動態化するための方法を提供すること。

【解決手段】その後の誘電体フィルムの形成とともに原位置に実行されるシラン・パッシベーション・プロセスは、Cu相互接続構造の露出したCu表面をケイ化銅に転化する。ケイ化銅は、Cu拡散およびエレクトロマイグレーションを抑制し、後続導体材料との接触が行われる領域内でバリア材として機能する。銅相互接続構造の銅表面全体をケイ化する場合もあれば、銅表面の一部分を露出するように上に重なる誘電体に開口部を形成した後で表面の局部部分をケイ化する場合もある。

(もっと読む)

半導体装置

【目的】プロービング試験での導電パッド下に配置された金属配線上の絶縁膜のクラック発生を抑制することが可能な半導体装置を提供することを目的とする。

【構成】本発明の一態様の半導体装置は、導電パッドと、前記導電パッド上に配置され、前記導電パッドの一部が露出するように開口領域が形成された第1の絶縁膜と、前記導電パッドの下方に配置された第2の絶縁膜と、銅(Cu)を用いた配線を有し、前記第2の絶縁膜を介して前記導電パッドの下方に配置され、前記開口領域と重なる領域での最上層における前記配線の最大配線幅w(nm)と前記配線の被覆率R(%)とがある条件を満たすように配置された少なくとも1層の配線層と、を備えたことを特徴とする。

(もっと読む)

薄膜トランジスタの製造方法

【課題】低抵抗なAl配線材料を用いて、生産コストの低下および生産性の向上を図ることができる薄膜トランジスタの製造方法を提供する。

【解決手段】本発明の薄膜トランジスタの製造方法は、Arガスを用いたスパッタリングによって純AlまたはAl合金を第1層として成膜する工程と、前記第1層の上層に、Ar+N2混合ガスまたはAr+NH3混合ガスを用いたスパッタリングによって、前記第1層の材料に加えて窒化アルミニウムも部分的に含む第2層を成膜する工程と、別途形成するコンタクトホールを介して透明膜電極と第1電極の前記第2層とを電気的に接続する工程を含むものである。

(もっと読む)

半導体装置

【課題】配線抵抗の低い半導体装置を提供すること、透過率の高い半導体装置を提供すること、または開口率の高い半導体装置を提供することを課題とする。

【解決手段】ゲート電極、半導体層、ソース電極又はドレイン電極を透光性を有する材料を用いて形成し、ゲート配線又はソース配線等の配線を透光性を有する材料より抵抗率が低い材料で設ける。また、ソース配線及び/又はゲート配線を、透光性を有する材料と当該透光性を有する材料より抵抗率が低い材料を積層させて設ける。これにより、配線抵抗が低く、透過率の高い半導体装置を提供することができる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】近年、半導体集積回路装置の製造プロセスにおいて、窒化シリコン膜等が有する応力に起因する歪を利用したキャリア移動度向上技術が活用されている。これに伴って、ウエハの表側における複雑なデバイス構造上の窒化シリコン膜を高選択で除去するため、熱燐酸によるバッチ方式ウエット処理が必須となっている。これによって、ウエハの裏面の窒化シリコン膜も除去され、一群の歪付与工程の後のプロセスにおいては、ウエハの裏側の表面はポリ・シリコン部材ということとなる。しかし、一般的なウエハの裏面等の洗浄に使用する方法は、裏面が窒化シリコン膜等であることを前提とするものであり、その特性の異なるポリ・シリコン主体の裏面を有するウエハでは洗浄の効果が十分といえない恐れがある。

【解決手段】リソグラフィ工程の前に、FPM処理の後SPM処理を実行する2工程を含むウエハ裏面に対するウエット洗浄処理を実行する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】Cuダマシン多層配線構造におけるセミ・グローバル配線の形成方法において、ダマシン配線構造を形成する際、ドライ・エッチングによりビア底のエッチ・ストップ絶縁膜を除去した後、ビア底表面上のカーボン系堆積物等を抑制する為に、窒素プラズマ処理を行うことが一般的である。その後、連続放電によって窒素プラズマ除電を行ってウエハ搬送するシーケンスを実行すると、ビア・チェーン終端部にて、ある閾値以上の長さを有するパッド引き出し配線に接続された終端部のビア底で、Cuえぐれが発生ことが、本願発明者らの検討によって明らかとなった。

【解決手段】本願発明は、ダマシン・セミ・グローバル配線等のビア・ホール形成工程において、ビア底エッチ・ストップ膜に対するドライ・エッチング処理後、同処理室内で行われる窒素プラズマ処理に引き続いて、アルゴン・プラズマによる除電処理を実行するものである。

(もっと読む)

Cu膜の成膜方法および記憶媒体

【課題】表面性状が良好でかつ高品質のCVD−Cu膜を下地に対して高い密着性をもって成膜することができるCu膜の成膜方法を提供すること。

【解決手段】チャンバー1内にウエハWを収容し、チャンバー1内にカルボン酸第1銅錯体、例えばCH3COOCuとこれを還元する還元剤とを気相状態で導入して、ウエハW上にCVD法によりCu膜を成膜する。

(もっと読む)

半導体装置の製造方法

【課題】シールリングの構造を最適化して、ダイシング部の切断面からの水分の侵入やクラックの伸展に対する障壁としての機能を確保したシールリングを備えた半導体装置の製造方法を提供する。

【解決手段】半導体基板1上の回路形成領域とダイシング領域との間にシールリング100が配設されている。シールリング100は、断面形状がT字型をなすシール層が積層された部分と、断面形状が矩形をなすシール層が積層された部分とを有している。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体層を用い、電気特性の優れた薄膜トランジスタを備えた半導体装置を提供することを課題の一つとする。

【解決手段】チャネル形成領域にSiOxを含む酸化物半導体層を用い、電気抵抗値の低い金属材料からなるソース電極層及びドレイン電極層とのコンタクト抵抗を低減するため、ソース電極層及びドレイン電極層と上記SiOxを含む酸化物半導体層との間にソース領域またはドレイン領域を設ける。ソース領域またはドレイン領域は、SiOxを含まない酸化物半導体層または酸窒化物膜を用いる。

(もっと読む)

薄膜トランジスタ表示板の製造方法およびこれに使用されるネガティブフォトレジスト組成物

【課題】パターンの不良が減少した薄膜トランジスタ表示板の製造方法およびこれに使用されるネガティブフォトレジスト組成物を提供する。

【解決手段】基板上に導電性物質からなる導電膜を形成する段階と、導電膜上にネガティブフォトレジスト組成物からなるエッチングパターンを形成する段階と、エッチングパターンをエッチングマスクとして利用して導電膜をエッチングし、導電膜パターンを形成する段階とを含み、ネガティブフォトレジスト組成物は、アルカリ現像液に溶解性を有するヒドロキシル基を含有するノボラック樹脂10〜50重量部、第1光酸発生剤(特定構造のスルホニルオキシイミド化合物)0.5〜10重量部、第2光酸発生剤(第1光酸発生剤とは構造の異なる特定構造のスルホニルオキシイミド化合物)0.5〜10重量部、架橋結合剤1〜20重量部および溶媒10〜90重量部を含む。

(もっと読む)

161 - 180 / 801

[ Back to top ]