Fターム[5F033LL01]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜材料の特徴点 (1,721) | 不純物、イオンを含むもの (1,142)

Fターム[5F033LL01]の下位に属するFターム

Fターム[5F033LL01]に分類される特許

1 - 20 / 167

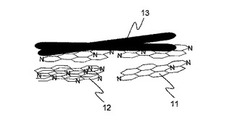

導電材料およびこれを用いた電気素子

【課題】 フレキシブルで、軽く、安定で高導電性の導電材料およびこれを用いた電気素

子を提供する。

【解決手段】

本発明の導電材料は、少なくとも一つの次元方向が200nm以下であり、かつ炭素原

子の一部が少なくとも窒素原子に置換された単層グラフェン及び多層グラフェンの少なく

とも1種よりなるカーボン材料と、金属の粒子及び線材の少なくとも1種よりなる金属材

料とが、混合及び/又は積層されてなることを特徴とする。

(もっと読む)

半導体装置

【課題】層間絶縁膜のエッチングの際に半導体層がエッチングされることによるコンタク

ト抵抗の増大を防ぎ、書き込み特性及び電荷保持特性に優れた不揮発性半導体記憶装置及

びその作製方法を提供する。

【解決手段】ソース領域又はドレイン領域とソース配線又はドレイン配線との間に導電層

を設ける。また、該導電層は、制御ゲート電極を形成する導電層と同じ導電層からなる。

また、該導電層を覆うように絶縁膜が設けられており、該絶縁膜は該導電層の一部が露出

するコンタクトホールを有する。また、該ソース配線又はドレイン配線は、該コンタクト

ホールを埋めるように形成されている。

(もっと読む)

カーボンナノチューブ層とオーバーコート層とを具備する複合層のパターン形成方法、及び前記方法で形成されたパターン

【課題】導電膜の所望部分を面内均一に除去することが出来ると共に高性能な導電膜を得ることが可能なパターン形成方法を提供することを目的とする。

【解決手段】カーボンナノチューブ層と、該カーボンナノチューブ層を覆うオーバーコート層とを具備する複合層のパターン形成方法であって、前記カーボンナノチューブ層が、単独では、実質上、エッチングされないものの、前記オーバーコート層のエッチングによって、前記カーボンナノチューブ層が共にエッチングされる前記オーバーコート層のエッチング剤が、前記オーバーコート層上に、所定パータンで塗布される塗布工程を具備する。

(もっと読む)

半導体電極構造

【課題】半導体装置の製造工程で高温下に曝された場合であっても、ヒロックの発生が抑制されて耐熱性に優れ、かつ膜自体の電気抵抗率が低く抑えられたAl合金膜を有する半導体電極構造を提供する。

【解決手段】基板上に少なくとも、基板側から順に、高融点金属の窒化物薄膜と、Al合金膜とを備えた半導体電極構造であって、前記Al合金膜は、500℃で30分間保持する加熱処理を行った後に下記(a)〜(c)を全て満たし、かつ膜厚が300nm〜5μmであることを特徴とする半導体電極構造。(a)Alマトリックスの最大粒径が1μm以下(b)ヒロック密度が1×109個/m2未満(c)電気抵抗率が10μΩcm以下

(もっと読む)

半導体装置用Al合金膜

【課題】半導体装置の製造工程で高温下に曝された場合であっても、ヒロックの発生が抑制されて耐熱性に優れ、かつ膜自体の電気抵抗率が低く抑えられた半導体装置用Al合金膜を提供する。

【解決手段】500℃で30分間保持する加熱処理を行った後に下記(a)〜(c)を全て満たし、かつ膜厚が500nm〜5μmであることを特徴とする半導体装置用Al合金膜。(a)Alマトリックスの最大粒径が800nm以下(b)ヒロック密度が1×109個/m2未満(c)電気抵抗率が10μΩcm以下

(もっと読む)

半導体装置の製造方法

【課題】本実施形態は、コンタクトプラグの抵抗の低減を行うことができる半導体装置の製造方法を提供する。

【解決手段】本実施形態の半導体装置の製造方法は、基板にコンタクトホール又はコンタクトトレンチを形成し、コンタクトホール又はコンタクトトレンチの底に、アモルファスシリコン層又は多結晶シリコン層を形成し、アモルファスシリコン層又は多結晶シリコン層を覆うように不純物を含むニッケル膜を形成し、加熱することによりニッケル膜とアモルファスシリコン層又は多結晶シリコン層とを反応させて、ニッケルシリサイド膜を形成し、コンタクトホール又はコンタクトトレンチを埋め込むようにコンタクト金属膜を形成する。

(もっと読む)

半導体装置、電子デバイス、及び、半導体装置の製造方法

【課題】 より信頼性の高いCu−Cu接合界面を有する半導体装置及びその製造方法を提供する。

【解決手段】 半導体装置1を、第1の配線18を含む第1半導体部10と、第1半導体部10と貼り合わせて設けられ、第1の配線18と電気的に接合された第2の配線28を含む第2半導体部20とを備える構成とする。さらに、半導体装置1は、酸素に対して水素よりも反応し易い金属材料と酸素とが反応して生成された金属酸化物17bを備える。そして、この金属酸化物17bを、第1の配線18及び第2の配線28の接合界面Sj、並びに、第1の配線18及び第2の配線28の少なくとも一方の内部を含む領域に拡散させた構成とする。

(もっと読む)

表示装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあわせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

表示装置および半導体装置用Al合金膜

【課題】450〜600℃程度の高温下に曝されてもヒロックが発生せず高温耐熱性に優れており、膜自体の電気抵抗(配線抵抗)も低く、アルカリ環境下の耐食性にも優れた表示装置用Al合金膜を提供する。

【解決手段】Geを0.01〜2.0原子%と、Ta、Ti、Zr、Hf、W、Cr、Nb、Mo、Ir、Pt、Re、およびOsよりなる群(X群)から選択される少なくとも一種の元素とを含み、450〜600℃の加熱処理を行なったとき、下記(1)の要件を満足する表示装置もしくは半導体装置用Al合金膜である。

(1)Alと、前記X群から選択される少なくとも一種の元素と、Geとを含む第1の析出物について、円相当直径50nm以上の析出物が200,000個/mm2以上の密度で存在する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】本発明は、銅合金配線とビアとの接続面に、窒素を含むバリヤメタル膜が形成されている構造を有する半導体装置であって、銅合金配線とビアとの間における電気抵抗の上昇を抑制することができる半導体装置等を提供する。

【解決手段】本発明に係る半導体装置では、第一の層間絶縁膜内に配設されており、主成分であるCuにAlを添加した第一の銅合金配線と、第一の層間絶縁膜上に形成される第二の層間絶縁膜と、第二の層間絶縁膜内に配設されており、主成分であるCuにAlを添加した第二の銅合金配線とを、備えている。そして、第二の銅合金配線のAlの濃度は、第一の銅合金配線の前記Alの濃度未満である。

(もっと読む)

半導体装置及びその製造方法

【課題】多結晶シリコンプラグと上層の導体プラグとの界面に十分な膜厚の金属シリサイド層を形成してコンタクト抵抗の低減を図る。

【解決手段】多結晶シリコンプラグを形成した後、多結晶シリコンプラグの表面からゲルマニウムイオン注入を実施してゲルマニウム含有多結晶シリコン16Gとし、その後、シリサイド化可能な金属膜を成膜して金属シリサイド層19を形成し、金属シリサイド19上に導体膜(バリア膜20、W膜21)を形成する。

(もっと読む)

配線材料、配線の製造方法、及びナノ粒子分散液

【課題】焼成無しで、酸素雰囲気に安定であり、かつ低抵抗な配線材料を提供する。また、従来の配線材料よりも低い温度で還元焼成できる配線材料を提供する。

【解決手段】銅と窒素を含む配線材料であって、当該配線材料には、添加材料として、エリンガム図において銅よりも酸化しやすい材料が0.5atm%以上10atm%以下添加されている。添加材料として、例えば、Si、Zr、Ti、Ni、Sn、Mn、Alのうち少なくとも1種類の金属を含む。この配線材料を加熱還元して低抵抗化する場合、1000Pa以下に減圧した雰囲気で加熱を行うことが好ましい。

(もっと読む)

電子デバイス配線用Cu合金スパッタリングターゲット材、及び素子構造

【課題】酸化物反応層の寄生抵抗の低減を図り、動作特性の向上を図った電子デバイス配線用Cu合金スパッタリングターゲット材、及び素子構造を提供する。

【解決手段】TFT素子1は、a−Si膜5上に形成されたPドープn+a−Si膜6と、Pドープn+a−Si膜6上に形成された1nm以下のSi酸化膜7を有している。電極配線膜となるCu合金膜8が、Si酸化膜7上にスパッタリングにより形成されている。Cu合金膜8は、0.3〜2.0原子%のSn、In、Gaの金属のうち1種以上を含有する。

(もっと読む)

耐透明導電膜ピンホール腐食性に優れた薄膜トランジスタ基板

【課題】薄膜トランジスタにおいて透明導電膜と電極配線膜が直接接続する構造を有する薄膜トランジスタ基板であって、その製造工程において、腐食防止用塗料の塗布や剥離といった工程を設けることなく、ピンホール腐食を防止できるような薄膜トランジスタ基板を提供する。

【解決手段】薄膜トランジスタにおいて透明導電膜と電極配線膜が直接接続する構造を有する薄膜トランジスタ基板であって、前記透明導電膜の結晶最大粒径が200nm以下である薄膜トランジスタ基板。

(もっと読む)

薄膜トランジスタ基板、および薄膜トランジスタ基板を備えた表示デバイス

【課題】金属配線膜のドライエッチングレートの低下やエッチング残渣を発生させることがなく、また該金属配線膜のヒロック耐性や電気抵抗率が抑制され、更に該金属配線膜と直接接続する透明導電膜や酸化物半導体層とのコンタクト抵抗率が抑制された薄膜トランジスタ基板、及び該薄膜トランジスタ基板を備えた表示デバイスを提供する。

【解決手段】薄膜トランジスタ基板であって、金属配線膜は、ドライエッチング法によるパターニングで形成された、Ni:0.05〜1.0原子%、Ge:0.3〜1.2原子%、Laおよび/またはNd:0.1〜0.6原子%を含有するAl合金膜とTi膜とからなる積層膜あって、該Ti膜が、該酸化物半導体層と直接接続していると共に、該Al合金膜が、該透明導電膜と直接接続している。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子及びその製造方法を提供する。

【解決手段】基板上で第1方向に延在するラインパターンと、ラインパターンの端部から、第1方向と異なる方向に延在する分岐ラインパターンとをそれぞれ含む第1導電ライン;第2導電ライン;第3導電ラインとを含む半導体素子であり、中間に位置する導電ラインの分岐ラインパターンは、他の導電ラインの分岐ラインパターン間に位置し、長さもさらに短い。これにより、コンタクト・パッドが、導電ラインの分岐ラインパターンと一体に形成されうる。

(もっと読む)

電子回路付き基板及びその製造方法、並びに混合型電子回路形成キット

【課題】DNA又はDNA−脂質複合体を用いた簡易な方法により、基板上に導電性パターンを、画像流れを抑制しながら安定して形成できる電子回路付き基板の製造方法を提供する。

【解決手段】基板上に、DNA又はDNA−脂質複合体を含む溶液を描画することによって電子回路パターンを形成する工程と、前記電子回路パターンが形成された基板を多価金属イオン溶液に浸漬することによって、前記電子回路パターンにおいて、前記DNA又は前記DNA−脂質複合体と前記多価金属イオンとの錯体を形成する工程と、形成された錯体中の金属イオンを還元することによって、前記電子回路パターンを導電性パターンとする工程と、を有する電子回路付き基板の製造方法である。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、バリアメタルの絶縁膜及びCuに対する密着性と、Cu拡散防止とを両立する。

【解決手段】 第1絶縁膜に設けた凹部の側壁に第2絶縁膜を形成し、第2絶縁膜の内側に順に第2絶縁膜との密着性が優れている第1の導電性バリア層、炭素を含有する第2の導電性バリア層、及び、Cu系埋込電極との密着性が優れている第3の導電性バリア層の3層構造のバリア層を介してCu系埋込電極を設けるとともに、前記第1の導電性バリア層と前記第2の導電性バリア層との界面と、前記第2の導電性バリア層と前記第3の導電性バリア層との界面に炭素混合領域を設ける。

(もっと読む)

成膜方法、半導体装置の製造方法及び半導体装置

【課題】表面の平坦性の優れたシリコン膜を形成する成膜方法、半導体装置の製造方法及び半導体装置を提供する。

【解決手段】基体上にジシラン及びトリシランの少なくともいずれかを用いて第1温度で第1膜を形成する第1膜形成工程と、前記基体及び前記第1膜を、水素を含む雰囲気中において、前記第1温度から、前記第1温度よりも高い第2温度に向けて昇温する昇温工程と、前記昇温の後に、前記第1膜の上に、シランを用いて前記第2温度で第2膜を形成する第2膜形成工程と、を備えたことを特徴とする成膜方法が提供される。

(もっと読む)

良伝導性非晶質合金、弱電用良伝導性非晶質合金および強電用良伝導性非晶質合金

【課題】単電子トンネリングを利用して、低温から室温まで動作可能な良伝導性非晶質合金、弱電用良伝導性非晶質合金および強電用良伝導性非晶質合金を提供する。

【解決手段】伝導島を有する孤立した複数の金属クラスターが、サブナノスケールの絶縁層を介して連続して連なった集積ナノ構造を有している。電子が、伝導島を介して、極低温から500℃の範囲で各金属クラスター間をトンネリングするよう構成されており、直流・交流のバリスティック伝導を示す。また、各金属クラスター間にサブナノスケールの原子空孔が均一に分布している。水素原子が各金属クラスター間に侵入固溶した、Ni-Nb-Zr系非晶質合金またはTi-Ni-Cu系非晶質合金から成っていてもよい。

(もっと読む)

1 - 20 / 167

[ Back to top ]