Fターム[5F033LL02]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜材料の特徴点 (1,721) | 不純物、イオンを含むもの (1,142) | 金属 (317)

Fターム[5F033LL02]に分類される特許

41 - 60 / 317

半導体装置

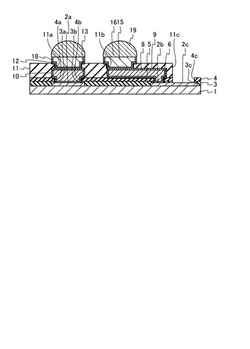

【課題】工程数の増大を抑制しつつ、チップ上に形成された再配線または突出電極の信頼性を向上させる。

【解決手段】配線2bおよびパッド電極2aが形成された半導体基板と、半導体基板上に形成された応力緩和層4と、応力緩和層4上に合金シード膜5を形成した後、応力緩和層4と合金シード膜5とを熱処理にて反応させることで、応力緩和層4と合金シード膜5との間に反応性バリア絶縁膜6を形成する。再配線8または突出電極は合金シード膜5上に形成する。

(もっと読む)

液晶表示装置及びその製造方法

【課題】製造に際して配線にヒロックが発生せず、かつエッチング形状の制御が容易な液晶表示装置を提供する。

【解決手段】液晶表示装置は、基板上にマトリクス配置された走査線と、信号線12と、前記走査線及び信号線に接続される薄膜トランジスタと、前記薄膜トランジスタに接続される画素電極27とを有する液晶表示装置において、前記走査線が下層からアルミニウム−ネオジム合金層211と高融点金属層212との積層構造からなり、前記信号線12が下層から高融点金属層231とアルミニウム−ネオジム合金層232と高融点金属層233との3層構造からなり、高融点金属の種類に応じて、ネオジム含有量を調整する。

(もっと読む)

配線材料、配線の製造方法、及びナノ粒子分散液

【課題】焼成無しで、酸素雰囲気に安定であり、かつ低抵抗な配線材料を提供する。また、従来の配線材料よりも低い温度で還元焼成できる配線材料を提供する。

【解決手段】銅と窒素を含む配線材料であって、当該配線材料には、添加材料として、エリンガム図において銅よりも酸化しやすい材料が0.5atm%以上10atm%以下添加されている。添加材料として、例えば、Si、Zr、Ti、Ni、Sn、Mn、Alのうち少なくとも1種類の金属を含む。この配線材料を加熱還元して低抵抗化する場合、1000Pa以下に減圧した雰囲気で加熱を行うことが好ましい。

(もっと読む)

電子デバイス配線用Cu合金スパッタリングターゲット材、及び素子構造

【課題】酸化物反応層の寄生抵抗の低減を図り、動作特性の向上を図った電子デバイス配線用Cu合金スパッタリングターゲット材、及び素子構造を提供する。

【解決手段】TFT素子1は、a−Si膜5上に形成されたPドープn+a−Si膜6と、Pドープn+a−Si膜6上に形成された1nm以下のSi酸化膜7を有している。電極配線膜となるCu合金膜8が、Si酸化膜7上にスパッタリングにより形成されている。Cu合金膜8は、0.3〜2.0原子%のSn、In、Gaの金属のうち1種以上を含有する。

(もっと読む)

多重膜のエッチング液組成物及びそのエッチング方法

【課題】Cu/Mo積層金属膜、Cu/Mo合金積層金属膜、Cu合金/Mo合金積層金属膜のような、銅又は銅合金の1層以上の銅層と、モリブデン又はモリブデン合金の1層以上のモリブデン層とを含む多重膜を、効率的で優秀に同時に一括してエッチングすることができるエッチング液組成物及びこれを用いた多重膜のエッチング方法を提供する。

【解決手段】エッチング液組成物は、総重量に対して、リン酸50〜80wt%;硝酸0.5〜10wt%;酢酸5〜30wt%;イミダゾール0.01〜5wt%;及び残量の水を含む。添加剤イミダゾールは、銅/モリブデンガルバニック反応調節剤として機能する。

(もっと読む)

半導体デバイス

【課題】ストレスによる半導体回路の特性変動・劣化を抑制した半導体デバイスを提供する。

【解決手段】縦導体3は、半導体回路に隣接して半導体層1の厚み方向に設けられ、少なくとも一つは、半導体層1と対面する領域に、等軸晶領域を有するか、または、凝固点と融解点との温度差が50℃以上である。

(もっと読む)

半導体デバイス

【課題】応力による半導体回路の特性劣化を抑制した半導体デバイスを提供する。

【解決手段】縦導体は、半導体基板の厚み方向に設けられた微細孔を満たし、第1結晶組織301と第2結晶組織302とを含むナノコンポジット結晶構造を有する。ナノコンポジット結晶構造において、第1結晶組織301及び第2結晶組織302の少なくとも一方は、ナノサイズである。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】MRAMにおいては、書き込み電流の低減やディスターブ回避を目的に、書き込みに使用する配線を強磁性体膜で覆うクラッド配線構造がよく用いられている。また、高信頼性製品の信頼性確保のためCu配線中に微量のAlを添加するCuAl配線が広く使用されている。MRAMも高信頼性製品に搭載される可能性が高く、信頼性は重要である。しかし、クラッド配線は、もともと配線抵抗が高いCuAl配線の配線抵抗を更に上昇させるというデメリットがあるため、両方の技術を同時に使用すると配線抵抗のスペックを満たさなくなる可能性が高い。

【解決手段】本願発明は、多層銅埋め込み配線を有する半導体装置において、MRAMメモリセルマトリクス領域を構成する複数の銅埋め込みクラッド配線の銅配線膜を比較的純粋な銅で構成し、これらの配線層よりも下層の銅埋め込み非クラッド配線の銅配線膜を、Alを添加したCuAl配線膜とするものである。

(もっと読む)

配線構造体、半導体素子、配線基板、表示用パネル及び表示装置

【課題】 酸化物電極との良好な接続を行うことや、絶縁膜等との界面で生じる相互拡散を抑制することができ、かつ製造工程の低コスト化を図ることができる配線構造体、それを用いた半導体素子、配線基板、表示用パネル及び表示装置を提供する。

【解決手段】 アルミニウム層、銅層及び銅合金層からなる群より選択される少なくとも1つの層と、アルミニウム合金層とを含む2層以上の積層体であり、該アルミニウム合金層が表層に配置されている配線構造体である。これにより、液晶表示装置等において、酸化物電極と配線との接続部で酸化膜が形成されず、良好な接続を行うことができる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】半導体装置の信頼性を向上させる。

【解決手段】複数のゲート電極3bを覆うように窒化シリコン膜(第1絶縁膜)5を形成した後、オゾンTEOS膜(第1酸化シリコン膜)6、プラズマTEOS膜(第2酸化シリコン膜)を順次積層する。ここで、オゾンTEOS膜6を積層後、プラズマTEOS膜を積層する前に、窒化シリコン膜5をCMPストッパ膜として、CMP法により研磨する。これにより、プラズマTEOS膜の膜厚を均一化させることができるので、半導体装置の信頼性を向上させることができる。

(もっと読む)

耐透明導電膜ピンホール腐食性に優れた薄膜トランジスタ基板

【課題】薄膜トランジスタにおいて透明導電膜と電極配線膜が直接接続する構造を有する薄膜トランジスタ基板であって、その製造工程において、腐食防止用塗料の塗布や剥離といった工程を設けることなく、ピンホール腐食を防止できるような薄膜トランジスタ基板を提供する。

【解決手段】薄膜トランジスタにおいて透明導電膜と電極配線膜が直接接続する構造を有する薄膜トランジスタ基板であって、前記透明導電膜の結晶最大粒径が200nm以下である薄膜トランジスタ基板。

(もっと読む)

半導体装置及びその製造方法

【課題】配線間の実効的な容量の増加を抑制する。

【解決手段】半導体装置100は、6員環構造の環状シロキサンを原料とする絶縁膜11と、絶縁膜11に形成された配線溝12と、配線溝12に金属膜(配線メタル)15が埋め込まれて構成される配線10と、を有する。半導体装置100では、配線溝12の底面において、絶縁膜11の内部よりも単位体積あたりの炭素原子数、又は/及び、窒素原子数が多い改質層13が形成されている。

(もっと読む)

半導体装置の作製方法

【課題】下地に対する選択比が大きく、テーパー形状の配線を形成するドライエッチング

方法を提供する。

【解決手段】基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下の配線を形成

する。また、基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下のゲート配線

を形成し、前記ゲート配線上にゲート絶縁膜を形成し、前記ゲート絶縁膜上に活性層を形

成する。

(もっと読む)

薄膜トランジスタ基板、および薄膜トランジスタ基板を備えた表示デバイス

【課題】金属配線膜のドライエッチングレートの低下やエッチング残渣を発生させることがなく、また該金属配線膜のヒロック耐性や電気抵抗率が抑制され、更に該金属配線膜と直接接続する透明導電膜や酸化物半導体層とのコンタクト抵抗率が抑制された薄膜トランジスタ基板、及び該薄膜トランジスタ基板を備えた表示デバイスを提供する。

【解決手段】薄膜トランジスタ基板であって、金属配線膜は、ドライエッチング法によるパターニングで形成された、Ni:0.05〜1.0原子%、Ge:0.3〜1.2原子%、Laおよび/またはNd:0.1〜0.6原子%を含有するAl合金膜とTi膜とからなる積層膜あって、該Ti膜が、該酸化物半導体層と直接接続していると共に、該Al合金膜が、該透明導電膜と直接接続している。

(もっと読む)

半導体装置の製造方法、配線用銅合金、及び半導体装置

【課題】半導体装置の歩留まりと信頼性を向上させる。

【解決手段】配線凹部に埋め込まれた部分以外のバリアメタル膜3b上のCu膜5bを化学機械研磨によって除去する。そして配線凹部内のCu膜5b上に、添加元素からなる層6bを形成する。添加元素を層6bからCu膜5b中に拡散させて、Cu表面、及びCu結晶粒の粒界及び該粒界近傍の位置においてCu結晶粒内部よりも添加元素の濃度が高い界面及びその近傍を形成するとともに、Cu膜5b中の酸素を層6bにゲッタリングさせる。その後、余剰な層6bを除去し、さらに絶縁膜上のバリアメタル膜3bを除去する。

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

【課題】高い電荷移動度を有し、大面積表示装置に対して均一な電気的特性を得ることができる薄膜トランジスタ表示板及びその製造方法を提供する。

【解決手段】絶縁基板上に形成されたゲート電極と、前記ゲート電極上に形成されたSiNxから構成された第1ゲート絶縁膜と、前記第1ゲート絶縁膜の上に形成されたSiOxから構成された第2ゲート絶縁膜と、前記ゲート電極と重畳するように形成され、チャネル部を有する酸化物半導体層と、前記酸化物半導体層及び前記ゲート電極の上部に形成されたSiOxから構成された保護膜とを含み、前記保護膜はドレイン電極拡張部を露出するコンタクトホールを含む。ここで、前記コンタクトホールは、ドレイン電極拡張部を直接的に露出する部分の保護膜が、その上部の保護膜よりさらに狭い領域を占める形状を有する。

(もっと読む)

金属配線

【課題】従来の、真空装置を用いた形成方法に比べて簡便かつ安価に形成され、しかもインクジェット印刷方法によって形成されるもの比べて、断線等を生じることなしに、より細線化された金属配線を提供する。

【解決手段】Ag粒子、またはAgを50原子%以上含む合金粒子を含む分散液を塗布して塗膜を形成し、乾燥後にパターン形成したのち焼成して形成され、その縁部2における、基材の表面方向の、想定される外形線4からの凹入量の最大値と突出量の最大値との和が50nm以下、前記縁部2における、基材3の表面方向の、想定される外形線4と直交し、かつ金属配線1の厚み方向の断面のうち、前記厚み方向の外形線の、前記基材3の表面と接する部分の、前記基材3の表面との交差角度が70°以下で、かつ抵抗率が14μΩ・cm以下である。

(もっと読む)

半導体装置及び電子機器

【課題】マスク数を増加させることなく、ブラックマスクを用いずに反射型または透過型の表示装置における画素開口率を改善する。

【解決手段】画素間を遮光する箇所は、画素電極167をソース配線137と一部重なるように配置し、TFTはTFTのチャネル形成領域と重なるゲート配線166によって遮光することによって、高い画素開口率を実現する。

(もっと読む)

半導体装置の製造方法

【課題】バリア金属膜の膜厚を薄膜化でき、金属配線やビア内にボイドの無い配線を形成可能な半導体装置の製造方法を提供する。

【解決手段】半導体構造は、相互接続トレンチ又はビア305に薄いバリア金属層307が、トレンチやビアの開口が相互接続トレンチやビアへの銅の配置を疎外する張り出しにより妨害されないように形成される。銅の相互接続配線314を形成するための材料は、銅とマンガンを含んでいる。アニールにより、銅の拡散に対してバリア特性を有する酸化マンガン層315が形成される。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu系合金配線膜と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに密着性に優れた配線構造を提供する。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記半導体層と前記Cu合金層との間に、基板側から順に、窒素、炭素、フッ素、および酸素よりなる群から選択される少なくとも一種の元素を含有する(N、C、F、O)層と、CuおよびSiを含むCu−Si拡散層との積層構造を含んでおり、前記(N、C、F、O)層を構成する窒素、炭素、フッ素および酸素のいずれかの元素は前記半導体層のSiと結合しており、前記Cu合金層は、Cu−X合金層(第一層)と第二層とを含む積層構造である。

(もっと読む)

41 - 60 / 317

[ Back to top ]