Fターム[5F033MM13]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 配線の断面構造 (9,197) | 2種類以上の導電層よりなる配線 (8,898) | バリア層を含むもの (2,960)

Fターム[5F033MM13]に分類される特許

361 - 380 / 2,960

半導体装置の製造方法、配線用銅合金、及び半導体装置

【課題】半導体装置の歩留まりと信頼性を向上させる。

【解決手段】配線凹部に埋め込まれた部分以外のバリアメタル膜3b上のCu膜5bを化学機械研磨によって除去する。そして配線凹部内のCu膜5b上に、添加元素からなる層6bを形成する。添加元素を層6bからCu膜5b中に拡散させて、Cu表面、及びCu結晶粒の粒界及び該粒界近傍の位置においてCu結晶粒内部よりも添加元素の濃度が高い界面及びその近傍を形成するとともに、Cu膜5b中の酸素を層6bにゲッタリングさせる。その後、余剰な層6bを除去し、さらに絶縁膜上のバリアメタル膜3bを除去する。

(もっと読む)

成膜方法及び処理システム

【課題】比誘電率の低い絶縁層の表面にMn等の金属を含む薄膜、例えばMnOxを効率的に形成することが可能な成膜方法を提供する。

【解決手段】絶縁層1が表面に形成された被処理体Wに対して成膜処理を施す成膜方法において、第1の金属よりなる第1の薄膜60を形成する第1の薄膜形成工程と、前記第1の薄膜を酸化して酸化膜60Aを形成する酸化工程と、前記酸化膜上に第2の金属を含む第2の薄膜62を形成する第2の薄膜形成工程とを有する。これにより、比誘電率の低い絶縁層の表面にMn等の金属を含む薄膜、例えばMnOxを効率的に形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】ダイシング等で半導体装置を個片化する際に加工のダメージ又は膜の残留応力などに起因して発生する、基板上の膜の剥離を抑制することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置101,102の周辺すなわち個片化のための加工ラインの近傍の基板1上に溝6を形成する。その溝の内部では基板上に成膜される薄膜が少なくとも1部で不連続となることにより、万一、半導体装置の端部から膜剥がれが発生したとしても、この溝部でその進行を阻止する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】歩留まりに優れた構造を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板と、基板上に形成されており、配線および絶縁層により構成された配線層が複数積層された多層配線層と、平面視において、基板内の記憶回路領域に形成されており、多層配線層内に埋め込まれた少なくとも1以上の容量素子および周辺回路を有する記憶回路と、平面視において、基板内の憶回路領域とは異なる領域である論理回路領域に形成された論理回路と、を備え、容量素子は、下部電極、容量絶縁膜、上部電極、埋設電極および、上部接続配線で構成されており、上部接続配線と埋設電極とは、同一の材料かつ一体に構成されており、上部接続配線と下部電極との間には、論理回路を構成する前記配線が少なくとも1以上設けられており、上部接続配線の上面と、上部接続配線と同じ配線層に形成された論理回路を構成する配線の上面とが、同一面を構成する。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】Cuを主要な成分とする再配線に設けられた外部接続用Auパッドの剥離を抑制する。

【解決手段】Cu膜15aの上部にNi膜15bを積層した2層膜からなる再配線15の表面には、ワイヤが接続されるパッド18が形成されている。パッド18は、Ni膜19aの上部にAu膜19bを積層した2層膜からなり、再配線15の上面および側面を覆うように一体形成されている。これにより、再配線15とパッド18の接触面積が大きくなるので、パッド18が再配線15から剥がれ難くなる。

(もっと読む)

半導体装置の製造方法

【課題】信頼性が損なわれるのを防止しつつ、電気的特性の良好な半導体装置を提供する。

【解決手段】半導体基板10上に、化学気相堆積法により、シリコンと酸素と炭素とを含む絶縁膜42を形成する工程と、絶縁膜を形成する工程の後、350℃以下の温度で加熱しながら絶縁膜に対して紫外線キュアを行う工程と、紫外線キュアを行う工程の後、絶縁膜に対してヘリウムプラズマ処理を行う工程とを有している。

(もっと読む)

ウェットエッチング性に優れた表示装置用配線膜

【課題】ウェットエッチング性が良好な表示装置用配線膜を提供する。

【解決手段】希土類金属元素、Zn、Mg、およびCaよりなる群から選択される少なくとも一種の元素を5原子%以上50原子%以下の範囲で含むMo合金と、純CuまたはCu合金との積層構造を有する表示装置用配線膜である。

(もっと読む)

配線形成方法

【課題】配線層で、配線密度の高い領域では隣接する配線間のショートを防ぎ、配線密度の低い領域では所望の平坦度が得られるとともに所望の配線抵抗が得られるように配線高さを制御できる配線形成方法を提供する。

【解決手段】まず、基板上に第1の絶縁膜111と、第1の絶縁膜111に比してCMP研磨レートの小さい所定の厚さの第2の絶縁膜112を順に積層させて層間絶縁膜11を形成し、ついで、層間絶縁膜11の第1の領域に第1の配線密度となり、第2の領域に第1の配線密度よりも低い第2の配線密度となるように、第2の絶縁膜112を貫通し、底部が第1の絶縁膜111に至る配線形成用溝21を形成した後、配線形成用溝21を形成した層間絶縁膜11上に導電性材料膜14を形成し、そして、CMP法によって、少なくとも第1の領域で第1の絶縁膜111が露出、後退するように層間絶縁膜11と導電性材料膜14を研磨する。

(もっと読む)

半導体装置およびその製造方法

【課題】積層される半導体基板同士が、貫通孔の内部に埋め込まれる導電体により、電気的に良好に接続される半導体装置を提供する。

【解決手段】第1半導体基板SCPは、主表面を有する基板SUBと、基板SUB内および基板SUB上に形成された半導体素子TRと、半導体素子TRに電気的に接続された配線MTLと、基板SUBの主表面であり、互いに対向する第1主面と第2主面とを貫通し、配線MTLに達する貫通孔の内部に形成された導電層TSVとを有する。第1半導体基板SCPと第2半導体基板SCPとが積層され、導電層TSVは第2半導体基板SCPの配線MTLと電気的に接続される。導電層TSVの第2主面では、貫通孔の端部の周囲には凹部DUMが形成され、凹部DUMの底壁面は基板SUBの内部に存在する。導電層TSVを構成する導電材料CUが凹部DUMの内部に充填される。

(もっと読む)

半導体装置及びその製造方法

【課題】low−k膜のワイヤーボンディング時の荷重による変形やクラッキングの発生を回避し、半導体装置の信頼性の低下を抑制することが可能な半導体装置とその製造方法を提供する。

【解決手段】半導体装置において、基板上に形成された絶縁層と、絶縁層上に形成された複数の層間絶縁膜と、層間絶縁膜中にそれぞれ形成される複数の配線層及びビアからなる多層配線と、複数の配線層のうち最下層の配線層より基板側に形成されたメタルパッドと、メタルパッドの一部の領域上の絶縁層及び層間絶縁膜が除去されて形成された開口部と、メタルパッド上に、複数の層間絶縁膜を貫通し、開口部を取り囲むように設けられるパッドリングと、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトプラグを、配線のバリア層に安定して接続できる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、バリア層を介して配線に接続されたコンタクトプラグ、第1及び第2の絶縁膜を有する。第1の絶縁膜は、配線及びバリア層の側面を覆い少なくともバリア層よりも上方で配線が延在する方向と直交する方向の幅が狭まる傾斜面を有し、バリア層の上面の一部を露出すると共に配線及びバリア層の側面を露出させないように形成された開口部を備える。第2の絶縁膜は、開口部の内側を除き第1の絶縁膜上に形成され、かつ開口部を備える。

(もっと読む)

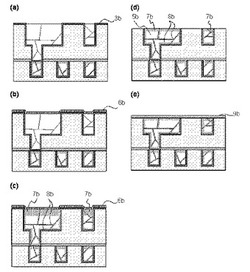

配線構造の形成方法および配線構造

【課題】太い幅の配線溝と細い幅の配線溝をCuの電解メッキで充填する際に、アンダープレートの発生を抑制し、化学機械研磨後におけるディッシングの発生を抑制する。

【解決手段】表面の第1の領域に縦/横比小さい第1の配線溝22Aが形成され、表面の第2の領域に縦/横比が大きい第2の配線溝22Bを形成された絶縁膜の表面上にレジスト膜R1を形成し、第1の領域を露出する第1のレジスト開口部R1Aを形成する工程と、レジスト膜をマスクに電解メッキを行い、第1の配線溝を第1の配線パタ―ン25Aで充填する工程と、第2の領域を露出する第2のレジスト開口部を形成する工程と、レジスト膜をマスクに電解メッキを行い、第2の配線溝を第2の配線パタ―ンで充填する工程と、レジスト膜を除去し、第1の配線パタ―ンおよび第2の配線パタ―ンを、それぞれの表面が絶縁膜の表面に一致するように、化学機械研磨により平坦化する工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、製造コストの増加を抑制可能な半導体装置を提供する。

【解決手段】半導体装置1は、半導体基板部10、誘電体膜22、再配線24、上部電極25、絶縁膜26、及び外部接続端子28を有する。半導体基板部10は、回路が形成され、回路にそれぞれ接続される下部電極15、上部電極パッド16、接続パッド17、18を上面に有する。誘電体膜22は、下部電極15を被い、上部電極パッド16、接続パッド17、18の上面に達する開口部を有する。再配線24は、一部の接続パッド17、18に電気的に接続される。上部電極25は、誘電体膜22を介して下部電極15の上面に対向して配置され、上部電極パッド16に接続され、再配線24を含む。絶縁膜26は、誘電体膜22、再配線24、及び上部電極25を被う。外部接続端子28は、絶縁膜26を貫通し再配線24に接続され、絶縁膜26の上面から露出する。

(もっと読む)

半導体装置の製造方法

【課題】ポーラスLow−k膜の信頼性を向上させる。

【解決手段】プラズマCVD法によって層間絶縁膜IL2を形成する際にCVD装置内に供給するポロジェンの流量を、ポロジェンおよびメチルジエトキシシランの合計の流量の30%以上60%以下とすることで、層間絶縁膜IL2内に形成される空孔10の大きさを小さくし、プロセスダメージによって層間絶縁膜IL2の表面に変質層CLが形成されることを防ぐ。また、水分を含む変質層CLの形成を抑えることで、各配線を構成するバリア膜および主導体膜の酸化を防ぎ、各配線間の耐圧の劣化を防ぐ。これにより、層間絶縁膜IL2に隣接して形成される配線のEM寿命および前記配線の線間TDDB寿命の劣化を防ぐ。

(もっと読む)

電子部品の製造方法及び電解めっき装置

【課題】シード膜の溶解を抑制し、電解めっき後のめっき膜の未析や欠陥の発生を低減する方法を提供する。

【解決手段】実施形態の電子部品の製造方法は、シード膜形成工程S110とめっき工程S114とを備えたことを特徴とする。かかるシード膜形成工程S110では、基体上にシード膜を形成する。そして、かかるめっき工程S114では、窒素ガスでバブリングされているめっき液が供給されためっき槽中の前記めっき液に前記シード膜を浸漬させ、前記シード膜をカソードとして電解めっきを行なう。

(もっと読む)

半導体装置およびその製造方法ならびに半導体ウエハ

【課題】ダイシングブレードの寿命を延ばすことができるとともに、半導体装置のエッジ部へのダメージを低減できる半導体装置を提供する。

【解決手段】機能素子領域2においては、第3層間絶縁膜27表面とパッシベーション膜33との間には、下配線25に接続される上配線29およびキャップメタル層32が形成されている。下配線25はCu以外の配線材料からなり、上配線29はCuからなる。このキャップメタル層32におけるパッシベーション膜33のパッド開口34から露出した部分が第1パッド6である。一方、スクライブ領域3においては、第3層間絶縁膜27表面とパッシベーション膜33との間には、下配線25に接続されるキャップメタル層32が形成されている。このキャップメタル層32におけるパッシベーション膜33のパッド開口44から露出した部分が第2パッド10である。

(もっと読む)

半導体装置及びその製造方法

【課題】下層の金属配線のダメージがなく上層の金属配線が形成され、かつ、配線間の寄生容量が低減された半導体装置及びその製造方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板上に設けられた第1の金属配線層と、

前記第1の金属配線層上に設けられ、該第1の金属配線層の金属の拡散を防止する拡散防止膜と、前記拡散防止膜上に設けられた第1の絶縁膜と、前記第1の絶縁膜上に設けられた、前記拡散防止膜と同じ材料からなる第2の絶縁膜と、前記第2の絶縁膜上に設けられた第3の絶縁膜と、前記拡散防止膜、前記第1の絶縁膜、前記第2の絶縁膜及び前記第3の絶縁膜に形成された接続孔に充填され、前記第1の金属配線層に電気的に接続された第2の金属配線層と、を備えたことを特徴とする。

(もっと読む)

配線回路基板及びその製造方法

【課題】配線回路基板において、コンタクト抵抗の上昇を抑制し、熱応力による断線を防止することのできるコンタクト構造を提供する。

【解決手段】 配線回路基板は、第1配線層(5)、第2配線層(7)、及び前記第1配線層と前記第2配線層を電気的に接続するコンタクト配線(6)を有する。前記コンタクト配線は、前記第1配線層のコンタクト面を被覆する第1被覆部(6a)と、前記第2配線層のコンタクト面を被覆する第2被覆部(6c)と、前記第1被覆部と前記第2被覆部の間に延びるプラグ部(6b)を有する。前記第1被覆部、前記プラグ部、及び前記第2被覆部は、同一の導電性材料で一体的に形成された内部に界面のないコンタクト配線である。

(もっと読む)

半導体装置の製造方法

【課題】ボイドとヒロックの発生の双方を抑制してCu配線を形成する。

【解決手段】半導体基板上の層間絶縁膜に溝パターンを形成する工程(S1)、めっき法によりCu膜を形成する工程(S2,S3)、130〜180℃で第1アニールを行う工程(S4)、CMPにより溝パターン以外の銅膜を除去する工程(S5)、300〜350℃でグレイン成長のための第2アニールを行う工程(S6)とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を向上させる。また、半導体装置の製造工程を簡略化する。

【解決手段】SOI基板SB上に形成された複数のnチャネル型MOSFETQnを有する半導体装置において、BOX膜の下部の支持基板の上面に拡散層であるn+型半導体領域を形成し、n+型半導体領域と電気的に接続され、素子分離領域1を貫くコンタクトプラグCT2を形成することで、支持基板の電位を制御する。SOI基板SBの平面において、各nチャネル型MOSFETQnは第1方向に延在しており、第1方向に複数形成されて隣り合うコンタクトプラグCT2同士の間に配置された構造とする。

(もっと読む)

361 - 380 / 2,960

[ Back to top ]