Fターム[5F033MM13]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 配線の断面構造 (9,197) | 2種類以上の導電層よりなる配線 (8,898) | バリア層を含むもの (2,960)

Fターム[5F033MM13]に分類される特許

141 - 160 / 2,960

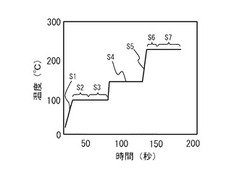

半導体装置の製造方法

【課題】反射防止膜を確実に除去して半導体装置の欠陥発生を低減する。

【解決手段】第1の層間絶縁膜の上に、絶縁膜と、反射防止膜と、レジスト膜とを順番に形成する。レジスト膜を用いて反射防止膜と絶縁膜をエッチングし、絶縁膜からハードマスクを作成する。この後、ラジカル照射によってレジスト膜と反射防止膜を除去する。ラジカル照射は、基板温度を100℃、150℃、250℃と順番に上昇させながら行う。基板温度が低い初期段階では、反射防止膜の膜材料の飛散防止と、反射防止膜の表面に残留する他の物質の除去が行われる。この後、基板温度を高くすることで、反射防止膜が確実に除去される。

(もっと読む)

半導体装置

【課題】信頼性を向上させた半導体装置の作製方法の提供を課題とする。

【解決手段】基板上に第1の導電層を形成する工程と、第1の導電層上に、金、銀または

銅の導電性粒子(導電性微粒子ともよぶ)と樹脂を含む第2の導電層を形成する工程と、

第2の導電層にレーザービームを照射して、前記第1の導電層と前記第2の導電層が接す

る面積(部分)を増加させる工程とを含む半導体装置の作製方法を提供する。レーザービ

ームを照射する工程を含むことにより、第1の導電層上に、導電性粒子と樹脂からなる第

2の導電層を形成した場合でも、第1の導電層と第2の導電層が接する部分を増加させ、

第1の導電層と第2の導電層の間の電気的な接続不良を改善することができる。

(もっと読む)

電力用半導体装置及びその製造方法

【課題】本発明は、信頼性の高い外部電極との接続構造を有する電力用半導体装置及びその製造方法の提供を目的とする。

【解決手段】本発明の電力用半導体装置は、段差を有する絶縁膜9と、絶縁膜9の前記段差を覆って形成された上部配線10と、上部配線10上の少なくとも前記段差の側壁に対応する部分を含む所定箇所に、部分的に形成された酸化膜16と、上部配線10及び酸化膜16上に形成され、半田21により外部導体22と接合するバリア層20とを備える。

(もっと読む)

半導体装置の製造方法

【課題】コンタクトホール内に良好にAl膜が埋設されたコンタクトプラグを有する半導体装置を提供する。

【解決手段】半導体装置の製造方法は、基板の層間絶縁膜内にコンタクトホールを形成する工程と、基板を加熱した状態でコンタクトプラグを形成する工程を有する。コンタクトプラグを形成する工程では、スパッタ装置のチャンバー内のステージ上に、チャックを介して基板を保持し、チャックに印加するESC電圧を第一の電圧、第二の電圧、第三の電圧と、この順に3段階のステップ状に増加させる。チャンバー内のターゲットに対して第一のターゲット電力を印加してコンタクトホール内に第一のAl膜を成膜する。次に、チャンバー内のターゲットに対して第一のターゲット電力よりも高い第二のターゲット電力を印加して第一のAl膜上に第二のAl膜を成膜する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線層中の配線をゲート電極として使用し、かつ拡散防止膜と同一層にゲート絶縁膜を有している半導体素子を有する半導体装置において、拡散防止膜の機能を損なうことなく、半導体素子のオン抵抗を低くする。

【解決手段】第1配線層150を構成する絶縁層の表層には、第1配線154及びゲート電極210が埋め込まれている。第1配線層150と第2配線層170の間には、拡散防止膜160が形成されている。ゲート絶縁膜230は、拡散防止膜160のうちゲート電極210と重なる領域及びその周囲の上面に凹部を形成し、この部分を薄くすることにより、形成されている。

(もっと読む)

半導体装置の製造方法

【課題】王水を用いることなくニッケルプラチナ膜の未反応部分を選択的に除去しうるとともに、プラチナの残滓が半導体基板上に付着するのを防止しうる半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極16と、ゲート電極16の両側のシリコン基板10内に形成されたソース/ドレイン拡散層24とを有するMOSトランジスタ26を形成し、シリコン基板10上に、ゲート電極16及びソース/ドレイン拡散層24を覆うようにNiPt膜28を形成し、熱処理を行うことにより、NiPt膜28とソース/ドレイン拡散層24の上部とを反応させ、ソース/ドレイン拡散層24上に、Ni(Pt)Si膜34a、34bを形成し、過酸化水素を含む71℃以上の薬液を用いて、NiPt膜28のうちの未反応の部分を選択的に除去するとともに、Ni(Pt)Si膜34a、34bの表面に酸化膜を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】基板を実装する際の温度負荷によって絶縁層と下地金属層の側面との接点領域に加わる応力を緩和させ、応力に起因した絶縁層のクラックの発生を抑えるように構成された半導体装置を提供する。

【解決手段】半導体基板101の一面101aに、絶縁層102、下地金属層103、金属端子が設けられるためのランド部104を順に積層してなる半導体装置109であって、ランド部104は、絶縁層102と対向する面の中央部において、下地金属層103と接合する接合領域と、絶縁層102と対向する面において、接合領域を除いた非接合領域と、を有し、下地金属層103は、ランド部104側から絶縁層102側にかけて外向きに傾斜した側面を有していること、を特徴とする半導体装置109。

(もっと読む)

パターン転写方法

【課題】エッチングを行わずに残膜除去処理を行うことが可能なパターン転写方法を提供する。

【解決手段】実施形態のパターン転写方法では、被加工基板上に光反応性樹脂を形成する。さらに、前記方法では、凹凸パターンを有する透明基板と、前記凹凸パターンの表面の一部に形成された遮光膜と、を備えるモールドを前記光反応性樹脂に押印する。さらに、前記方法では、前記モールドが前記光反応性樹脂に押印された状態で、前記モールドを介して前記光反応性樹脂に光を照射する。さらに、前記方法では、前記光反応性樹脂に光を照射した後に、前記モールドが前記光反応性樹脂に押印された状態で、前記光反応性樹脂を加熱する。さらに、前記方法では、前記光反応性樹脂の加熱後に、前記モールドを前記光反応性樹脂から離型する。さらに、前記方法では、前記モールドの離型後に、前記光反応性樹脂を洗浄液で洗浄する。

(もっと読む)

Cu合金膜および表示装置

【課題】酸化物半導体層を用いた表示装置において、保護膜形成時のプラズマ処理におけるCu配線の酸化を有効に防止し得る技術を提供する。

【解決手段】基板1の上に、基板側から順に、薄膜トランジスタの半導体層4と、電極に用いられるCu合金膜5と、保護膜6と、を備えており、半導体層は酸化物半導体からなる。Cu合金膜5は、基板側から順に、第一層(X)5aと第二層(Z)5bを含む積層構造を有し、第一層(X)は、純Cu、またはCuを主成分とするCu合金であって第二層(Z)よりも電気抵抗率の低いCu合金からなり、第二層(Z)は、Zn、Ni、Ti、Al、Mg、Ca、W、Nb、希土類元素、Ge、およびMnよりなる群から選択される少なくとも1種の元素を合計で2〜20原子%含むCu−Z合金からなり、第二層(Z)の少なくとも一部は、前記保護膜と直接接続されている。

(もっと読む)

半導体装置

【課題】 より信頼性の高い接合界面を有する半導体装置を提供する。

【解決手段】 半導体装置100を、第1半導体部と、第2半導体部とを備える構成とする。第1半導体部には、接合界面側の表面に形成されかつ第1の方向に延在する第1電極16を設ける。そして、第2半導体部には、接合界面で第1電極16と接合されかつ第1の方向と交差する第2の方向に延在する第2電極26を設ける。

(もっと読む)

半導体装置の製造方法と半導体装置

【課題】半導体基板の表面のAl層の表面が荒れることを抑制しつつ、リフトオフの後に溶解層が剥離せずに残ることを防止し得る半導体装置の製造方法を提供する。

【解決手段】半導体基板12の表面にAl層14を形成し、Al層14の表面にTiN層16を形成し、TiN層16の表面の一部に絶縁層20を形成し、TiN層16と絶縁層20の表面に溶解層を形成し、溶解層の表面にレジスト層を形成し、溶解層とレジスト層の一部を除去して溶解層開口部を形成してTiN層16の一部を露出させ、レジスト層の表面、及び、露出したTiN層16の一部の表面にTi層30及びNi層40を形成し、アルカリ溶液によって溶解層を溶解させることにより、溶解層とともに、レジスト層とその表面に形成されたTi層及びNi層を除去する。

(もっと読む)

半導体装置の製造方法

【課題】基板のエッジ部分での膜剥がれを防止し、半導体装置を効率良く製造する。

【解決手段】基板1の上方に低誘電体膜31を形成する際に、基板1のエッジ部分1Aをエッジカット工程にて洗い流すことで段差部31Aが形成される。低誘電体膜31に配線溝41を形成した後、導電膜43を埋め込む。基板1のエッジ部分1Aの導電膜43を洗い流すと、導電膜43が埋め込まれていない配線溝41Aが形成される。配線溝41Aを保護フィルム51で覆ってから、CMP法にて余分な導電膜43を除去する。この後、保護フィルム51を基板1から取り外す。

(もっと読む)

半導体装置およびその製造方法

【課題】ダイシング工程で発生する膜剥離やクラックがチップ内部に伝播するのを防ぐ。

【解決手段】半導体装置100は、基板102と、ビア層130および配線層132が形成される素子形成領域であるチップ内部202と、平面視においてチップ内部202を囲むようにチップ内部202の外周に形成されたシールリング部204と、を含む。シールリング部204において、シールリングは、平面視においてチップ内部202を囲むように形成された貫通孔122aを有する第1のメタル層122と、第1のメタル層122上に第1のメタル層122に接して形成された第2のメタル層124と、を含み、第1のメタル層122の貫通孔122aの下部分には絶縁性材料(層間絶縁膜106)が形成され、貫通孔122aの上部分には第2のメタル層124を構成するメタル材料がくい込んで形成される。

(もっと読む)

半導体装置

【課題】パッドの下方に半導体素子を設けることができ、信頼性の高い半導体装置を提供する。

【解決手段】素子形成領域10Aと該素子形成領域10Aの周囲に設けられた素子分離領域20とを有する半導体層10と、前記素子形成領域10A内に形成された素子30と、前記半導体層10の上方に設けられた層間絶縁層60と、前記層間絶縁層60の上方に設けられ、平面形状が短辺と長辺とを有する長方形である電極パッド62であって、前記素子30と平面視で少なくとも一部が重複する前記電極パッド62と、を含み、前記半導体層10において、前記電極パッド62の前記短辺の鉛直下方から外側に位置する所定の範囲は、素子禁止領域12である。

(もっと読む)

半導体装置の製造方法

【課題】貫通電極の形成過程で、余分な酸化膜を確実に除去する。

【解決手段】貫通電極を形成するビアホール25の内面に酸化膜26を形成した後、Cu膜28を埋め込む。第1層間絶縁膜22の上に形成された余分なCu膜28をCMP法による研磨で除去するときに、酸化膜26も研磨されて膜厚が薄くなる。膜厚が薄くなった酸化膜26Bをハードマスクとして第1層間絶縁膜14に配線溝を形成する。このとき、酸化膜26Bの膜厚が薄くなる。配線溝に導電材を埋め込んだ後、余分な導電材を研磨によって除去する。このとき、残りの酸化膜26Bが全て研磨により除去される。

(もっと読む)

半導体装置の製造方法

【課題】 低k膜と金属マスクとの間の界面に歪みを引き起こすことなく、高い精度の望ましいパターンを得ること。

【解決手段】 半導体装置を製造する方法では、金属マスクと絶縁マスクをと備える多層ハードマスクを用いて形成される配線層を含む半導体装置が形成される。第1パターンにアラインされた第2開口パターンを形成するために、第1ステップで多層ハードマスクが使用された後、金属マスクが除去され、絶縁マスクが、第2のステップで絶縁層中に第1のパターン構造を形成するために使用される。

(もっと読む)

誘電フィルム及び材料における疎水性を回復する方法

【課題】誘電率の増加、シラノールの増加、または有機部分の減少、の少なくとも一つによって損傷した、基体上のシリカ誘電フィルムの損傷を回復する。

【解決手段】基体上のそのような損傷シリカ誘電フィルムを表面改質組成物と接触させて、該損傷シリカ誘電フィルムの誘電率の減少、該損傷シリカ誘電フィルムの誘電率のシラノールの減少、該損傷シリカ誘電フィルムの誘電率の有機部分の増加、の1つ以上をもたらす。このとき、該損傷シリカ誘電フィルムに疎水性を与える。

(もっと読む)

無電解薄膜析出法により平坦化銅相互接続層を形成する方法および装置

【課題】基板に定形された形態部の内部に、表面が平坦化された導電性材料を形成する方法を提供する。

【解決手段】平坦化表面を形成する方法であって、狭小形態部と幅広形態部が形成された基板上に、第1のプロセスでは電気めっき法により狭小形態部および幅広形態部の少なくとも一部を充填し、第1の層を形成し、第2のプロセスでは無電解めっき法により幅広形態部のに対応する第1の層中の孔および第1の層上に第2の層を充填形成し、表面が平坦な上層部110を形成する。

(もっと読む)

複数の開口部を備える基板上への層の蒸着方法

【課題】多孔性低誘電率絶縁膜のトレンチおよびビア内にカバレージ良くライニング層を形成する半導体装置の製造方法を提供する。

【解決手段】第1パルス期間に供給される第1反応物と、第2パルス期間に供給される第2反応物とを利用する原子層堆積(ALD)プロセスにより成膜する。まずシーリング層を低コンフォマリティーを有する条件で成膜し、ポアをブロックする。この後、接着層を高いコンフォマリティーを有する条件で成膜する。

(もっと読む)

半導体装置、半導体装置の製造方法、固体撮像装置及び電子機器

【課題】 ビア形成時のエッチングによる基板や配線への影響を抑制しつつ積層された半導体ウェハの回路どうしを接続する。

【解決手段】 半導体装置の製造方法は、第1基板と第1基板の一面と接するように形成された第1絶縁層を有する第1の半導体ウェハと、第2基板と第2基板の一面と接するように形成された第2絶縁層を有する第2の半導体ウェハを接合する工程と、第1基板の他面に第3絶縁層を形成する工程と、第3絶縁層、第1基板、及び第1絶縁層を貫通し第2絶縁層に形成された第2の配線上に第2絶縁層が残るようにエッチングを行い第1接続孔を形成する工程と、第1接続孔に絶縁膜を形成する工程と、第2の配線上の第2絶縁層及び絶縁膜のエッチングを行い第2接続孔を形成し第2の配線を露出させる工程と、第1及び第2接続孔の内部に形成され第2の配線と接続する第1のビアを形成する工程とを備え、第1基板の他面に形成された第1接続孔の径は第3絶縁層に形成された前記第1接続孔の径より大きい。

(もっと読む)

141 - 160 / 2,960

[ Back to top ]