Fターム[5F033MM26]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 表面状態 (80) | 配線の表面に凹凸やうねりがあるもの (72)

Fターム[5F033MM26]に分類される特許

1 - 20 / 72

半導体装置及びその製造方法

【課題】個別の工程で形成されることで分離して配置された電極どうしを断線することなく接続できる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板の主面に第1の絶縁膜を介して形成された第1の電極と、半導体基板の主面に第2の絶縁膜を介して形成された第2の電極との間に補償膜を埋設する。第1の電極及び第2の電極上には、第1の電極の上面及び第2の電極の上面と接触する、第1の電極の上面から補償膜の上面を経由して第2の電極の上面まで到達する配線を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】信号速度の遅延を防止することができる半導体装置を提供する。

【解決手段】本実施形態の半導体装置は、基板上に成膜された第1の絶縁膜と、配線と、第2の絶縁膜とを持つ。前記配線は、前記第1の絶縁膜に互いに平行に所定間隔で形成されたトレンチを埋め込むように金属で形成される。前記第2の絶縁膜は、前記第1の絶縁膜と前記配線とを覆うように前記第1の絶縁膜よりも誘電率の高い材料で成膜される。前記配線間の領域における前記第2の絶縁膜の下面は、前記配線の上面の周縁を互いに結ぶ面に対して上方へ離隔している。

(もっと読む)

半導体装置の製造方法と半導体装置

【課題】本発明は、絶縁膜を金属に密着させることができる半導体装置の製造方法と半導体装置を提供することを目的とする。

【解決手段】本願の発明に係る半導体装置の製造方法は、基板上に多結晶の金属を形成する工程と、該金属の表面粗さRaが0.051μmより大きくなり、かつ該金属の表面に1〜10μm径のランダムな方向に伸びる複数の穴が形成されるように、該金属の表面を1.0μm/min未満のエッチングレートでウェットエッチする工程と、該金属の表面に絶縁膜を形成する工程と、を備えたことを特徴とする。

(もっと読む)

半導体集積回路装置およびその製造方法ならびにそれを用いた電子システム

【課題】再配線のランド部にバンプ電極が接続された半導体集積回路装置において、再配線と半田バンプとの接着強度を向上させる。

【解決手段】再配線20のランド部20Aは、再配線20を構成する5層の金属膜(バリアメタル膜13、シード膜14、Cu膜15、第1Ni膜16および第2Ni膜17)のうち、最上層の第2Ni膜17の面積が他の金属膜(バリアメタル膜13、シード膜14、Cu膜15、第1Ni膜16)の面積よりも大きくなるように構成され、この第2Ni膜17の表面に半田バンプ21が接続されている。そして、半田バンプ21の端部では、第2Ni膜17の直下にポリイミド樹脂膜22が形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電極パッド部の安定した電気的接触を確保しつつ電極パッド部の面積を小さくすることができる半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板の主表面上であって平面視において素子形成領域内およびダイシングライン領域内の少なくともいずれかに形成された半導体チップ用電極パッド部,TEG用電極パッド部PTとを備えている。半導体チップ用電極パッド部,TEG用電極パッド部PTは、外部と電気的に接続するための表面OSFを有し、かつ半導体チップ用電極パッド部,TEG用電極パッド部PTの辺SIDに対して斜めに傾斜した方向に延びた溝部THPを表面OSFに有している。

(もっと読む)

半導体装置

【課題】画素部に形成される画素電極やゲート配線及びソース配線の配置を適したものとして、かつ、マスク数及び工程数を増加させることなく高い開口率を実現した画素構造を有するアクティブマトリクス型表示装置を提供することを目的とする。

【解決手段】絶縁表面上のゲート電極及びソース配線と、前記ゲート電極及びソース配線上の第1の絶縁層と、前記第1の絶縁膜上の半導体層と、前記半導体膜上の第2の絶縁層と、前記第2の絶縁層上の前記ゲート電極と接続するゲート配線と、前記ソース電極と前記半導体層とを接続する接続電極と、前記半導体層と接続する画素電極とを有することを特徴としている。

(もっと読む)

半導体装置及びその製造方法

【課題】工程数を増やさずに、安価な装置を用いてプロ―ビング位置の目視観察を可能にする。

【解決手段】本発明の半導体装置は、多層配線層(図示せず)と、多層配線層の最上層に形成され、ボンディング領域P1と試験用プローブ接触領域P2とを含むボンディングパッド200を有する。ボンディングパッド200には、ボンディング領域P1と試験用プローブ接触領域P2との境界を表す凹部202が形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電極パッドのプローブ領域とボンディング領域とを、光学顕微鏡による拡大観察で明確に識別することができる半導体装置を提供する。

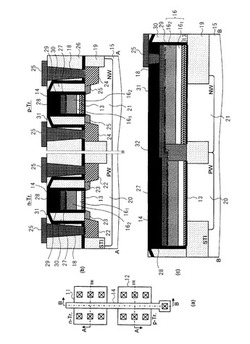

【解決手段】半導体基板に形成された回路と接続される下層メタル配線20と、下層メタル配線20の上に形成され、複数のビアホール35、36を有する層間絶縁膜30と、複数のビアホール35、36を埋める複数の配線部40と、層間絶縁膜30及び複数の配線部40の上に形成され、複数の配線部40を介して下層メタル配線20と電気的に接続する上層メタル配線50とを具備する。層間絶縁膜30は、複数の第1ビアホール35を有する第1絶縁部31と、複数の第2ビアホール36を有する第2絶縁部32と、第1絶縁部31と第2絶縁部32との間に位置し、上面が平らな第3絶縁部33とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の高い半導体装置を効率良く製造できるようにする。

【解決手段】半導体装置31は、回路基板1の所定位置に形成された電極パッド10を有し、電極パッド10には、半導体装置21のハンダバンプ26が接合されている。ハンダバンプ26は、半導体装置21の電極25上に形成され、そのハンダ材料には鉛フリーハンダが用いられている。回路基板1の電極パッド10は、複数の凸部10Aと溝10Bが形成されており、ハンダバンプ26は、その一部が電極パッド10の溝10Bを埋めるように入り込んでいる。

(もっと読む)

半導体装置

【課題】SRAM回路の動作速度を向上させる。

【解決手段】駆動MISFETと転送MISFETとそれらの上部に形成された縦型MISFETとでメモリセルを構成したSRAMにおいて、周辺回路を構成するMISFET間の電気的接続を、メモリセルの縦型MISFET(SV1、SV2)よりも下部に形成されるプラグ28および中間導電層46、47で行うとともに、縦型MISFET(SV1、SV2)よりも上部に形成されるプラグ、第1および第2金属配線層を用いて行うことにより、配線の自由度を向上でき、高集積化できる。また、MISFET間の接続抵抗を低減でき、回路の動作スピードを向上できる。

(もっと読む)

半導体装置

【課題】多層配線構造において、測定パッドとバンプ等形成用の外部接続パッドの構造をそれぞれの用途に合わせて最適化する。

【解決手段】半導体装置100は、測定パッド2と外部接続パッド3を有している。測定パッド2は、その周端部に沿って20個のビアコンタクトが配置され、当該ビアコンタクトが形成されていない平坦な中央部を有し、当該中央部は、測定用のプローブ針が接触されるプローブ針接触領域2Aになっている。外部接続パッド3は、9個のビアコンタクトが配置され、当該ビアコンタクトが配置されることにより凹凸のある領域を有し、当該領域は、外部接続媒体が形成される外部接続媒体形成領域3Aになっている。

(もっと読む)

半導体装置

【課題】プローブ痕上にレジスト膜及び表面保護膜が形成されないなどの不具合が生じるのを抑えることが可能な半導体装置を提供する。

【解決手段】本発明の半導体チップは、半導体集積回路と、半導体集積回路と電気的に接続され、表面に突起部12を有する検査用パッド201とが同一面上に設けられた半導体基板を備え、半導体集積回路の検査時に、プローブが検査用パッド201と接触した状態で検査用パッド201の表面を押し出し、検査用パッド201の表面には、検査時にプローブにより押し出された検査用パッド201の一部が突起部12と接するようにプローブ痕61として形成され、突起部12の幅は、プローブ痕61の幅よりも狭い。

(もっと読む)

配線構造およびその製造方法、並びに配線構造を備えた表示装置

【課題】基板側から順に、Al合金膜と、当該Al合金膜と直接接続する薄膜トランジスタの酸化物半導体層と、を有し、TiやMoなどの高融点金属を省略してAl合金膜を酸化物半導体層と直接接続しても低コンタクト抵抗を実現できる新規な表示装置用Al合金膜を有する配線構造を提供する。

【解決手段】上記配線構造において、半導体層は酸化物半導体からなり、Al合金膜は、Niおよび/またはCoを含むものである。

(もっと読む)

半導体装置の製造方法、半導体装置、及び半導体製造装置

【課題】樹脂突起の成型時に導電膜に変形が生じ、導電膜が断線することを防止する。

【解決手段】まず、保護絶縁膜120上に選択的に硬化型の樹脂層を形成することにより、複数の外部接続端子それぞれのコアとなる複数の凸部202を形成する。次いで、凸部202を硬化させる前に、対向面22(表面)が平坦である成型用治具20を複数の凸部202の上面に押し付けることにより、複数の上面それぞれに平坦部を形成する。次いで、複数の凸部202を硬化させる。ついで、複数の凸部202、保護絶縁膜120、及び複数の電極パッド130上に導電膜を選択的に形成することにより、複数の外部接続端子、及び複数の配線を形成する。

(もっと読む)

電子デバイス及びその製造方法、並びに電子機器

【課題】製造プロセスを増加させずに、信頼性が高く、かつ反射特性に優れる電子デバイスを提供する。

【解決手段】本発明に係る電子デバイス200は、基板1と、基板1上に形成され、少なくともMo系膜41と、その上層に形成されたAl系膜42とからなる導電性反射膜40とを備える。そして、導電性反射膜40のMo系膜41の表面荒さRaが5nm以下であり、Al系膜42の波長350nm〜550nmにおける反射率が85%以上である。

(もっと読む)

半導体装置

【課題】 半導体素子のサイズを大きくすることなく、プロービング試験の際にボンディング領域に針跡が到達していないかどうかを容易に確認することができる構造を備えた半導体装置を提供する。

【解決手段】 半導体装置は、半導体基板上に設けられた第1の金属層26と、前記第1の金属層26上に設けられた絶縁層30と、前記絶縁層30上に設けられ、外部に露出した電極パッド面33a、33bを有する第2の金属層33と、を含み、前記第2の金属層33及び前記絶縁層30に、凹部31が形成されており、前記絶縁層30の前記凹部31内に、前記第2の金属層33が設けられていることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】プローブとパッドとを低接触抵抗で相互に電気的に接続させ、安定した特性検査を行うことができる方法の提供。

【解決手段】半導体装置は、電気的特性の検査を行う検査装置のプローブ8が接触されるパッド9を備え、パッド9の少なくとも表層部には、凹部21の内径がプローブ8の先端部8aよりも小径であり、凸部22の頂部が平坦である凹凸形状が形成されている。この構造により、パッド9上でオーバードライブされるプローブ8の先端部8aとパッド9の表面との摩擦を大きくすることができる。オーバードライブの際に、パッド9の表面に元々生成されている絶縁物をプローブ8の先端部8aで掻き取るようにして十分に剥がすことができる。こうすることで、プローブ8とパッド9とを低接触抵抗で相互に電気的に接続させ、安定した特性検査を行うことができる。

(もっと読む)

半導体装置及びその製造方法

【課題】 ビアホールの微細化及び高アスペクト比化が進むと、銅からなるシード層でビアホールの内面を連続的に覆うことが困難になる。

【解決手段】 半導体基板(10)の上に絶縁膜(20)が形成されている。絶縁膜に凹部(21)が形成されている。凹部の内面を第1の導電膜(22)が覆う。島状組織(25)が、第1の導電膜の表面に離散的に分布する。島状組織は、銅に対して、第1の導電膜の濡れ性よりも高い濡れ性を有する。凹部が、銅または銅合金からなる導電部材(31)で充填されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置に設けられた半導体部品等の電極パッドとそれに接続されるべくインクジェット法により形成される配線との電気的な接続を好適に確保することのできる半導体装置、及びその半導体装置の製造方法を提供する。

【解決手段】半導体装置の第2電極パッド15に電気的に接続される金属配線膜19が、銀微粒子を分散媒に分散させた導電性インクからなる液滴(液層25L)の配置及び乾燥により形成される。このとき、第2電極パッド15の表面のメッキ層21に銀微粒子の結合層からなる中間層23Dを形成した後、中間層23Dを覆うかたちに上記分散媒を撥液する撥液材料を含む撥液層24を積層する。これにより、金属配線膜19は、その乾燥焼成を通じて中間層23Dと物理的に接続するようになり、撥液層24を間に挟みつつ第2電極パッド15と物理的に接続され、すなわち電気的にも接続されるようになる。

(もっと読む)

表示装置

【課題】動作特性に優れ低温で製造可能な酸化物半導体を用いた表示装置の特性を活かすには、適切な構成を備えた保護回路等が必要となる。

【解決手段】ゲート電極15を被覆するゲート絶縁層37と、ゲート絶縁層37上においてゲート電極15と端部が重畳し、第2酸化物半導体層40と導電層41が積層された一対の第1配線層38及び第2配線層39と、少なくともゲート電極15と重畳しゲート絶縁層37及び該第1配線層38及び該第2配線層39における導電層41の側面部及び上面部の一部と第2酸化物半導体層40の側面部と接する第1酸化物半導体層36とを有する非線形素子30aを用いて保護回路を構成する。

ゲート絶縁層37上において物性の異なる酸化物半導体層同士の接合を形成することで、ショットキー接合に比べて安定動作をさせることが可能となり、接合リークが低減し、非線形素子30aの特性を向上させることができる。

(もっと読む)

1 - 20 / 72

[ Back to top ]