Fターム[5F033MM28]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 膜厚の異なる複数の配線を有するもの (89)

Fターム[5F033MM28]に分類される特許

1 - 20 / 89

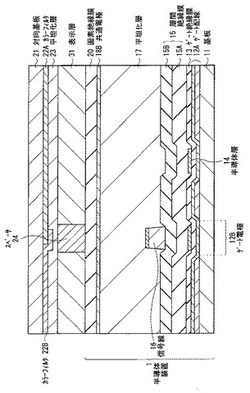

半導体装置およびその製造方法ならびに表示装置および電子機器

【課題】配線層の膜応力を低減し、製造歩留まりを向上することが可能な半導体装置およびその製造方法並びに表示装置および電子機器を提供する。

【解決手段】本技術の半導体装置は、一方向に延在する複数の第1配線層と、第1配線層の間に設けられた第1配線層よりも膜厚が薄いゲート電極と、第1配線層およびゲート電極上に形成された絶縁膜と、絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層と、半導体層上に設けられた層間膜と、層間膜上に形成されると共に、層間膜に設けられた貫通孔を介して半導体層と接続された第2配線層とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】エピ抵抗や抵抗チップを用いることなく、奇モードのループ発振を抑えること。

【解決手段】本発明は、金属層60を形成する工程と、複数のFETそれぞれのゲートフィンガー14を共通に接続するゲートバスライン26のパターンのうち一部分を除いたパターンを有するめっき層64と、一部分の領域を被覆する第2マスク層66と、をマスクにして金属層60をパターニングすることで、ゲートバスライン26を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】縦型トランジスタの特性にばらつきが生じることを抑制する。

【解決手段】半導体基板100には縦型MOSトランジスタ20が形成されている。半導体基板100の表面上には、第1層間絶縁膜300及び第1ソース配線312が形成されている。第1ソース配線312は、第1層間絶縁膜300上に形成されており、平面視で縦型MOSトランジスタ20と重なっている。第1層間絶縁膜300にはコンタクト302が埋め込まれている。コンタクト302は、縦型MOSトランジスタ20のn型ソース層140と第1ソース配線312とを接続している。そして第1ソース配線312には、複数の開口316が形成されている。

(もっと読む)

半導体装置

【課題】占有面積の小さな直線状の電気ヒューズを有する半導体装置を提供する。

【解決手段】複数の突出部10fは、電気ヒューズ部10aの中央位置からずれた位置、より具体的には、ビア10dに近くかつビア10eから遠い位置に設けられている。また、複数の突出部20fは、電気ヒューズ部20aの中央位置からずれた位置、より具体的には、ビア20dから遠くかつビア20eに近い位置に設けられている。つまり、突出部10fおよび突出部20fは、ジグザグ状に配置されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線層中の配線をゲート電極として使用し、かつ拡散防止膜と同一層にゲート絶縁膜を有している半導体素子を有する半導体装置において、拡散防止膜の機能を損なうことなく、半導体素子のオン抵抗を低くする。

【解決手段】第1配線層150を構成する絶縁層の表層には、第1配線154及びゲート電極210が埋め込まれている。第1配線層150と第2配線層170の間には、拡散防止膜160が形成されている。ゲート絶縁膜230は、拡散防止膜160のうちゲート電極210と重なる領域及びその周囲の上面に凹部を形成し、この部分を薄くすることにより、形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】配線抵抗を低減することのできる半導体装置を提供する。

【解決手段】一の実施の形態に係る半導体装置は、半導体基板と、半導体基板上にそれぞれ設けられた第1の領域及び第2の領域とを備える。第1の領域は、半導体基板上の第1配線層に形成され、所定の第1の幅を有する第1の金属配線と、第1配線層の上層の第2配線層に形成され第1の幅を有する第2の金属配線と、第1の金属配線と第2の金属配線とを接続し、第1の幅以下の第2の幅を有する第1のコンタクトとを有する。第2の領域は、第1配線層から第2配線層へと亘る膜厚を有し、所定の第3の幅を有する第3の金属配線を有する。

(もっと読む)

半導体装置

【課題】半導体装置において、高電圧の配線層とその下方を横切るように配置された抵抗層との間の絶縁膜の耐圧を確保し、この配線層と抵抗層との間で破壊が起きるのを抑制することを目的とする。

【解決手段】第1半導体領域10に接続され第2半導体領域11上を通過するように第3配線層22が配置されている。第3配線層22と第2半導体領域11との間に配置される絶縁膜14内には、一端が第3配線層22に接続されると共に、他端が第1半導体領域11よりも電位の低い制御端子12に接続され、且つ第3配線層22とSOI層2との間において第3配線層22を少なくとも1回以上横切る構成で抵抗層25が配置されている。この抵抗層25は、第3配線層22を横切る部位の上面が他の部位よりも下方位置となるように段差状に形成されている。

(もっと読む)

メッキ金属膜基板とその製造方法、及び半導体装置

【課題】一度の成膜で、所望の平面パターンと膜厚分布を有するメッキ金属膜を成膜することが可能なメッキ金属膜基板とその製造方法を提供する。

【解決手段】メッキ金属膜基板1は、基板上に少なくとも1層の給電金属膜20と少なくとも1層のメッキ金属膜30とを順次有し、少なくとも1層の給電金属膜20は、少なくとも1層のメッキ金属膜30の下地が相対的に高抵抗な高抵抗部20Hと、メッキ金属膜30の下地が相対的に低抵抗な低抵抗部20Lとを有するものである。

(もっと読む)

半導体装置及びその製造方法

【課題】モリセル領域内と周辺回路領域内およびそれらとの間に実施的に段差がない状態でメタル積層配線を形成し、段差部でメタル積層配線が断線する問題を回避する。センスアンプを構成するNMOSトランジスタとPMOSトランジスタのアンバランス動作を解消して動作遅延を軽減する。

【解決手段】半導体装置は、半導体基板上にメモリセル領域と周辺回路領域とを有し、メモリセル領域と周辺回路領域に跨って延在し、メモリセル領域ではビット線を構成し、周辺回路領域では周辺回路用配線の一部とゲート電極の一部を構成するメタル積層配線を有する。メモリセル領域に配置されるメタル積層配線の底面の半導体基板上面からの高さが、周辺回路領域に配置されるメタル積層配線の底面の半導体基板上面からの高さと実質的に同じである。

(もっと読む)

ディスプレイ装置及びその製造方法

【課題】構造及び製造工程を簡素化しながら、開口率を向上させた、ディスプレイ装置及びその製造方法を提供する。

【解決手段】本発明の実施形態に係るディスプレイ装置101は、基板111、前記基板111上に形成された前記第1透明導電膜1301及び前記第1透明導電膜1301上に形成された第1金属膜1302を含む多重膜構造と前記第1透明導電膜1301で形成された単一膜構造とを含むゲート配線、前記ゲート配線の一部の領域上に形成された半導体層153、そして前記半導体層上に形成された第2透明導電膜1701及び前記第2透明導電膜1701上に形成された第2金属膜1702を含む多重膜構造と前記第2透明導電膜1701で形成された単一膜構造とを含むデータ配線を含む。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】動作マージンを確保した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセル及び前記複数のメモリセルを選択する複数の選択配線を有するセルアレイを複数積層してなるセルアレイブロックと、第1高さから第2高さまで積層方向に延び、前記セルアレイブロックの選択配線のうちの所定の第1配線が側面に接続された柱状の第1ビアと、前記第1高さから第2高さまで積層方向に延び、前記セルアレイブロックの選択配線のうち前記第1配線よりも上層の所定の第2配線が側面に接続された柱状の第2ビアとを備え、前記第2配線は、前記第1配線よりも積層方向に厚く、且つ、前記第1配線よりも抵抗率が高いことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】 メモリセルアレイ領域と周辺回路領域との配線溝の深さを最適化する。

【解決手段】 本発明の一態様の半導体装置の製造方法によれば、レジストパターンをマスクとして芯材膜を加工する工程と、前記芯材膜上に被加工膜とエッチング選択比がある側壁膜を形成する工程と、前記側壁膜を異方性エッチング工程により加工する工程と、前記芯材膜を前記側壁膜と選択的に除去する工程と、第1領域の前記側壁膜上および前記被加工膜上に絶縁膜を第1の膜厚を有するように形成し、第2領域の前記被加工膜上に前記絶縁膜を第2の膜厚を有するように形成する工程と、を備えている。さらに、前記第2領域においてフォトリソグラフィ工程によりレジストパターンを形成する工程と、前記第1領域における前記側壁膜と前記第2領域における前記レジストパターンとをマスクとして前記絶縁膜および前記被加工膜を加工し、前記被加工膜に配線溝を形成する工程と、を備えている。

(もっと読む)

配線構造及び配線構造の形成方法

【課題】配線の洗浄液への溶解を低減する配線構造の形成方法を提供する。

【解決手段】絶縁層13に犠牲配線溝21及び主配線溝31を形成し、犠牲配線溝21及び主配線溝31内にバリア層16を形成し、バリア層16が形成された犠牲配線溝21及び主配線溝31内に導電層17を埋め込んだ後に、絶縁層13上の導電層17の部分を研磨する工程と、犠牲配線溝21及び主配線溝31内の露出したバリア層16及び導電層17の表面を洗浄する工程と、を備え、研磨する工程の後における絶縁層13の平面視において、犠牲配線溝21内のバリア層16の部分の面積と導電層17の部分の面積との比S1が、主配線溝31内のバリア層16の部分の面積と導電層17の部分の面積との比S2よりも大きくなる。

(もっと読む)

配線形成方法

【課題】配線層で、配線密度の高い領域では隣接する配線間のショートを防ぎ、配線密度の低い領域では所望の平坦度が得られるとともに所望の配線抵抗が得られるように配線高さを制御できる配線形成方法を提供する。

【解決手段】まず、基板上に第1の絶縁膜111と、第1の絶縁膜111に比してCMP研磨レートの小さい所定の厚さの第2の絶縁膜112を順に積層させて層間絶縁膜11を形成し、ついで、層間絶縁膜11の第1の領域に第1の配線密度となり、第2の領域に第1の配線密度よりも低い第2の配線密度となるように、第2の絶縁膜112を貫通し、底部が第1の絶縁膜111に至る配線形成用溝21を形成した後、配線形成用溝21を形成した層間絶縁膜11上に導電性材料膜14を形成し、そして、CMP法によって、少なくとも第1の領域で第1の絶縁膜111が露出、後退するように層間絶縁膜11と導電性材料膜14を研磨する。

(もっと読む)

半導体装置およびその製造方法ならびに半導体ウエハ

【課題】ダイシングブレードの寿命を延ばすことができるとともに、半導体装置のエッジ部へのダメージを低減できる半導体装置を提供する。

【解決手段】機能素子領域2においては、第3層間絶縁膜27表面とパッシベーション膜33との間には、下配線25に接続される上配線29およびキャップメタル層32が形成されている。下配線25はCu以外の配線材料からなり、上配線29はCuからなる。このキャップメタル層32におけるパッシベーション膜33のパッド開口34から露出した部分が第1パッド6である。一方、スクライブ領域3においては、第3層間絶縁膜27表面とパッシベーション膜33との間には、下配線25に接続されるキャップメタル層32が形成されている。このキャップメタル層32におけるパッシベーション膜33のパッド開口44から露出した部分が第2パッド10である。

(もっと読む)

半導体装置及びその製造方法

【課題】製造コストの増加および歩留まりを低下させることなく、配線抵抗を下げることのできる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板100上の絶縁膜104上にマスク材料膜106を形成した後、第1のトレンチ形成用開口と第2のトレンチ形成用開口とを有するマスクパターン109をマスク材料膜106に形成する工程と、マスク材料膜106上に、第1のトレンチ形成用開口を露出する第3のトレンチ形成用開口112を有し、且つ、第2のトレンチ形成用開口部を覆うレジストパターン113を形成する工程と、レジストパターン113及びマスクパターン109を用いて、絶縁膜104内に第1のトレンチ115を形成する工程と、レジストパターン113を除去した後、マスクパターン109を用いて、絶縁膜104内に第2のトレンチを形成する工程とを備えている。

(もっと読む)

半導体集積回路

【課題】少なくともロジック回路ブロックを含む半導体集積回路において、半導体集積回路の電源用パッドとロジック回路ブロックの電源ラインとを接続する電源配線、及び/又は、半導体集積回路のグランド用パッドとロジック回路ブロックのグランドラインとを接続するグランド配線の抵抗値を下げる。

【解決手段】この半導体集積回路は、半導体基板と、半導体基板上にそれぞれの層間絶縁膜を介して形成され、半導体基板に形成された複数のトランジスタに接続されて複数のトランジスタと共に少なくともロジック回路ブロックを構成する複数の配線層と、複数の配線層が形成された半導体基板上に層間絶縁膜を介して形成され、複数の配線層における最大膜厚の5倍〜20倍の膜厚を有する最上層の配線層とを具備する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通電極およびこれと一体的に形成された裏面電極を有する半導体装置において、貫通電極の膜厚と裏面電極の膜厚とを独立に制御することにより、貫通電極の剥離の問題と裏面配線の剥離の問題を同時に解消することができる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板10と、半導体基板の上方に形成された少なくとも1層からなる配線層13と、半導体基板の裏面から配線に達する貫通電極30と、半導体基板の裏面に設けられて貫通電極に接続された裏面配線40と、裏面配線に接続された外部端子50と、を含む半導体装置であり、裏面配線は、少なくとも外部端子との接続部を含む部分の膜厚が、貫通電極の膜厚よりも厚く形成されている。

(もっと読む)

半導体装置

【課題】ESD放電経路におけるメタル配線の電流密度の許容値を高くとることが可能であり、また、配線抵抗を小さくすることが可能である半導体装置を提供する。

【解決手段】信号パッド(101)と、電源線(103)と、接地線(104)と、一端が信号パッド(101)と接続されたインダクタ(111)と、インダクタ(111)の他端と電源線(103)または接地線(104)との間に設けられた終端抵抗(112)と、インダクタ(111)の中間の第1位置(Aa)に接続された第1ESD保護素子(ESD_G)と、インダクタ(111)の中間の第1位置(Aa)とは異なる第2位置(Ab)に接続された第2ESD保護素子(ESD_V)とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】ヒューズのカットばらつきを防ぐとともに腐食(酸化等も含む)を良好に防ぐ。

【解決手段】半導体装置100は、基板102と、基板102上に形成されたヒューズ配線116と、少なくともヒューズ配線116の側壁を保護するように形成された耐湿性絶縁膜120と、を含む。耐湿性絶縁膜120は、ヒューズ配線116の上面には形成されていないか、またはヒューズ配線116の上面における積層方向の膜厚d1がヒューズ配線116の側壁における積層方向に垂直な方向の膜厚d2よりも薄くなるように形成されている。

(もっと読む)

1 - 20 / 89

[ Back to top ]