Fターム[5F033MM29]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 線幅の異なる複数の配線を有するもの (161)

Fターム[5F033MM29]に分類される特許

1 - 20 / 161

半導体装置の製造方法

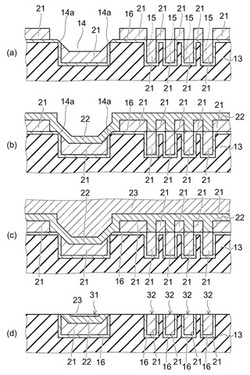

【課題】高い歩留まりを実現できる半導体装置の製造方法を提供する。

【解決手段】実施形態によれば、半導体装置の製造方法は、基板11上の絶縁層13に形成された第1の凹部14および第1の凹部14よりも幅が狭い第2の凹部15に、基板11を銅が流動可能なリフロー温度に加熱した状態で、第1の銅膜21を形成する工程を備えている。また、前記半導体装置の製造方法は、第1の銅膜21上に、不純物濃度が第1の銅膜21よりも高い第2の銅膜22を、第1の銅膜21の形成時よりも流動性が小さい状態で形成する工程を備えている。

(もっと読む)

半導体装置の製造方法

【課題】エピ抵抗や抵抗チップを用いることなく、奇モードのループ発振を抑えること。

【解決手段】本発明は、金属層60を形成する工程と、複数のFETそれぞれのゲートフィンガー14を共通に接続するゲートバスライン26のパターンのうち一部分を除いたパターンを有するめっき層64と、一部分の領域を被覆する第2マスク層66と、をマスクにして金属層60をパターニングすることで、ゲートバスライン26を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

半導体装置の製造方法

【課題】配線幅が異なる第1及び第2の配線を有する配線パターンの上に形成された絶縁層を、十分に平坦化すること。

【解決手段】基板上に、第1の配線及び第1の配線よりも配線幅が小さい第2の配線を有する配線パターンを形成する配線形成工程S10と、配線パターンの上から、第1の絶縁層及び第2の絶縁層をこの順に形成する絶縁層形成工程S20と、第2の絶縁層の上に、配線パターンの反転パターンを有するレジストパターンを形成するレジスト形成工程S30と、第2の絶縁層の方が第1の絶縁層よりもエッチングされやすい条件で等方性エッチングするエッチング工程S40と、レジストパターンを除去するレジスト除去工程S50と、を有する半導体装置の製造方法。

(もっと読む)

半導体集積回路、半導体集積回路の設計方法、および半導体集積回路の設計装置

【課題】配線層に形成される信号配線をなるべく迂回させずに配線できるように電源スタックビアが配置された半導体集積回路を提供すること。

【解決手段】半導体集積回路は、第1の方向に延伸された第1,第2の下層電源配線11A,11Bと、第2の方向に延伸された第1,第2の上層電源配線12A,12Bと、上層,下層電源配線を接続させる第1,第2接続部3A,3Bと、を備え、第1,第2接続部は、第1,第2の接続用配線26A,26Bと、第1,第2の位置変換用配線27A,27Bと、第1,第2の上側ビア28A,28Bと、を有して構成され、第1,第2の接続用配線は、第2の方向に沿った同一ライン上に配置され、第1,第2の位置変換用配線は、第1,第2の接続用配線を第2の方向に沿って延長した領域内に形成され、第1,第2の上側ビアは、第1の方向に沿った同一ライン上となる位置に配置される。

(もっと読む)

半導体装置

【課題】占有面積の小さな直線状の電気ヒューズを有する半導体装置を提供する。

【解決手段】複数の突出部10fは、電気ヒューズ部10aの中央位置からずれた位置、より具体的には、ビア10dに近くかつビア10eから遠い位置に設けられている。また、複数の突出部20fは、電気ヒューズ部20aの中央位置からずれた位置、より具体的には、ビア20dから遠くかつビア20eに近い位置に設けられている。つまり、突出部10fおよび突出部20fは、ジグザグ状に配置されている。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の製造後におけるチャージ蓄積用素子からのチャージの放電を防止してデバイス機能素子のチャージダメージを低減する半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板上に形成されたデバイス機能素子と、半導体基板上に形成されたチャージ蓄積用素子と、半導体基板上に形成され、デバイス機能素子とチャージ蓄積用素子との間に接続され、電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子とを有する。

(もっと読む)

半導体装置、表示装置および電子機器

【課題】特性の劣化を抑えつつ省スペース化を図ることが可能な半導体装置等を提供する。

【解決手段】半導体装置は、基板上の第1の方向に沿って延在し、互いに離隔配置された主配線部および分岐配線部を有する1または複数の第1の配線と、基板上の第1の方向とは異なる第2の方向に沿って延在する幹配線部と、主配線部と分岐配線部との間隙領域内で第1の方向に沿って延在する複数の枝配線部とを有する1または複数の第2の配線と、複数の枝配線部が個別にゲート電極として機能すると共に、主配線部内および分岐配線部内に形成されたソース領域と、複数の枝配線部間に形成されたドレイン領域とを有し、各々が第2の方向に沿って複数個に分割形成されてなる1または複数のトランジスタと、第2の方向に沿って延在し、トランジスタのドレイン領域と電気的に接続された1または複数の第3の配線とを備えている。

(もっと読む)

無電解薄膜析出法により平坦化銅相互接続層を形成する方法および装置

【課題】基板に定形された形態部の内部に、表面が平坦化された導電性材料を形成する方法を提供する。

【解決手段】平坦化表面を形成する方法であって、狭小形態部と幅広形態部が形成された基板上に、第1のプロセスでは電気めっき法により狭小形態部および幅広形態部の少なくとも一部を充填し、第1の層を形成し、第2のプロセスでは無電解めっき法により幅広形態部のに対応する第1の層中の孔および第1の層上に第2の層を充填形成し、表面が平坦な上層部110を形成する。

(もっと読む)

半導体集積回路のトランジスタ素子

【課題】簡易な構成であり且つトランジスタ毎にしきい値電圧が異なる半導体集積回路のトランジスタ素子の提供。

【解決手段】ソース領域16A,16D、ドレイン領域16B,16Cおよびチャネル領域を備えた支持基板(Si基板2)上に、ゲート電極10とゲート電極10を覆う中間膜18とを備える第1および第2のトランジスタ構造を、少なくとも有し、前記第1のトランジスタ構造におけるゲート電極10とチャネル領域とが重なる領域には、中間膜18上に、第1のトランジスタ構造のしきい値電圧に変動を及ぼす範囲でゲート電極10とチャネル領域とが重なる領域の大部分を覆うよう支持基板(Si基板2)に応力を印加する応力膜22を有し、前記第2のトランジスタ構造におけるゲート電極10とチャネル領域とが重なる領域には、中間膜18上に、支持基板(Si基板2)に応力を印加する応力膜22を有さない半導体集積回路のトランジスタ素子。

(もっと読む)

半導体装置及びその製造方法

【課題】配線抵抗を低減することのできる半導体装置を提供する。

【解決手段】一の実施の形態に係る半導体装置は、半導体基板と、半導体基板上にそれぞれ設けられた第1の領域及び第2の領域とを備える。第1の領域は、半導体基板上の第1配線層に形成され、所定の第1の幅を有する第1の金属配線と、第1配線層の上層の第2配線層に形成され第1の幅を有する第2の金属配線と、第1の金属配線と第2の金属配線とを接続し、第1の幅以下の第2の幅を有する第1のコンタクトとを有する。第2の領域は、第1配線層から第2配線層へと亘る膜厚を有し、所定の第3の幅を有する第3の金属配線を有する。

(もっと読む)

偏在率算出方法、半導体装置の製造方法及びプログラム

【課題】レイアウトデータからCu残が発生しやすい品種やレイヤであるか否かを判定することのできる偏在率算出方法を提供する。

【解決手段】CPUは、検証レイヤにおいて所定サイズの検証エリア毎にパターン密度を算出するステップS13と、算出されたパターン密度を複数の密度範囲に分別し、各々の密度範囲に属するパターン密度の分布を示す複数の密度マップMAP0〜MAP7を生成するステップS14とを実行する。また、CPUは、各密度マップMAP0〜MAP7に所定量のプラスシフトを加えるステップS15と、パターン密度の密度差が第1基準値以上となる組み合わせの密度マップMAP0〜MAP7を重ね合わせ、両密度マップで重複した領域を抽出するステップS16とを実行する。CPUは、その抽出した領域の総面積を算出するステップS17と、算出した総面積と第2基準値とを比較するステップS18とを実行する。

(もっと読む)

配線の形成方法

【課題】配線が微細化された場合でも、所望の高さの配線を得ることができる配線の形成方法を提供する。

【解決手段】実施形態によれば、まず、絶縁膜11上に形成した犠牲導体膜12に配線形成用溝12a,12bを形成する。ついで、配線形成用溝12a,12bが形成された犠牲導体膜12上の全面にCuを堆積し配線形成用溝12a,12b内に流動するようにリフローさせて、配線形成用溝12a,12b内にCu膜14bを形成する。その後、犠牲導体膜12とCu膜14bを通電層としてめっき法によって配線形成用溝12a,12b内のCu膜14b上にCu膜14cを積み増す。ついで、Cu膜14b,14cからなるCu配線14をCMP処理して平坦化した後、犠牲導体膜12を除去する。その後、Cu配線14が形成された絶縁膜11上に絶縁膜15を形成する。

(もっと読む)

半導体集積回路

【課題】製造コストを増大させずに、半導体集積回路の電源配線、接地配線の電圧降下を減少させる。

【解決手段】半導体チップ1上の第1の方向に延びる電源配線12Aが配置され、半導体チップ1上の第2の方向に延びると共に、第2の方向から第1の方向に屈曲し、電源配線12Aの一部と重畳する屈曲部24Aを有する電源引き出し配線22Aが配置されている。また、第1の方向に延びる接地配線12Bが配置され、第2の方向に延びると共に、第2の方向から、第1の方向とは逆方向の第3の方向に屈曲し、接地配線12Bの一部と重畳する屈曲部24Bを有する接地引き出し配線22Bが配置されている。電源引き出し配線22Aと接地引き出し配線22Bを覆う第1の層間絶縁膜13の中には、電源配線12Aと屈曲部24Aを接続する電源配線ビアコンタクト14Aと、接地配線12Bと屈曲部24Bを接続する接地配線ビアコンタクト14Bが配置されている。

(もっと読む)

半導体装置

【課題】半導体チップ内の銅配線が一部消失することを防ぐ。

【解決手段】上層プラグ一本当たりの下層の配線の面積が10000μm2以上になるような大面積の多層配線を有する半導体装置において、前記多層配線が半導体基板1Sの主面においてn型拡散層NSを介してpウエルPWに接続される構造を形成せず、前記多層配線をp型拡散層PSを介してpウエルPWに接続する構造、前記多層配線をp型拡散層PSを介してn型拡散層NSに接続する構造、前記多層配線をn型拡散層NSを介してnウエルに接続する構造、または半導体基板1S上に形成されたMISFETのゲート電極に接続する構造を形成する。

(もっと読む)

半導体装置

【課題】チップ面積を拡大することなく信頼性の高い配線レイアウトを実現する。

【解決手段】信号線S1〜S3と電源線VDD1,VSS1がY方向に延在する下層配線層と、信号線S4〜S6と電源線VDD2,VSS2がX方向に延在する上層配線層と、対応する信号線が重なり合うオーバーラップ領域OL1に設けられたビア導体VE1と、対応する電源線が重なり合うオーバーラップ領域OL2,OL3に設けられたビア導体VE2,VE3とを備える。領域OL1のX方向における幅は、領域OL2,OL3のX方向における幅よりも広く、これにより、領域OL1には複数のビア導体VE1a,VE1bが設けられる。また、電源線VDD1,VSS1は、領域OL1との干渉を避けるようY方向に分断されている。複数の下層配線は、一つのビアを含むミニマムピッチで2つのビアを配置している。

(もっと読む)

半導体装置

【課題】2つのトランジスタを混載した半導体装置において、ダミー配線を介して配線間で短絡が発生するのを防止し、信頼性の高い混載デバイスを実現可能にする。

【解決手段】本発明の半導体装置は、微細CMOS4Aと、微細CMOS4Aに接続される微細配線15とを有する微細CMOS領域と、微細CMOS4Aよりも耐圧が高い高耐圧デバイス4Bと、高耐圧デバイス4Bに接続され、平面視において微細配線15よりも配線幅が広いドレイン配線115及びソース配線116と、を有する高耐圧デバイス領域と、を具備し、高耐圧デバイス領域には、電気的に孤立したダミー配線14が少なくともドレイン配線115及びソース配線116に隣接して配置されない。

(もっと読む)

半導体装置の製造方法

【課題】 メモリセルアレイ領域と周辺回路領域との配線溝の深さを最適化する。

【解決手段】 本発明の一態様の半導体装置の製造方法によれば、レジストパターンをマスクとして芯材膜を加工する工程と、前記芯材膜上に被加工膜とエッチング選択比がある側壁膜を形成する工程と、前記側壁膜を異方性エッチング工程により加工する工程と、前記芯材膜を前記側壁膜と選択的に除去する工程と、第1領域の前記側壁膜上および前記被加工膜上に絶縁膜を第1の膜厚を有するように形成し、第2領域の前記被加工膜上に前記絶縁膜を第2の膜厚を有するように形成する工程と、を備えている。さらに、前記第2領域においてフォトリソグラフィ工程によりレジストパターンを形成する工程と、前記第1領域における前記側壁膜と前記第2領域における前記レジストパターンとをマスクとして前記絶縁膜および前記被加工膜を加工し、前記被加工膜に配線溝を形成する工程と、を備えている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の配線間容量を低減する。

【解決手段】半導体装置の製造方法は、基板の上方に絶縁膜を形成する工程と、絶縁膜を貫通する第1の溝及び絶縁膜の内部で終端する第2の溝を絶縁膜に形成する工程と、絶縁膜の内部で終端する配線溝を絶縁膜に形成する工程と、第1の溝の表面及び配線溝の表面に第1の金属膜を形成するともに、第2の溝の上方を覆うように第1の金属膜を形成する工程と、第1の溝及び配線溝に第2の金属膜を埋め込む工程と、を備える。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子及びその製造方法を提供する。

【解決手段】基板上で第1方向に延在するラインパターンと、ラインパターンの端部から、第1方向と異なる方向に延在する分岐ラインパターンとをそれぞれ含む第1導電ライン;第2導電ライン;第3導電ラインとを含む半導体素子であり、中間に位置する導電ラインの分岐ラインパターンは、他の導電ラインの分岐ラインパターン間に位置し、長さもさらに短い。これにより、コンタクト・パッドが、導電ラインの分岐ラインパターンと一体に形成されうる。

(もっと読む)

半導体装置の製造方法

【課題】チップ面積の削減が可能な側壁加工プロセスを用いた半導体装置の製造方法を提供すること。

【解決手段】実施形態の半導体装置の製造方法は、基板301上に被加工膜302を形成し、被加工膜の上に芯材膜304を形成し、芯材膜の一部であって被加工膜の加工時まで残存させる残存部分とそれ以外の芯材膜である除去予定部分との間が所定距離の間隙となるように芯材膜をパターニングする。パターニングの後に芯材膜の側面に側壁305を形成して除去予定部分および残存部分の側面を側壁で覆うとともに残存部分と除去予定部分との間の所定距離の間隙を側壁で閉塞する。さらに、側面が側壁で覆われた残存部分の上面を覆うようにレジスト306を形成し、レジストの形成後にウェットエッチングを行うことにより除去予定部分を除去し、ウェットエッチングの後にレジストを除去する。レジストを除去した後に側壁および残存部分をマスクとして被加工膜を加工する。

(もっと読む)

1 - 20 / 161

[ Back to top ]