Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

2,141 - 2,160 / 2,805

半導体装置およびその製造方法

【課題】電気的にフローティングした配線に蓄積する電荷を、半導体基板に逃がすこと。

【解決手段】第1主面12aを備えた半導体基板12と、第1主面側に設けられたMOSFET14と、MOSFETのゲート電極26およびゲート電極に電気的に接続された配線を含む第1配線構造体36と、第1主面および第1主面に電気的に接続された配線を含む第2配線構造体38と、第1および第2構造体のどちらとも接触し、かつ、第1および第2配線構造体間を接続している、酸化イットリウムからなる非導電性膜16とを備える

(もっと読む)

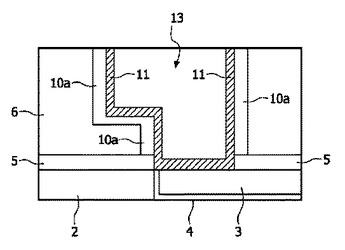

半導体装置用構造およびその製造方法

半導体装置用のダマシン配線(1)の製造方法を示す。非導電性バリヤ層(10)が、多孔質低誘電率材料によって定義されるパッセージ(7)の壁の上と、パッセージ(7)の一端を閉じる銅領域(3)の表面の上とに形成される。非導電性バリヤ層(10)は、誘電性材料の貫通細孔からなるその下層部(10a)が非導電性を残している間に、その上層部(10b)を導電層に変換するためにプラズマ処理される。ついで、パッセージ(7)は、今度は導電性になっているバリヤ(10)の上層部(10b)を介して第1銅領域(3)と電気配線を形成する第2銅領域(13)で満たされる。当業者にとって明らかなように、本文献において開示、請求される本発明のすべての実施形態は、本発明の範囲を超えることなしに結合されても良い。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 WPPを使用した半導体装置において、最上層配線間のショート不良を防止することにより、信頼性を向上させることのできる技術を提供する。

【解決手段】 最上層配線43aと再配線50との間に緩衝層47を設ける。このとき、例えば、最上層配線43aは銅膜より形成され、緩衝層47は、アルミニウム膜より形成される。さらに再配線50は、銅膜51とニッケル膜52の積層膜から形成される。このように構成された半導体装置において、低温と高温との間の温度サイクルで3重点Xに応力が集中する。この3重点Xに集中した応力は、緩衝層47の存在によって緩和され、3重点Xの直下にある界面Yへの応力の伝達を抑制することができる。このため、界面Yでの応力による剥離を防止できる。

(もっと読む)

ヒューズ素子及びその切断方法

【課題】ヒューズ回路を大きくすることなく層間絶縁膜のクラックを防止できるとともに、ヒューズ切断前後において大きな抵抗変化を得ることができるヒューズ素子及びその切断方法を提供する。

【解決手段】シリコン層を含む配線部14と、配線部14の一端側に接続されたコンタクト部20bと、配線部14の他端側に接続されたコンタクト部20aとを有するヒューズ素子において、コンタクト部20bからコンタクト部20aへ配線部14を介して電流を流し、コンタクト部20aの金属材料をシリコン層中にマイグレーションさせることにより、配線部14とコンタク部20aとの間の接続抵抗を変化させる。

(もっと読む)

半導体デバイス用TaN膜とそれを用いた半導体デバイス

【課題】膜厚の面内均一性を高めた半導体デバイス用TaN膜を提供する。

【解決手段】半導体デバイス用TaN膜はCuまたはCu合金からなる配線膜に対するバリア層として用いられるTaN膜であって、膜厚の面内均一性が5%以下とされている。

(もっと読む)

半導体装置およびその製造方法

【課題】キャパシタ電極とコンタクトプラグとの導通性を向上できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、絶縁膜15−1と、前記絶縁膜中に設けられ、金属を主成分とするコンタクトプラグ16と、前記絶縁膜上に設けられ、前記金属より酸素親和性が高く、酸化物を主成分とする第1接着膜33−1と、前記コンタクトプラグ上および前記第1接着膜上に設けられ、酸素の拡散を防止するように働く第1キャパシタ電極21と、前記第1キャパシタ電極上に設けられたキャパシタ絶縁膜22と、前記キャパシタ絶縁膜上に設けられた第2キャパシタ電極23とを具備する。

(もっと読む)

半導体装置の製造方法

【課題】ダマシン構造を有する半導体装置において、レジストポイゾニング現象の発生要因となる、レジストの化学反応を阻害する反応阻害物質を効率良く除去する。

【解決手段】基板上に形成された第1の絶縁膜10に、配線11を形成する工程(a)と、第1の絶縁膜10及び配線11の上に、第2の絶縁膜12を形成する工程(b)と、第2の絶縁膜12の上に、第2の絶縁膜12を露出させる開口部を有する第3の絶縁膜(14,15)を形成する工程(c)と、第3の絶縁膜(14,15)の上に、レジストパターンを形成する工程(d)とを備え、工程(b)よりも後であって且つ工程(c)よりも前に、工程(b)の際に発生する、レジストパターンを構成するレジストの化学反応を阻害する物質を除去する工程(X)を更に備える。

(もっと読む)

半導体装置の製造方法

【課題】 導電部材中のCu以外の元素の含有量を低減させ、比抵抗を低下させることができる半導体装置の製造方法を提供する。

【解決手段】 (a)半導体基板上に、凹部が設けられた絶縁膜を形成する。(b)開口の内面及び絶縁膜の上面を、Cu以外に第1の金属元素を含むCu合金からなる補助膜で覆う。(c)凹部内に充填されるように、補助膜上に、Cuを主成分とする導電部材を堆積させる。(d)P化合物、Si化合物、またはB化合物を含有する雰囲気下で熱処理を行う。

(もっと読む)

半導体素子の金属配線およびその製造方法

【課題】銅配線のベリア金属層の物質としてCVD TiSiNを用いて65nm以下の半導体素子にも適用できるようにした半導体素子の金属配線およびその製造方法を提供する。

【解決手段】本発明に係る半導体素子の金属配線は、半導体素子が形成された半導体基板と、前記半導体素子に相応する部分にコンタクトホールを有し、前記半導体基板に形成される絶縁膜と、前記コンタクトホール内に形成されるTiSiNベリア金属層と、前記TiSiNベリア金属層上に形成される銅配線とを含んで構成される。

(もっと読む)

成膜方法及び電子デバイスの製造方法

【課題】 結晶構造が体心立方格子構造の金属、または、ルテニウムを確実且つ容易にエッチバック可能とした成膜方法及び電子デバイスの製造方法を提供することを目的とする。

【解決手段】成膜後に少なくともその一部がエッチングされる金属膜の成膜方法であって、

結晶構造が体心立方格子構造の金属またはルテニウムを含有するガスと水素ガスとを含むソースガスと、窒素ガスと、を基体上に流し前記ソースガスを分解することにより前記金属または前記ルテニウムからなる金属膜を前記基体の上に形成することを特徴とする成膜方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】 スタックト構造を有するコンタクトプラグの複数段連結されたコンタクトプラグのうちの下方のものについて、酸化防止を図る。

【解決手段】 半導体装置の製造方法は、半導体基板1上に第1の絶縁膜5を形成する工程(a)と、第1の絶縁膜5中に、バリアメタル膜7及びタングステン膜8からなる第1のプラグ9を形成する工程(b)と、第1のプラグ9Aの上方に、下部電極14、容量絶縁膜15及び上部電極16からなる容量素子17を形成する工程(c)と、第1の絶縁膜5及び第1のプラグ9上に、第2の絶縁膜11を形成する工程(d)と、第2の絶縁膜11中に、第1のプラグ9Bと接続してスタックト構造を構成する第2のプラグ21を形成する工程(e)と、工程(c)の後に、容量素子17に対して酸素雰囲気中で熱処理する工程(f)と、工程(b)と工程(d)との間に、半導体基板に対して熱処理をする工程(g)とを備える。

(もっと読む)

半導体装置およびその欠陥検査方法

【課題】ショート欠陥を容易に速やかに検出することができ、ショート欠陥の原因となるマイクロスクラッチ対策にも有用な半導体装置およびその欠陥検査方法を提供する。

【解決手段】半導体基板11上の最上層の絶縁膜12の上に、前記半導体基板11あるいは下層配線に対して電気的に接続された第1の線分導体パターン14と電気的に接続されない第2の線分導体パターン13とが交互に並列に配列されてなる、荷電ビームによる画像上で検査されるテストパターン16を有した半導体装置とする。

(もっと読む)

半導体装置の製造方法

【課題】 密着性を高める機能を併せ持つバリア層が形成されるまでの期間に、配線部材の十分な密着性を確保し、配線部材の剥離を防止することが可能な半導体装置の製造方法を提供する。

【解決手段】 (a1)半導体基板の上に形成された絶縁膜に凹部を形成する。(a2)凹部の内面、及び絶縁膜の上面を覆うように、CVD法により、Mnからなる第1の膜を形成する。(a3)第1の膜の上に、Cuを主成分とする導電材料を堆積させるとともに、凹部内に該導電材料を充填する。(a4)半導体基板をアニールする。

(もっと読む)

半導体装置

【課題】空孔率の高い層間絶縁膜を用いた信頼性の高い多層配線構造を有する半導体装置を提供する。

【解決手段】空孔率が50%以上の層間膜を有する下層配線層と、空孔率の低い上層配線層を備える多層配線構造において、配線層間を接続するビアを配線層を介して基板表面に垂直方向に連続して形成したスタックドビア70とチップ外周部に設けた外周リング80により、空孔率が低く厚い層間膜を有する上層配線層を支える構造とする。

(もっと読む)

半導体装置の製造方法

【課題】接続孔または配線溝の側壁に露出される層間絶縁膜に吸着している水分を確実に脱ガスさせて除去するとともに、接続孔の底部への下層配線の隆起を防ぐことが可能な半導体装置の製造方法を提供する

【解決手段】表面側に下層配線9が設けられたSiO2層4上に、保護膜10と第1絶縁膜11および第2絶縁膜12とを順次形成する。次に、下層配線9上の第1絶縁膜11および第2絶縁膜12に、保護膜10に達する接続孔16と接続孔16の上部に連通する配線溝17を形成する。次いで、接続孔16の底部に保護膜10を残存させた状態で、第1の熱処理を行う。続いて、保護膜10を除去し、接続孔16の底部に下層配線9を露出させる。次に、接続孔16の底部に下層配線9を露出させた状態で、第1の熱処理よりも低い温度で第2の熱処理を行う。その後、接続孔16および配線溝17にヴィアおよび配線を形成することを特徴とする半導体装置の製造方法である。

(もっと読む)

強誘電体メモリ及びその製造方法

【課題】 本発明の目的は、微細化及び高密度化に対応し、かつ製造プロセスの容易化を図ることのできる、強誘電体メモリ及びその製造方法を提供することにある。

【解決手段】 強誘電体メモリは、基板10と、基板10の上方に形成された少なくとも1層よりなる層間絶縁層30,34と、層間絶縁層30,34の上方に形成された複数の強誘電体キャパシタC11,C22と、複数の強誘電体キャパシタC11,C22を被覆する被覆層70と、複数の強誘電体キャパシタC11,C22の間に設けられた第1の開口部72と、第1の開口部72と連通するとともに被覆層70及び層間絶縁層34に形成された第2の開口部74と、第1及び第2の開口部72,74内に一体的に設けられた導電層82と、を含む。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】シード層から導電部表面に拡散して酸化物を形成する金属の酸化物層で形成することで、配線信頼性の向上、微細化によるRC遅延の問題を解決することを可能とする。

【解決手段】基板11上の絶縁膜(層間絶縁膜21)に形成された凹部22の内面にバリア層25を介してシード層26を形成する工程と、シード層26を介して凹部22を導電部(銅)27で埋め込む工程と、層間絶縁膜21上に形成された銅およびシード層26を除去して、凹部22内に銅を主材料とする導電部27を形成する工程とを備えた半導体装置の製造方法であって、シード層26は導電部27表面に拡散して酸化物を形成する金属を含む銅材料で形成され、凹部22内に銅を主材料とする導電部27を形成した後に熱処理を行って導電部27表面に酸化物を形成する金属を含む酸化物層31を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ロジック領域におけるトランジスタの上を応力を有する膜で覆って能力を向上させると共に、SRAM領域において、各トランジスタの能力のバランスを保持し、リーク電流の発生を抑制する事ができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置では、N型ロジック領域NLにおけるトランジスタが引っ張り応力を有する膜50により覆われ、P型ロジック領域PLにおけるトランジスタが圧縮応力を有する膜55により覆われている。そして、P型SRAM領域PSにおけるトランジスタおよびN型SRAM領域NSにおけるトランジスタは、引っ張り応力を有する膜50aおよび圧縮応力を有する膜55aからなる積層膜により覆われている。

(もっと読む)

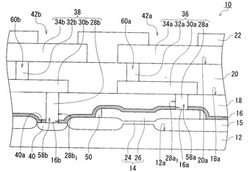

ピッチ増倍コンタクトを形成する方法

集積回路内で使用するための導電性および/または半導電性のフィーチャを形成する方法を開示する。種々のパターン転写ステップおよびエッチング・ステップをピッチ縮小技術と組み合わせて用いて、高密度実装フィーチャを生成することができる。フィーチャは、1つの方向に縮小ピッチを有し、別の方向に広いピッチを有することができる。従来のフォトリソグラフィ・ステップをピッチ縮小技術と組み合わせて用いて、たとえばビット線コンタクト(732)など、細長いピッチ縮小フィーチャを形成することができる。いくつかの実施形態では、コンタクト(732)は、マスキング材料の複数の層が上にある絶縁層(334)を設けることによって形成することができる。次に、一連の選択的に画定可能な線(124)をマスキング材料中に形成することができ、そこでその線がパターンを有する。次に、スペーサ材料(170)を使用して線に対してピッチ縮小を実施すると、スペーサ軸に沿って延びるピッチ縮小マスキング線(175)を生成することができる。したがって、ピッチ縮小空所によって各ピッチ縮小マスキング線(175)を分離することができる。次に、マスキング・フィーチャの一部分と交差するフォトレジストの第2のパターン(たとえば第2のマスク480のパターン)を付けることができる。第2のパターンは、ピッチ縮小マスキング線(175)、および隣接するピッチ縮小空所をフォトレジストで覆われないままにする窓(482)を有することができる。窓(482)は、ピッチ縮小マスキング線の長軸に対して平行ではない長軸を有することができる。次に、一部にはピッチ縮小空所によって画定された第3のパターンを介して絶縁層(334)をエッチングすると、絶縁層(334)中にコンタクトビア(584)を生成することができる。コンタクトビア(584)を導電材料で充填して電気コンタクト(732)を生成することができる。 (もっと読む)

半導体装置の製造方法、半導体装置およびウエハ

【課題】 ウエハの薄型化に際して生じる問題を回避し、積層ウエハ間の電気的接続のための工程を短縮できる方法を提供する。

【解決手段】 基板1SAにその主面から所望の深さまで延びる深い分離溝5aを形成した後、深い分離溝5a内に絶縁膜5bを埋め込み貫通分離部5を形成する。続いて、基板1SAの主面にMOS・FET6を形成した後、基板1SAの主面上に層間絶縁膜8aを堆積する。その後、貫通分離部5で囲まれた領域内に、層間絶縁膜8aの上面から基板1SAの厚さの途中深さまで延びる深い導通溝9aを形成する。続いて、深い導通溝9a内に導体膜9bを埋め込み貫通配線部9を形成する。その後、基板1SAの裏面を、貫通分離部5および貫通配線部9が露出しない程度まで研削および研磨した後、貫通分離部5および貫通配線部9の下部の一部が露出する程度までウエットエッチング処理する。

(もっと読む)

2,141 - 2,160 / 2,805

[ Back to top ]