Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

221 - 240 / 2,805

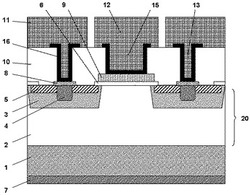

半導体装置とその製造方法

【課題】配線加工時のエッチングレートの極端な上昇を抑え、プロセスを安定化させる。

【解決手段】炭化珪素基板1上に形成された炭化珪素層20の上に、ソース電極8、ゲート電極9、層間絶縁膜10、層間絶縁膜10上に形成されたソース電極上部配線11およびゲート電極上部配線12とが形成され、ソース電極上部配線11とゲート電極上部配線12の下には、これらの上部配線を構成する金属が炭化珪素層20に拡散することを抑制するためのバリアメタル16が形成されている。層間絶縁膜10には、炭化珪素層20上に形成されたソース電極8およびゲート電極9に到達するようにコンタクトホール13、15が形成されており、バリアメタル16はコンタクトホール内の電極と上部配線との界面、層間絶縁膜10の側壁と上部配線との界面、および側壁の上端部近傍と上部配線との界面にのみ形成されている。

(もっと読む)

半導体装置

【課題】半導体装置の小型化、特に、狭ピッチ化に対する技術を提供する。

【解決手段】半導体チップ1C上に設けられたパッド2と、プローブ領域10Aおよび接続領域10Bのパッド2上に開口部11を有し、半導体チップ1C上に設けられたパッシベーション膜3と、接続領域10Bのパッド2上に開口部12を有し、パッド2上およびパッシベーション膜3上に設けられたパッシベーション膜5と、パッド2と電気的に接続され、接続領域10B上およびパッシベーション膜5上に設けられた再配線7とを備える。接続領域10Bより半導体チップ1Cの外周部側に設けられたプローブ領域10Aのパッド2にプローブ痕100が存在し、接続領域10Bから半導体チップ1Cの中央部側に延びて再配線7が存在している。

(もっと読む)

半導体装置及びその製造方法、並びにSOI基板及びその製造方法

【課題】コンタクトホールの形成領域が素子分離領域と重複しても、素子特性の劣化を抑制できるSOI基板とこのSOI基板を用いた半導体装置とを提供する。

【解決手段】半導体装置1は、半導体基材11と埋め込み絶縁膜12と半導体層16とを有するSOI基板と、このSOI基板上に形成された半導体素子構造とを備える。埋め込み絶縁膜12は、半導体基材11から半導体層16を電気的に絶縁分離する機能を有し、窒化膜14を有する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を製造する。また、スループットを向上させ、製造コストを低減する。

【解決手段】開口部OA1および絶縁膜(21、23)上に銅のCuシード層27を形成する工程と、Cuシード層上に、フォトレジスト膜を形成する工程と、Cuシード層上に、メッキ成長により銅膜31aを形成する工程と、銅膜上に、Ni膜31bを形成する工程と、により、再配線31を形成する。この後、再配線31上の開口部(OA2、パッド領域)にAu膜33bを形成した後、フォトレジスト膜を除去し、Ni膜31bに不動態化処理を施す。この後、再配線31の形成領域以外のCuシード層27をエッチングする。かかる工程によれば、Ni膜31bの表面に不動態化膜35が形成され、上記エッチングによるNi膜31bの膜減りを低減できる。また、膜減りを考慮したNi膜の厚膜化による基板の歪みによる不具合を低減できる。

(もっと読む)

半導体装置の製造方法

【課題】配線中に残留した不純物金属の濃度が少ない半導体装置の製造方法を提供する。

【解決手段】半導体基板上に絶縁膜を形成し、絶縁膜に凹部を形成し、凹部の形成された絶縁膜の表面に所定の金属元素を含む前駆体膜を形成し、前駆体膜上に配線形成膜を堆積させ、酸化雰囲気下で熱処理を施すことにより、前駆体膜と絶縁膜を反応させ、その境界面に所定の金属元素と絶縁膜の構成元素を含む化合物を主成分とする自己形成バリア膜を形成し、未反応の所定の金属元素を配線形成膜内に拡散移動させて配線形成膜表面で雰囲気中の酸素と反応させ、未反応金属酸化膜として析出させ、未反応金属酸化膜を除去し、未反応金属酸化膜を除去する工程の後、配線形成膜上に、配線形成膜と同一の材料を堆積させて、配線形成膜を積み増した後、凹部外の絶縁膜が露出するまで配線形成膜を平坦化して配線構造を形成する。

(もっと読む)

半導体装置

【課題】隣接するビット線同士の短絡が抑制されており、かつ層間絶縁膜が平坦に研磨された半導体装置を提供する。

【解決手段】磁気抵抗素子MRDが複数配置されたメモリセル領域と、平面視においてメモリセル領域の周囲に配置された周辺回路領域とを備える。磁気抵抗素子MRDは、磁化固定層と磁化自由層とトンネル絶縁層とを含んでいる。磁気抵抗素子MRDの上方には、主表面に沿った方向に向けて延びる複数の第1の配線BLを有している。上記周辺回路領域には、第1の配線BLと同一レイヤにより構成される第2の配線BL2と平面視において重なるように、磁化自由層と同一材質の層、トンネル絶縁層と同一材質の層および磁化固定層と同一材質の層が積層された積層構造DMMが配置されている。積層構造DMMは、周辺回路領域にて平面視において隣接する1対の第2の配線BL2の両方と重ならない。

(もっと読む)

固体撮像素子、固体撮像素子の製造方法、及び電子機器

【課題】センサ基板と回路基板とを電極間で張り合わせてなる構成において電極間の接合面積を確保することが可能な3次元構造の固体撮像素子を提供する。

【解決手段】光電変換部21が配列形成されたセンサ基板2と、光電変換部21を駆動する回路が形成されセンサ基板2に対して積層された回路基板7と、センサ基板2における回路基板7側の界面に引き出されたセンサ側電極45と、回路基板7におけるセンサ基板2側の界面に引き出された回路側電極65とを備え、センサ側電極45と回路側電極65とは、凹型電極に凸型電極を嵌め合わせた状態で接合されていることを特徴とする固体撮像素子1である。

(もっと読む)

半導体装置及びその製造方法

【課題】多結晶シリコンプラグと上層の導体プラグとの界面に十分な膜厚の金属シリサイド層を形成してコンタクト抵抗の低減を図る。

【解決手段】多結晶シリコンプラグを形成した後、多結晶シリコンプラグの表面からゲルマニウムイオン注入を実施してゲルマニウム含有多結晶シリコン16Gとし、その後、シリサイド化可能な金属膜を成膜して金属シリサイド層19を形成し、金属シリサイド19上に導体膜(バリア膜20、W膜21)を形成する。

(もっと読む)

半導体装置の製造方法

【課題】デュアルダマシン法による銅配線接続において、コンタクト抵抗の上昇を抑制する半導体装置の製造方法を提供する。

【解決手段】第1の配線25上に積層された第1の拡散防止膜27及び層間絶縁膜のうち、第1の層間絶縁膜28をエッチングすることで第1のホールを形成する。第1の拡散防止膜がエッチングされにくい条件で、第1のホールの下方に位置する第1の層間絶縁膜をエッチングして第2のホールを形成する。第2のホールを埋め込むように、第1の層間絶縁膜よりもエッチング速度の速い第2の層間絶縁膜を形成する。第1の層間絶縁膜の上面が露出するまで第2の層間絶縁膜をエッチングすることで、第2のホールと一体とされた配線形成用溝を形成する。第2のホール内に残存する第2の層間絶縁膜を選択的に除去し、第2のホールの下方に位置する第1の拡散防止膜を選択的に除去する。

(もっと読む)

半導体装置の製造方法及び製造装置

【課題】半導体装置のエッチングを精度良く行い、再生率を低減させる

【解決手段】基板にトランジスタを形成し、トランジスタを覆うように第1層間絶縁膜22を形成する。さらに、第1層間絶縁膜22の上方に形成したレジスト膜27を用いて第1層間絶縁膜22をエッチングし、トランジスタのソース/ドレイン領域に到達するコンタクトホール31を形成する。この際、レジスト膜27の開口部27Aの半径rと、開口部27Aが設計位置からずれている位置ずれ量ΔXとを測定し、コンタクトホール31に必要な半径Rxと、コンタクトホール31を形成可能な限界距離Sとから、r+ΔX−S<ES<r−Rxを満たす半径差ESを決定し、半径差ESからエッチング条件を決定する。

(もっと読む)

Cu−Mn合金スパッタリングターゲット及び半導体配線

【課題】半導体用銅合金配線自体に自己拡散抑制機能を有せしめ、活性なCuの拡散による配線周囲の汚染を効果的に防止することができ、またエレクトロマイグレーション(EM)耐性、耐食性等を向上させ、バリア層が任意に形成可能かつ容易であり、さらに半導体用銅合金配線の成膜工程の簡素化が可能である半導体用銅合金配線及び同配線を形成するためのスパッタリングターゲット並びに半導体用銅合金配線の形成方法を提供する。

【解決手段】Mn0.05〜20wt%を含有し、Be,B,Mg,Al,Si,Ca,Ba,La,Ceの総計が500wtppm以下、残部がCu及び不可避的不純物であることを特徴とするCu−Mn合金スパッタリングターゲット。

(もっと読む)

半導体装置の製造方法

【課題】タングステン膜を使用した部分の抵抗を低減した半導体装置を提供する。

【解決手段】半導体装置の製造方法では、基板内に設けた開口部内、又は基板上にタングステン膜を形成する。タングステン膜の形成後、エッチバック又はエッチングを行う前にタングステン膜に対してアニール処理を行う。これにより、タングステン膜の結晶状態を変化させる。

(もっと読む)

半導体装置およびその製造方法

【課題】 表面側から特性試験が行える縦型の半導体装置を提供する。

【解決手段】 半導体装置10では、半導体基板11は第1の面と、第1の面に対向する第2の面を有している。半導体素子12は半導体基板11のダイシングライン14、15で囲まれた矩形状格子に形成されるとともに、第1の面に形成された第1電極26と、第2の面に形成された第2電極28とを有している。電流は第1電極26と第2電極28の間に流れる。貫通電極16は半導体基板11のダイシングライン14、15で囲まれていない領域に形成されるとともに、一端が第1の面上に延在し、他端が第2電極28と電気的に接続されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】絶縁層及び金属層の密着性を向上させる。

【解決手段】半導体基板1には、一方の平面1aから他方の平面1bに貫通するビアホール2が形成され、ビアホール2の底部2aとなる電極パッド層4が他方の平面1bに設けられている。この半導体基板1の一方の平面1a及びビアホール2の側壁部2bには、絶縁層6が形成されている。また、金属層7が、半導体基板1の一方の平面1a及びビアホール2の側壁部2bに絶縁層6を介して形成され、ビアホール2の底部2aに直接形成されている。ビアホール2の側壁部2bには、ビアホール2の底部2aにおける開口径がビアホール2の開口端部2cにおける開口径よりも大きくなるように傾斜面2dが形成されている。傾斜面2dには、複数の凹凸2eが形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】実効誘電率が低く、かつ信頼性の高いバリア絶縁膜を有する半導体装置を提供することができる。

【解決手段】半導体装置100は、層間絶縁膜10と、層間絶縁膜10中に設けられた配線20と、層間絶縁膜10上および配線20上に設けられたSiN膜30と、を備え、FTIRによって測定したSiN膜30のSi−N結合のピーク位置が845cm−1以上860cm−1以下である。これにより、配線金属の拡散を防ぐためのバリア絶縁膜である窒化シリコン膜において、リーク電流を抑制することができる

(もっと読む)

半導体装置及びその製造方法

【課題】配線の絶縁膜内へのCu溶出を抑制すると共に、配線間におけるショートの発生を抑止し、信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】MCMの半導体装置において、ベアチップ1,2間を接続する配線4aをCu材料13を用いてダマシン法で形成する際に、上面が有機絶縁膜11の表面から上方に突出し、上面の配線幅方向の中央部位が端部位よりも厚い配線4aを形成し、配線4aのCu材料13上のみにメタルキャップ膜5を形成する。

(もっと読む)

半導体装置

【課題】基板の大型化に対応し得る金属配線を作製する。

【解決手段】絶縁表面上に少なくとも一層の導電膜12,13を形成し、前記導電膜12,13上にレジストパターンを形成し、前記レジストパターンを有する導電膜にエッチングを行い、バイアス電力密度、ICP電力密度、下部電極の温度、圧力、エッチングガスの総流量、エッチングガスにおける酸素または塩素の割合に応じてテーパー角αが制御された金属配線を形成する。このようにして形成された金属配線は、幅や長さのばらつきが低減されており、基板10の大型化にも十分対応し得る。

(もっと読む)

半導体装置およびその製造方法

【課題】工程数を削減して生産性を向上できる構造の半導体装置およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体層1にトレンチ20を形成する工程と、トレンチ2の内壁およびトレンチ2外の表面を覆うように半導体層1上に絶縁膜3を形成する工程と、トレンチ2を埋め尽くし、トレンチ2外の絶縁膜3上に堆積されるように導電性のポリシリコン膜4を形成する工程と、トレンチ2内、およびトレンチ2外の絶縁膜3上の所定領域にポリシリコン膜4が残るように、当該ポリシリコン膜4を選択的に除去するポリシリコンエッチング工程とを含む。

(もっと読む)

半導体装置及びその製造方法並びにそれを用いた積層型半導体装置

【課題】貫通電極に起因する応力を抑制し、半導体装置の動作を安定化し、半導体装置の信頼性を向上する。

【解決手段】半導体装置は、表面側に活性領域を有する半導体基板1と、半導体基板1の表面から裏面までを貫通するように形成され、導電材からなる貫通電極24と、貫通電極24に囲まれるように形成され、導電材とは異なる応力緩衝部25とを備えている。応力緩衝部25は、貫通電極24の内部であって半導体基板1の表面が横切る位置に形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】DRAMセルとロジックを混載したLSIデバイスにおけるアスペクト比の大きいコンタクト構造において、素子分離絶縁膜および不純物拡散層のオーバエッチングを抑制して、接合リークを抑制することを課題とする。

【解決手段】周辺MOSトランジスタを覆う第1エッチングストッパ層121と、DRAMメモリセルのキャパシタ部上層に第2エッチングストッパ層122が形成され、周辺MOSトランジスタの不純物拡散層113は、第1、第2エッチングストッパ層121、122を貫通する電極層131により、上記キャパシタ部上層に形成された金属配線層と接続され、不純物拡散層113の少なくとも一つは素子分離絶縁膜102の境界上に電極層131を接続し、素子分離絶縁膜102上に形成された電極層131の底部の不純物拡散層113表面からの深さ寸法は、不純物拡散層113の接合深さ寸法もより短く形成されたものである。

(もっと読む)

221 - 240 / 2,805

[ Back to top ]