Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

2,641 - 2,660 / 2,805

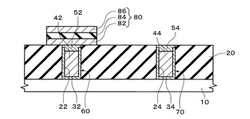

強誘電体メモリ及びその製造方法

【課題】 製造プロセスの簡略化及び信頼性の向上を図ることにある。

【解決手段】 強誘電体メモリの製造方法は、(a)基体10の上方に形成された絶縁層20に、第1及び第2のコンタクトホール22,24を形成すること、(b)第1及び第2のコンタクトホール22,24のそれぞれの内部に、絶縁層20の上面よりも低い上面を有するプラグ42,44を形成すること、(c)第1及び第2のコンタクトホール22,24のそれぞれのプラグ42,44の上方に、バリア層52,54を形成すること、(d)下部電極82、強誘電体層84及び上部電極86を順に積層して積層体81を形成すること、(e)積層体81をエッチングすることによって、第1のコンタクトホール22のプラグ42の上方を含む領域に、強誘電体キャパシタ80を形成すること、を含む。バリア層52,54は、下部電極82よりもエッチングされにくい性質を有する。

(もっと読む)

半導体装置とその製造方法

【課題】 プラズマ処理によりシリコン表面に形成される、SiCを含む変質層を、シリコン表面の侵食を最小限に抑止しながら除去する。

【解決手段】 前記変質層を、酸素ラジカルに、前記半導体表面のSi原子に結合してSi原子と酸素原子との間の二重結合の形成を阻害するような元素の活性種を添加して改質し、形成された改質層をウェットエッチングにより除去する。

(もっと読む)

強誘電体メモリ及びその製造方法

【課題】 信頼性の向上を図ることにある。

【解決手段】 強誘電体メモリの製造方法は、(a)基体10の上方に形成された絶縁層20に、第1及び第2のコンタクトホール22,24を形成すること、(b)第1及び第2のコンタクトホール22,24のそれぞれの内部に、絶縁層20の上面よりも低い上面を有するプラグ42,44を形成すること、(c)第1及び第2のコンタクトホール22,24のそれぞれのプラグ42,44の上方を含む領域に、バリア層51を形成すること、(d)下部電極82、強誘電体層84及び上部電極86を順に積層して積層体81を形成すること、(e)積層体81をエッチングすることによって、第1のコンタクトホール22のプラグ42の上方を含む領域に、強誘電体キャパシタ80を形成すること、(f)第2のコンタクトホール24のプラグ44の上方を含む領域に、被覆層90を形成すること、(g)酸素雰囲気下においてアニール処理を行うこと、を含む。

(もっと読む)

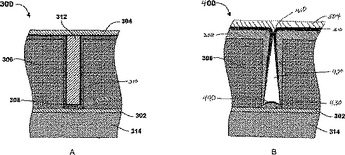

集積回路相互接続構造のGCIB処理

集積回路内の金属(304)の相互接続の製造工程および品質を改善するために、ガスクラスタ・イオンビーム(GCIB)(128)によって集積回路相互接続構造の溝やビア内の材料を取り除いたり再配分したりする方法が開示されている。この工程では、構造の入口の領域での不要な「ネックイン」を広げ、構造の頚部または底部等のより厚い領域から側壁に、バリア金属(308)を再堆積させたり、スパッタリングによって構造の底部の余分で不要な材料の一部を取り除く。GCIB処理は、バリア金属堆積後で銅シード層(310)/銅(312)電気メッキ前に適用することも、銅シード層(310)の形成後で電気メッキ前に適用することもできる。この方法は、既知の相互接続堆積技術の有用性を、次世代以降の集積回路まで拡張できる。  (もっと読む)

(もっと読む)

レジスト除去方法及び半導体装置の製造方法

【課題】 低誘電率絶縁膜の比誘電率の増加を防止すると共にレジスト残渣を生じさせないレジスト除去を可能にする。

【解決手段】 ビアホール用開口3を有するレジストマスク4をエッチングマスクにして、第1キャップ層2c、第1低誘電率膜2bを順次に反応性イオンエッチング(RIE)でドライエッチングしビアホール5を形成する。そして、レジストマスク4の除去では、はじめに、上記RIEでレジストマスク4表面部に形成された変質層4aに対して、ホットプレートにより空気雰囲気、300℃温度、3分程度の熱処理を施すことで、変質層4aを少なくともその一部が酸素と反応した改質層4bに変換させる。その後に、この改質層4bおよびレジストマスク4に水素ラジカルを照射して残渣のないレジスト除去を行う。

(もっと読む)

半導体装置の設計方法及び半導体装置

【課題】低誘電率層間膜材料を用いた多層配線におけるスタックビアの熱応力歪みによる信頼性低下を予め防ぐことを可能とするスタックビアレイアウト設計方法および半導体装置を提供する。

【解決手段】スタックビア設計レイアウト結果から温度変化による歪みによって故障発生可能性の高い危険スタックビア部を特定のスタックビア構造をもとに抽出し、その危険スタックビア部の温度変化歪み量を算出して所定の臨界歪み量を超える臨界スタックビアを抽出し、そのビアを含む領域に回路機能に変化を与えないように新規ビア構造を追加配置することで臨界スタックビアの歪み量を低減させて、信頼性の高いスタックビアのレイアウト結果を得る。また前記の特定のスタックビア構造を有しない半導体装置を構成する。

(もっと読む)

半導体装置の製造方法

【目的】 点欠陥の集合によるボイドがCu配線内に形成しないようにすることを目的とする。

【構成】 基体上に絶縁膜を形成する絶縁膜形成工程(S102〜S110)と、前記絶縁膜に開口部を形成する開口部形成工程(S112)と、前記絶縁膜表面と前記開口部とにシード膜を形成するシード膜形成工程(S116)と、前記シード膜を電極として第1の電流密度となる電流を流し、前記開口部に導電性材料をめっき法により堆積させる第1のめっき工程(S118)と、前記第1のめっき工程後、前記第1の電流密度より小さい第2の電流密度となる電流を流し、前記絶縁膜表面上に前記導電性材料をめっき法により堆積させる第2のめっき工程(S120)と、前記第2のめっき工程後、前記導電性材料が堆積した基体をアニール処理するアニール工程(S124)と、を備えたことを特徴とする。

(もっと読む)

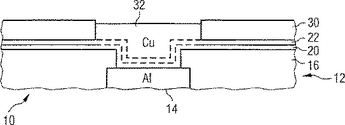

金属、特に銅を電着する方法、この方法の使用、および集積回路構造

とりわけ、絶縁層(16)内において相互接続(14)へのコンタクトホール(18)が生成される方法が示される。バリア層(20)が次いで提供される。その後、フォトレジスト層(30)が提供され、照射され、かつ、現像される。次いで、ガルバニック法を用いて、銅コンタクト(32)がコンタクトホール(18)において生成される。バリア層(20)またはさらなる境界電極層(22)のどちらか一方が、ガルバニック処理において境界電極としての役目をする。重大な金属汚染は、製造中、この方法によって抑制される。  (もっと読む)

(もっと読む)

半導体装置

【課題】 半導体装置中のクラックの伝播を抑制し、他の領域に影響を与えないようにする。

【解決手段】 シリコン基板101上に設けられたSiCN膜105およびSiOC膜107を貫通する凹部の側面を覆う界面補強膜115を設ける。界面補強膜115はSiOC膜113と連続一体に形成され、エアギャップ117を有する。

(もっと読む)

多重積層膜構造の金属窒化膜の蒸着方法

【課題】素子回路線幅の超微細化、パターン縦横比の増加、および蒸着温度の低下にもかかわらず、膜特性、段差塗布性、大気/湿気露出に対する膜質変化に対する安定性の全てを満足させる多重積層膜構造の金属窒化膜の蒸着方法を提供する。

【解決手段】基板上に第1蒸着速度で第1下部金属窒化膜を形成し、前記第1下部金属窒化膜上に第2蒸着速度で第2下部金属窒化膜を形成し、前記2段階によって形成された下部TiN膜上に、窒素(N)含有量の多い上部金属窒化膜を第3蒸着速度で形成することからなり、前記n番目膜の蒸着速度は、第2蒸着速度≧第1蒸着速度≧第3蒸着速度である。本発明によれば、基板上にTiN積層膜を形成することで、大気/湿気露出に対する安定性を向上させることができ、クラスタシステムの同一反応チャンバーまたは相違した反応チャンバーで容易に基板上にTiN積層膜を形成することができる。

(もっと読む)

ビアに相互接続を形成する方法及び該相互接続を含むマイクロエレクトロニック・ワークピース

【課題】マイクロエレクトロニック・ワークピースの異なる高さで導電要素を電気的に連結するために深いビアに相互接続を形成する技術を提供する。

【解決手段】ブラインドビア又は他の種類の孔に相互接続を形成する方法及びそのような相互接続を有するマイクロエレクトロニック・ワークピース。ブラインドビアは、ワークピース全体を薄くすることなくワークピースの背面(14)の一部分から材料の一塊を最初に除去することによって形成することができる。この一括除去処理は、例えば、ワークピース内の中間深さまで延びるが導電要素の接触面(26)までは延びない第1の開口部(30)を形成することができる。第1の開口部を形成した後に、第1の開口部の中間深さから導電要素の接触面まで第2の開口部(40)が形成される。第2の開口部は、第1の開口部の第1の幅よりも狭い第2の幅を有する。本方法は、更に、ブラインドビアを導電材料で充填する段階、及び続いて空洞(30)が除去されるまでワークピースを外部側面から薄くする段階を含む。

(もっと読む)

半導体チップの製造方法、半導体チップ、半導体装置の製造法および半導体装置

【課題】貫通電極の形成に伴う半導体基板の金属汚染を抑制することができる半導体チップの製造方法を提供する。

【解決手段】一方表面に機能素子3が形成されたウエハWの当該一方表面に、ウエハWの厚さよりも浅い所定の深さの表面側凹所9を形成する。続いて、表面側凹所9内に非金属材料を供給して、当該非金属材料からなるダミープラグ8を形成する。次に、ウエハWにおいて上記一方表面とは反対の面である裏面Wrを機械的に研削して、ウエハWを表面側凹所9の深さより小さな厚さに薄型化して、表面側凹所9をウエハWを貫通する貫通孔にする。その後、この貫通孔内のダミープラグ8を除去し、さらに、この貫通孔内に金属材料を供給して貫通電極を形成する。

(もっと読む)

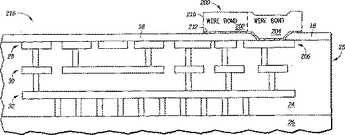

ボンディングパッドを有する半導体装置及びその形成方法

ボンディングパッド(200)は第1ワイヤボンディング領域(202)と、第2ワイヤボンディング領域(204)と、を含む。一実施形態では、第1ワイヤボンディング領域(202)がパッシベーション(18)を覆って延びる。別の実施形態では、ボンディングパッドはプローブ領域、第1ワイヤボンディング領域、及び第2ワイヤボンディング領域を有する。一実施形態では、プローブ領域及びワイヤボンディング領域がパッシベーション(18)を覆って延びる。ボンディングパッドはどのような数のワイヤボンディング領域及びプローブ領域も有することができ、かつこれらの領域をどのような構成として有することもできる。ボンディングパッドが複数のワイヤボンディング領域を含むことができるので、マルチチップパッケージにおける場合のように単一のボンディングパッドへの複数のワイヤ接続を行なうことができる。ボンディングパッドがパッシベーションを覆って延びる形でパッドを設けることができるので、集積回路チップ面積を小さくすることもできる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】低電気抵抗化および高信頼性化可能なコンタクトを備え、高速伝送が可能で信頼性の高い半導体装置およびその製造方法を提供する。

【解決手段】 コンタクト20、23を、CVD法を用いて、シリサイド膜19、22、シリコン窒化膜15aおよび第1層間絶縁膜15bの内壁に接する表面に、表面からコンタクト内部方向への距離に応じて窒素含有量が減少する組成勾配を有する窒化タングステン部24を形成し、その内側にタングステンが充填されたタングステン部25を形成する。窒化タングステン部24とタングステン部25との界面の酸化や汚染を防止する。

(もっと読む)

反射防止コーティング及び積層配線ライン

【解決手段】 チタニウム−アルミニウム−窒素(「Ti−Al−N」)が半導体基板上に積層されて反射防止コーティングとしての役割を果たす。配線ラインの実施の形態に対して、アルミニウム導電層(54)及びアルミニウム−チタニウム下層(52)は、反射防止キャップ層の下に形成される。

【効果】 配線ライン製造プロセスに対して、Ti−Al−N層は、製造中の不要なフォトリソグラフ光(即ち、光子)の反射を防止するキャップ層(56)としての役割を有する。電界放射ディスプレイ装置(FED)(150)に対して、Ti−Al−N層は、ディスプレイスクリーン(118)のアノードに由来する光がトランジスタ接合部を通過して装置動作を妨害するのを防止する。Ti−Al下層は熱処理中にアルミニウム導電層に起きる収縮を低減する。

(もっと読む)

半導体装置及びその製造方法

【課題】 配線及びコンタクトを微細化しながら活性領域の増大を抑制して、配線と活性領域とのコンタクトを良好に保つ。

【解決手段】 半導体装置では、配線M1乃至M3がY方向に平行して設けられ、配線直下に活性領域SDGが設けられ、配線M2が第1のコンタクトC1及び第2のコンタクトC2を介して活性領域SDGと接続されている。第1のコンタクトC1は、配線M2よりも幅の広い活性領域SDG内に、第1のコンタクトと活性領域との余裕Zだけ内側に設けられ、開口部にコンタクトプラグ6が埋設されている。配線M2内に設けられた第2のコンタクトC2は、第1のコンタクトC1上に第1のコンタクトC1と接して設けられ、X方向の寸法X1が第1のコンタクトC1及び配線M2よりも第2のコンタクトと配線の余裕Wの2倍分だけ小さく、且つY方向の寸法Y1が第1のコンタクトC1よりも大きく、活性領域SDGの外側まで設けられている。

(もっと読む)

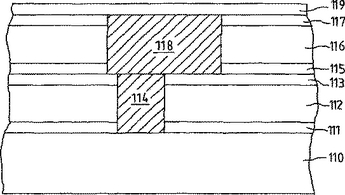

半導体装置の製造方法

【課題】 ヴィアホール、配線層の良好なカバレージを得ることにより、歩留りや信頼性の向上を図った半導体装置の製造方法を提供する。

【解決手段】 半導体基板上1に、所定パターンの第1の金属層3を形成する工程と、全面に、第1の絶縁膜4を形成する工程と、前記第1の絶縁膜4上に、所定パターンの第2の金属層5を形成し、この第2の金属層5上に第3の金属層6を形成する工程と、前記第3の金属層6上に、第2の絶縁膜7を形成する工程と、前記第2の絶縁膜7を平坦化する工程と、全面に、第3の絶縁膜9を形成する工程と、前記第3の絶縁膜9上に反射防止膜10を形成する工程と、前記反射防止膜10上にレジスト層を形成する工程と、前記レジスト層をパターニングする工程と、パターニングされたレジスト層11をマスクとしてエッチングを行い、所定位置に前記第2の金属層に到達する開口部12、13を形成する工程と、前記開口部12、13内を含む全面に、第4の金属層及び第5の金属膜を形成する工程とを備える。

(もっと読む)

磁気抵抗効果装置およびその製造方法

【課題】磁界を効率よく記憶素子に集束させることができ、配線間のショートが防止された磁気抵抗効果装置およびその製造方法を提供する。

【解決手段】互いに平行に配置される複数の第1配線11と、第1配線11の上方に離間して配置されるとともに、互いに平行に配置される複数の第2配線12と、第1配線11と第2配線12との間の一領域に、磁気抵抗型のTMR素子13とを備えた磁気抵抗効果装置であって、各第2配線12上を覆うとともに、隣接する第2配線12間に連続して設けられた絶縁性の高透磁率材料からなる第2磁性体層22bを備えたことを特徴とする磁気抵抗効果装置およびその製造方法である。

(もっと読む)

ハイブリッド誘電体を備えた高信頼低誘電率相互接続構造

【課題】ハイブリッド誘電体を有する拡張型バック・エンド・オブ・ライン(BEOL)相互接続構造を提供すること。

【解決手段】ビア・レベルでの層間誘電体(ILD)は、ライン・レベルでのILDとは異なることが好ましい。好ましい実施形態では、ビア・レベルのILDを低k SiCOH材料で形成し、ライン・レベルのILDを低kポリマー熱硬化性材料で形成する。  (もっと読む)

(もっと読む)

デュアル・ダマシン配線及びその形成方法

【課題】 デュアル・ダマシン配線の形成方法を改善し、デュアル・ダマシン配線効率を向上させる新たなデュアル・ダマシン配線構造体を提供すること。

【解決手段】 デュアル・ダマシン相互接続構造体及び該構造体を形成する方法であり、該構造体はデュアル・ダマシン配線を誘電体層に含み、該デュアル・ダマシン配線は該誘電体層の厚さと比べて小さい距離にわたって該誘電体層内に延び、デュアル・ダマシン・ビア・バーは該デュアル・ダマシン配線の底面と一体になっており、かつ、該底面から該誘電体層の底面に向かって延びる。

(もっと読む)

2,641 - 2,660 / 2,805

[ Back to top ]