Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

2,661 - 2,680 / 2,805

半導体装置の製造方法及び半導体装置

【目的】 配線抵抗を低減させながら歩留まりを向上させたバリアメタル膜を形成することを目的とする。

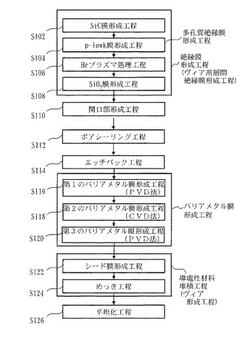

【構成】 基体上に絶縁膜を形成する絶縁膜形成工程(S102〜S108)と、前記絶縁膜に開口部を形成する開口部形成工程(S110)と、PVD法を用いて、前記絶縁膜上と開口部内とに第1のバリアメタル膜を形成する第1のバリアメタル膜形成工程(S116)と、その上に、CVD法を用いて第2のバリアメタル膜を形成する第2のバリアメタル膜形成工程(S118)と、その上に、PVD法を用いて第3のバリアメタル膜を形成する第3のバリアメタル膜形成工程S120)と、その上に、導電性材料を堆積させる堆積工程(S112,S124)と、を備え、前記絶縁膜上に形成された前記第1と第2と第3のバリアメタル膜の合計膜厚が、8nmより小さくなるように形成することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】 本発明は、特性にばらつきが生じることを抑制して歩留まりを向上させることができる半導体装置の製造方法を提供することを目的とする。

【解決手段】 半導体基板上に層間絶縁膜を形成するステップと、層間絶縁膜の所望の領域を除去し、当該除去した領域を埋め込むように、半導体基板及び層間絶縁膜上に導電性材料を堆積して膜を形成するステップと、層間絶縁膜と略同一の高さを有するように膜を平坦化することにより、導電性材料を埋め込んで第1の導電層を形成するステップと、埋め込まれた第1の導電層の上面に希釈コリン水溶液を用いた処理を行うステップとを備えることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 ボイドの移動経路となるバウンダリーが顕著に低減されるため、SIV不良の発生を効果的に抑制することができ、信頼性の高い半導体装置を提供する。

【解決手段】 相対的に広幅の第2銅配線110,126の上面において、銅のグレインが数10μm程度と非常に大きい。第2銅配線110,126の配線幅は0.3μm〜数10μm程度であるので、第2銅配線110,126の上面において配線幅方向のバウンダリーが顕著に低減され、第2銅配線110,126とビア113との接続部分にボイドが集中・合一して大きなボイドが形成されることを抑制することができ、SIVの発生が効果的に抑制される。相対的に狭幅の第1銅配線111,127の面方位はEM耐性を向上させるために主にCu(111)であり、相対的に広幅の第2銅配線110,126の面方位はSIV耐性を向上させるために主にCu(200)である。

(もっと読む)

半導体素子の金属配線形成方法

【課題】エッチング停止膜のアンダーカットなどのプロファイル不良を防止する半導体素子の金属配線形成方法を提供する。

【解決手段】半導体素子の金属配線形成方法は、まず、導電性パターンが埋め込まれている基板上に、エッチング阻止膜121,122及び絶縁膜131,132を順次に形成する。次いで、絶縁膜をパターニングしてエッチング阻止膜を露出させる開口部を形成する。次いで、開口部の内面に沿って第1拡散防止膜161を形成する。次いで、スパッタリング方式のエッチングを通じて、開口部の底面の第1拡散防止膜及びエッチング阻止膜を除去する。次いで、導電性パターンと電気的に連結される導電物質を、開口部に埋め込む。

(もっと読む)

溝配線または接続孔を有する半導体装置の製造方法

【課題】 電気的特性および信頼性に優れた溝配線または接続孔を有する半導体装置の製造方法を提供する。

【解決手段】 層間絶縁膜74上に所定の回路パターンを有するレジスト膜75bを形成し、レジスト膜75bをマスクとしてエッチング処理し、層間絶縁膜74にビア78aを形成する。このエッチング処理によって層間絶縁膜74に形成されたビア78aの側面部をシリル化処理し、ビア78aの側面部をエッチング処理によるダメージから回復させる。その後、ビア78aに金属を埋め込み、その表面を平坦化する。

(もっと読む)

信頼性の向上した銅被膜のための接続パッド構造およびその製造方法

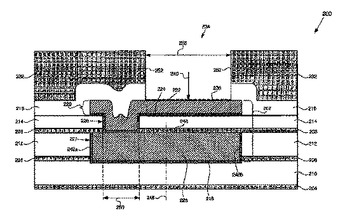

1つの例示的な実施例に従って、半導体ダイにおける構造は、相互接続金属層内に配置される金属パッド(226)を含み、金属パッド(226)は銅を含む。当該構造はさらに、金属パッド(226)の上に配置される層間誘電体層(214)を含む。当該構造はさらに、層間誘電体層(214)内に規定される端子ビア(228)を含み、端子ビア(228)は、金属パッド(226)の上に配置される。端子ビア(228)は、金属パッド(226)の1つの側面(242a、242b、242c、242d)のみに沿って延在する。当該構造はさらに、層間誘電体層(214)の上および端子ビア(228)内に配置される端子金属層(220)を含む。当該構造はさらに、端子金属層(220)の上に配置される誘電体ライナー(216)を含み、接続パッド開口部234は、誘電体ライナー(216)内に規定され、接続パッド開口部(234)は、端子金属層(220)の一部分(236)を露出させる。層間誘電体層(214)は、端子金属層(220)の露出部分(236)と金属パッド(226)との間に配置される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 従来では、半導体層表面に堆積された絶縁層にコンタクトホールを形成する際に、半導体層表面に耐エッチング膜としての絶縁膜を形成することで、製造工程が煩雑となり、また、余計な製造コストが掛かるという問題があった。

【解決手段】 本発明では、コレクタ領域の拡散領域4表面のシリコン酸化膜8、TEOS膜9、20をエッチングする工程と、ベース取り出し電極16表面のTEOS12、20膜をエッチングする工程とを別工程とする。そして、露出した拡散領域4表面及びベース取り出し電極16表面にコバルトシリサイド膜21を形成する。コバルトシリサイド膜21をコンタクトホール25、26、27を形成する際の、耐エッチング膜として用いることで、オーバーエッチングを防ぐことができる。

(もっと読む)

半導体装置の製造方法

【目的】 層間絶縁膜が剥離または破壊される事態が起こりにくい半導体装置の製造方法を提供することを目的とする。

【構成】 基体上に絶縁膜を形成する絶縁膜形成工程(S102〜S108)と、前記絶縁膜上に導電性材料を堆積させる堆積工程(S114〜S118)と、堆積した前記導電性材料を所定の深さまでウェットエッチングするウェットエッチング工程(S120)と、ウェットエッチングされた前記導電性材料を研磨する研磨工程(S122)と、を備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【目的】 ヴィア(ヴィアコンタクト)の加工形状を均一にすることを目的とする。

【構成】 第1の配線層と、前記第1の配線層の上方に形成された第2の配線層と、前記第1の配線層と前記第2の配線層との間のヴィア層に配置され、前記第2の配線層下面から前記第1の配線層上面まで導電性材料が堆積したヴィア20と、前記第1の配線層と前記第2の配線層との間のヴィア層に配置され、前記第2の配線層下面から前記ヴィア層の途中まで導電性材料が堆積した、前記ヴィア20より径の小さなヴィア22と、を備えたことを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 ドライエッチングにより半導体基板やポリシリコン層に生じるダメージ層を効果的に除去して、寄生抵抗や接合リークが低減された半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、半導体基板上に絶縁膜を形成する工程と、前記絶縁膜を、ドライ工程によりエッチングする工程と、前記エッチングにより前記半導体基板上に生じたダメージ層を、熱分解した原子状の水素により、所定の温度下で除去する工程とを含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】多層配線の狭ピッチ化に対応可能な半導体装置およびその製造方法を得る。

【解決手段】半導体基板上に複数の第1配線層を形成する工程と、第1配線層を覆うように第1層間絶縁膜層9を形成する工程と、第1層間絶縁膜層に、表面からその厚み方向に貫いて第1配線層に接続する複数の第1プラグ14を形成する工程と、第1層間絶縁層上であって、第1プラグのうち一部の第1プラグの直上部に第2配線層40を形成する工程と、第1層間絶縁膜層上に第2配線層を覆うように第2層間絶縁膜層19を形成する工程と、第2層間絶縁膜層に、表面からその厚み方向に貫いて第2配線層に接続する第2プラグ24’と、表面からその厚み方向に貫いて第1プラグに直接接続する第3プラグ24と、を同時に形成する工程と、第2層間絶縁膜層上であって、第2プラグおよび第3プラグの直上部に第3配線層50を形成する工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】 従来では、埋込拡散層が、他の熱処理工程で必要以上に這い上がり、所望の耐圧特性が得られないという問題があった。

【解決手段】 本発明では、N型の埋込拡散層2を形成した後、素子間分離等に用いる溝部8のコーナー部9を丸めるため、ドライエッチングを行う。更に、溝部8を、例えば、CVD法によるNSG膜10で埋設し、分離領域を構成するトレンチ12は、例えば、CVD法によるHTO膜13及び多結晶シリコン膜14で埋設する。この製造方法により、N型の埋込拡散層2の必要以上の這い上がりを抑制し、所望の耐圧特性が得られる半導体装置を実現できる。

(もっと読む)

半導体装置の製造方法

【課題】 ダマシン配線のトレンチあるいはビアホールの側壁部でのダメージ層の生成および多孔質のLow−k膜中でのボイドの発生を抑制する。

【解決手段】 下層配線1上に第1エッチングストッパー層2a、多孔質の第1低誘電率膜2bおよび第1キャップ層2cの積層した第1層間絶縁膜2を形成し、C4F8のような炭素含有量が多いフルオロカーボンガスを用いレジストマスク3を使用したドライエッチングによりビアホール4を形成する。次に、第1キャップ層2cをハードマスクにし、エッチングガスとしてCF4/Ar/N2混合ガスあるいはCHF3/Ar/N2混合ガスを用い、上記エッチングガスの圧力を0.1Pa〜6.0Pa範囲にして第1エッチングストッパー層2aをエッチング除去し、ビアホール4を下層配線1表面に達するように貫通させる。

(もっと読む)

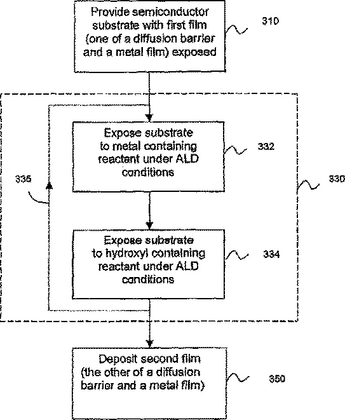

酸素架橋構造及び方法

拡散バリア膜と金属膜との間の接着性を改善するための方法が提唱される。拡散バリア膜及び金属膜の両方は、いずれかのシークエンスで、半導体基板上へ堆積される。拡散バリア膜又は金属膜のいずれか一方である第一膜(第一膜は、基板の表面領域の少なくとも一部で暴露される)を有する基板は、酸素含有リアクタントに暴露され、第一膜の露出部分に酸素含有基又は酸素原子の約1の単層の表面終端を生成する。次いで、第二膜(これは、拡散バリア膜及び金属膜のうち他方である)が基板上に堆積される。さらに、酸素架橋構造が提唱され、該構造は、拡散バリア膜及び該拡散バリア膜との界面を有する金属膜を含む(ここで、界面は、酸素原子の単層を含有する)。

【課題】

【解決手段】  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】ボンディングパッド部のパッド剥がれを抑制した半導体装置及びその製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、層間絶縁膜8上にバリアメタル層14を形成する工程と、パッド開孔部の下に位置する前記バリアメタル層の少なくとも一部を除去する工程と、前記除去する工程により露出した層間絶縁膜8及び前記バリアメタル層14の上に第2のAl合金膜15を形成する工程と、第2のAl合金膜及び前記バリアメタル層をパターニングすることにより、前記層間絶縁膜上にボンディングパッド部17aを形成する工程と、前記ボンディングパッド部及び前記層間絶縁膜の上にパッシベーション膜18を形成する工程と、前記パッシベーション膜に、前記ボンディングパッド部上に位置するパッド開孔部を形成する工程と、を具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】 簡易な方法でヒューズを溶断することにより製造コストを低減できる半導体装置及びその製造方法を提供する。

【解決手段】 本発明に係る半導体装置は、層間絶縁膜20上に形成されたヒューズ素子22と、前記ヒューズ素子22の一端に繋げられた第1のパッド23aと、前記ヒューズ素子22の他端に繋げられた第2のパッド23bと、ヒューズ素子22、第1、第2のパッド23a,23b及び層間絶縁膜20の上に形成されたパッド保護膜24と、パッド保護膜24に形成され、第1のパッド23a上に位置する第1のパッド開口部24aと、パッド保護膜に形成され、第2のパッド23b上に位置する第2のパッド開口部24bとを具備し、ヒューズ素子22は、第1のパッドと第2のパッドとの間に電流を流して溶断されるものである。

(もっと読む)

非結晶性炭素膜を犠牲ハードマスクとして用いる半導体素子の製造方法

【課題】 本発明は、犠牲ハードマスクのエッチング選択比を増加させ、パターン変形を最小化できる半導体素子の製造方法を提供すること。

【解決手段】 本発明は、被エッチング層上に犠牲ハードマスク用の非結晶性炭素膜を形成するステップと、該犠牲ハードマスク用の非結晶性炭素膜上にフォトレジストパターンを形成するステップと、該フォトレジストパターンをエッチングマスクとして前記犠牲ハードマスク用の非結晶性炭素膜をエッチングし、犠牲ハードマスクを形成するステップと、少なくとも前記犠牲ハードマスクをエッチングマスクとして前記被エッチング層をエッチングし、所定のパターンを形成するステップとを含む。

(もっと読む)

半導体装置の製造方法

【課題】コリメータを備えるスパッタリング装置の生産効率を向上させることのできる技術を提供する。

【解決手段】上部シールド13の上部折曲部13aと下部折曲部13bとの上下垂直位置の距離を相対的に短く、上部シールド13の下縁部の内径を相対的に広くして、ターゲット3と上部シールド13との間の隙間量を相対的に広くし、さらに台座リング15の内径を相対的に広く、台座リング15の高さを相対的に低くして、パッキングプレート11(ターゲット3)と台座リング15との間の隙間量を相対的に広くすることにより、ターゲット3と上部シールド13との接触またはパッキングプレート11(ターゲット3)と台座リング15との接触を回避する。

(もっと読む)

エッチング方法及び絶縁膜のパターニング方法

【課題】 無機ポーラス低誘電率材料に及ぼすダメージを大幅に低減し、容易且つ確実にビア孔及び配線溝の形成等を行う。

【解決手段】 SiOC系低誘電率材料からなる第1の絶縁膜112と、ポーラスシリカからなる第2の絶縁膜113を積層して配線間絶縁膜111を形成し、CF4を含有するエッチングガスで第2の絶縁膜113を、C4F6を含有するエッチングガスで第1の絶縁膜112をそれぞれドライエッチングする。

(もっと読む)

半導体装置及びその製造方法

【課題】 微細化された半導体装置において、半導体素子相互間及び配線相互間に層間絶縁膜が十分に埋め込む。

【解決手段】半導体基板1に形成された半導体素子と、半導体素子上及び半導体基板1上に位置し、下地膜としての第1の絶縁膜9aと、第1の絶縁膜9a上に位置し、O3とTEOSを反応させるCVD法により形成された第2の絶縁膜9bと、第2の絶縁膜9b上に位置し、プラズマCVD法により形成され、表面がCMP法により平坦化された第3の絶縁膜9cと、第1乃至第3の絶縁膜に形成され、半導体素子上に位置する接続孔10a,10bと、接続孔10a,10bに埋め込まれた導電体11a,11bと、第3の絶縁膜9c上に形成され、導電体11a,11bを介して半導体素子に接続する配線12a,12bとを具備する。

(もっと読む)

2,661 - 2,680 / 2,805

[ Back to top ]