Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

2,681 - 2,700 / 2,805

銅の配線層を形成する方法

【課題】 少なくとも1つの窪みを有する第1領域と、前記少なくとも1つの窪みのアスペクト比とは異なるアスペクト比を有する窪みが複数個並んだ第2領域とを有する半導体構造に、低コストで銅の配線層を形成する方法を提供すること。

【解決手段】 本方法は、線幅の異なる2以上の溝を有する半導体構造に、第1の硫酸濃度を有するめっき液で銅の導電層を形成する第1工程と、前記第1の硫酸濃度より薄い第2の硫酸濃度を有するめっき液で、前記導電層上に更に導電層を積層する第2工程と、前記半導体構造上に成膜された銅の導電層を研磨する研磨工程とを有する。これにより、線幅の異なる2以上の溝を有する半導体構造に、低コストで銅の配線層を形成することができる。

(もっと読む)

ガス層形成材料

本発明は、アセナフチレンホモポリマー、アセナフチレンコポリマー、ポリ(アリーレンエーテル)、ポリアミド、B−ステージ多官能性アクリレート/メタクリレート、架橋スチレンジビニルベンゼンポリマー、およびスチレンとジビニルベンゼンとマレイミドまたはビス−マレイミドとのコポリマーから成る群から選択されるガス層形成材料を提供するものである。形成されたガス層はマイクロチップおよびマルチチップモジュールにおいて使用される。  (もっと読む)

(もっと読む)

デュアルダマシン配線の製造方法

【課題】本発明は、信頼性のあるトレンチのプロファイルを確保することができるデュアルダマシン配線の製造方法を提供する。

【解決手段】本発明のデュアルダマシン配線の製造方法は、(a)基板上に下部配線を形成する段階と、(b)下部配線上に絶縁膜を形成する段階と、(c)絶縁膜上にハードマスクを形成する段階と、(d)ハードマスクをエッチングマスクで用いて絶縁膜内にビアを形成する段階と、(e)ハードマスクをビアと連結されるとともに配線が形成されるトレンチを規定するトレンチ用ハードマスクに再パターニングする段階と、(f)トレンチ用ハードマスクをエッチングマスクとして用いて絶縁膜を一部エッチングしてビアと連結されるとともに配線が形成されるトレンチを形成する段階と、(g)トレンチ用ハードマスクを湿式エッチングで除去する段階と、(h)トレンチ及びビアを配線物質で充填して配線を形成する段階を含む。

(もっと読む)

半導体装置の製造方法

【課題】めっき膜に取り込まれる不純物を低減させて、凹部内の配線における欠陥を減少させることが可能な半導体装置の製造方法を提供する。

【解決手段】まず、表面にビアホール1a及び配線溝1bを有するウェハWをめっき液に浸漬させ、かつウェハWとアノード11との間に電圧を印加して、ウェハW上にめっき膜4を形成する。めっき膜4を形成した後に、電圧を印加した状態でウェハWをめっき液から取り出す。そして、シード膜3及びめっき膜4に熱処理を施し、結晶を成長させて、配線膜5を形成する。最後に、ビアホール1a及び配線溝1bに埋め込まれた部分以外の配線膜5等を除去し、配線5aを形成する。

(もっと読む)

半導体装置の製造方法、半導体装置、及び電子機器

【課題】 積層された半導体チップの接合強度が高く、これにより高い信頼性を確保することができる半導体装置の製造方法及び半導体装置、並びに当該半導体装置を備える電子機器を提供する。

【解決手段】 半導体基板10を貫通する電極20,21を有する半導体装置の製造方法であって、集積回路が形成された半導体基板10の能動面10aから半導体基板10の内部にかけて孔部H3を形成する工程と、孔部H3の内側に導電材料を充填して第一接続端子20を形成する工程と、半導体基板10を裏面側10bから薄板化して、電極20の先端部を露出させる工程と、先端部の周辺に導電材料を配置して第二接続端子21を形成する工程と、を有する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】接続孔の直径を小さくしても、接続孔に埋め込まれたプラグと、プラグ上の配線との接触抵抗を低くする。

【解決手段】第1の導電層4上に、絶縁膜8を形成し、絶縁膜8に、第1の導電層4上に位置する接続孔8cを形成する。接続孔8cの中及び絶縁膜上に導電膜を形成し、さらに、絶縁膜8a上に位置する導電膜をCMP法で除去することにより、接続孔8cに導電体9を埋め込む。接続孔8cに埋め込まれた導電体9の表層を、不活性イオンを用いたスパッタエッチングにより除去し、その後、絶縁膜8上に、導電体9に接続する第2の導電層10aを形成する。

(もっと読む)

銅からなる配線を有する半導体装置及びその製造方法

【課題】 十分なエレクトロマイグレーション耐性及びストレスマイグレーション耐性を得ることができる半導体装置を提供する。

【解決手段】 下地基板の上に、絶縁材料からなる第1の層間絶縁膜が形成されている。第1の層間絶縁膜をビアホールが貫通する。ビアホール内に、銅または銅を主成分とする合金からなる導電プラグが充填されている。第1の層間絶縁膜の上に、絶縁材料からなる第2の層間絶縁膜が形成されている。第2の層間絶縁膜に、導電プラグ上を通過して導電プラグの上面を露出させる配線溝が形成されている。配線溝内に、銅または銅を主成分とする合金からなる配線が充填されている。導電プラグ中の炭素、酸素、窒素、硫黄、及び塩素の原子濃度の合計が、配線中の炭素、酸素、窒素、硫黄、及び塩素の原子濃度の合計よりも低い。

(もっと読む)

半導体装置の製造方法

【課題】 貫通電極を有した半導体装置の製造方法において、工程を簡略化して製造コストを極力低く抑えると共に、歩留まりの向上を図る。

【解決手段】 半導体基板10の表面に第1の絶縁膜11を形成し、その一部をエッチングして、半導体基板10の一部を露出する開口部11aを形成する。次に、開口部11a内から第1の絶縁膜11上に延びるパッド電極12を形成する。半導体基板10の裏面上には第2の絶縁膜15を形成する。次に、開口部11aよりも大きい開口径を有したビアホール16を形成する。そして、ビアホール16内から第2の絶縁膜15上に延びる第3の絶縁膜17を形成し、ビアホール16の底部の第3の絶縁膜17をエッチングしてパッド電極12を露出する。その後、ビアホール16内に貫通電極19及び配線層20を形成する。最後に、半導体基板10を複数の半導体チップ10Aに切断分離する。

(もっと読む)

ドライエッチング方法および半導体装置の製造方法

【課題】 レジスト膜をマスクにした被加工材料のドライエッチングにおいて、レジスト膜の荒れを抑制しパターン側壁のストライエーションを低減させる。

【解決手段】 下層配線1上に第1エッチングストッパー層2、Low−k膜3、キャップ層4を積層して形成し、上記キャップ層4上にARC膜5、および配線溝パターン7を有するレジストマスク6を形成する。そして、少なくとも炭素およびフッ素を含むガスであって上記炭素に対するフッ素の原子比率が4以上になるガスをプラズマ励起し、レジストマスク6をエッチングのマスクにして層間絶縁膜になるキャップ層4およびLow−k膜3をドライエッチングして、上記層間絶縁膜に配線溝8を形成する。

(もっと読む)

多層配線構造と多層配線構造を有する半導体装置とこれらの製造方法

【課題】 多層配線構造における上層配線の下層配線に対する接続部の形成にあたり、その接続導体の接続部の清浄化処理において問題となる特性劣化を確実に回避する。

【解決手段】 下層配線溝(第1配線溝)11g内の埋込み配線(第1埋込み配線)11bに上層配線(第2埋込み配線)12bが接続導体12cを介して接続される構成において、接続導体12cの形成時の第1埋込み配線11b表面の水素ラジカルないしは水素ブラズマによる清浄化に耐性を有する保護膜7を、この清浄化の雰囲気にさらされ侵食される第2埋込み配線12bが埋め込まれる配線溝12g、接続導体12cが充填される配線接続孔12hの内表面に形成することによって、上述した清浄化に際して絶縁層が侵食されることを回避し、充分な洗浄を行うことができるようにして特性劣化の改善を図る。

(もっと読む)

半導体装置の製造方法

【課題】 貫通電極を有する半導体装置の製造方法において、半導体装置の信頼性及び歩留まりの向上を図る。

【解決手段】 パッド電極11に対応した位置で半導体基板10を貫通するビアホール16を形成する。次に、ビアホール16を含む半導体基板10の裏面上に絶縁膜17を形成する。次に、半導体基板10の裏面上に、ビアホール16の開口部の縁でオーバーハング部18aを有する補強用絶縁膜18を形成する。そして、補強用絶縁膜18をマスクとして、ビアホール16の側壁の絶縁膜17を残存させつつ、当該底部の絶縁膜17をエッチングして除去する。次に、ビアホール16を含む半導体基板10の裏面に、貫通電極21、配線層22、及び導電端子24を形成する。最後に、ダイシングにより半導体基板10を半導体チップ10Aに切断分離する。

(もっと読む)

半導体装置及びその製造方法

【課題】 ボンディング工程、CMP工程、熱応力等による機械的衝撃やウエハの変形によるビアの変位を小さく制御できる半導体装置及びその製造方法を提供する。

【解決手段】 第1配線22と、第1配線22の上に配置された低誘電率絶縁膜310と、低誘電率絶縁膜310の中に第1配線22と接続するように埋め込まれ、第1配線22の長手方向に測った第1長さLx、第1配線22が配置された平面で第1配線22に直交する方向に測った第2長さLy、第1配線22が配置された平面に垂直な高さHに対する第1及び第2長さLx,Lyの少なくとも一方との比が1以上である複数の第1扁平ビア31a,31bと、低誘電率絶縁膜310の上に配置され、複数の第1扁平ビア31a,31bにそれぞれ接続された第2配線32とを備える。

(もっと読む)

半導体装置の製造方法

【目的】 不純物の残留を抑制し、バリアメタルを高純度に成膜することを目的とする。

【構成】 基体上にTa[N((CH3)2]5を供給するTa[N((CH3)2]5供給工程(S102)と、前記Ta[N((CH3)2]5におけるTaとは異なるCを除去するH2供給工程(S106)と、前記Cが除去された前記Ta[N((CH3)2]5の吸着分子に基づいて前記TaN膜を生成するNH3供給工程(S108)と、を備え、前記Ta[N((CH3)2]5工程とH2供給工程とNH3供給工程とを繰り返すことで、前記基体上にTaN膜を堆積させることを特徴とする。

(もっと読む)

導電性材料とその製法

【課題】銅を含む導電性コア領域と界面領域とを有する導電性材料及び該導電性材料の製造方法を提供すること。

【解決手段】銅と、0.001原子百分率から0.6原子百分率までの、イリジウム、オスミウム、及びレニウムから選択された1つ又はそれ以上の金属とを含む導電性コア領域、及び界面領域を備える導電性材料である。界面領域は、少なくとも80原子百分率又はそれ以上の1つ又はそれ以上の金属を含む。界面領域は、銅と、イリジウム、オスミウム、及びレニウムから選択された1つ又はそれ以上の金属とを含むシード層を形成し、その上に銅からなる導電性層を形成し、導電性層を研磨して、研磨された銅の表面材料を構成し、シード層から研磨された表面への1つ又はそれ以上の金属のマイグレーションを引き起こすのに十分な温度で該研磨された銅の表面材料をアニールして形成される。

(もっと読む)

半導体装置の製造方法

【目的】 CVD法により形成された多孔質low−k膜上にバリアメタルを連続に形成することを目的とする。

【構成】 基体上に、有機物質原料を用いてCVD法により多孔質絶縁膜を形成するポーラスlow−k膜形成工程(S104)と、前記ポーラスlow−k膜表面に結合されるCH3基をエッチングするエッチング工程(S112)と、前記CH3基がエッチングされた前記ポーラスlow−k膜表面にALD法によりバリアメタル膜を形成するバリアメタル膜形成工程(S114)と、を備えたことを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】生産性の低下を招くことなく、接続孔形成の際のリソグラフィにおける露光マージンを広げることが可能で、これにより歩留まり向上およびさらなる微細化が可能な半導体装置およびその製造方法を提供する。

【解決手段】基板上に設けられた下層配線3と、下層配線3を覆う第2層間絶縁膜5と、下層配線3に達する状態で第2層間絶縁膜5に設けられた接続孔5a内を導電性材料で埋め込んでなるビア7と、ビア7に接続された状態で第2層間絶縁膜5上にパターン形成された上層配線9とを備えた半導体装置において、接続孔5は、上層配線9の延設方向に長い開口形状を有しており、また上層配線9側から下層配線3側にかけて連続した傾斜角度θを有して開口径が狭くなるテーパ形状に整形されている。

(もっと読む)

半導体装置の製造方法

【課題】 安定した低抵抗のシリサイド膜を形成する技術を提供する。

【解決手段】 半導体基板1上にゲート絶縁膜5を形成する工程、ゲート絶縁膜5上にシリコン膜7を形成する工程、シリコン膜7と半導体基板1との表面にBF2イオンおよびBイオンを注入し、pチャネル型MISトランジスタQpのゲート電極11pと高濃度n型半導体領域15からなるソース/ドレインとを形成する工程、ゲート電極11pの上部に第1コバルトシリサイド膜を形成し、ソース/ドレインの上部に第2コバルトシリサイド膜を形成する工程を有する。

(もっと読む)

半導体装置の製造方法、半導体装置、露光マスクおよび露光装置

【課題】基板周辺部における少なくとも第2絶縁膜に複数の凹部を形成するすることで、配線を形成する研磨時の絶縁膜剥がれを防止することを可能とする。

【解決手段】基板11上に少なくとも2層以上の配線層を備えた多層配線を形成する工程を備え、配線層を形成する配線は、基板11上に設けられた絶縁膜に配線用凹部(図示せず)を形成して配線用凹部内に導電膜41を埋め込むように絶縁膜上に導電膜41を形成する工程と、導電膜41を研磨して配線用凹部内に導電膜41を残すことで配線を形成する工程とにより形成される半導体装置の製造方法であって、絶縁膜は、第1絶縁膜21と第2絶縁膜22とを積層したものからなり、絶縁膜上に導電膜41を形成する前に、基板周辺部における少なくとも第2絶縁膜22に複数の凹部31を形成する工程を備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】 配線の終端部におけるボイドの爆発により配線に損傷が生じるのを抑制した半導体装置及びその製造方法を提供する。

【解決手段】 絶縁膜11上に、複数の配線13aを互いに並ぶように形成すると共に、複数の配線13aの端部13c近傍に、複数の配線13aと交わる方向にダミーパターン13bを形成する。次いで、絶縁膜11上、複数の配線13a上、及びダミーパターン13b上に、第2の絶縁膜を形成する。その後、絶縁膜11、複数の配線13a、ダミーパターン13b及び第2の絶縁膜を加熱し、配線13a相互間のボイドが膨張しても、ダミーパターン13bが設けられているため、配線端部の近傍でボイドが爆発するのを防止でき、それにより配線が損傷することを抑制できる。

(もっと読む)

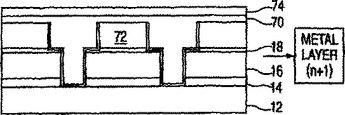

半導体装置および半導体装置の製造方法

【課題】 大電流を流す場合や長期間使用する場合の信頼性が高く、かつ、腐食に対する信頼性の高い配線を備えた半導体装置およびその製造方法を提供する。

【解決手段】 銅配線層30と、銅配線層30に比べ酸素による腐食の少ないアルミ配線層32を銅配線層30の上に形成した積層構造の配線層33を形成する。したがって、配線層33が銅配線層30を有するため、エレクトロマイグレーションによる断線が生じ難く、大電流を流す場合や長期間使用する場合の信頼性を向上させることができる。また、配線層33形成後に配線層33が露出した状態で酸素を含む雰囲気中における処理を行なう場合でも、配線層33が腐食されにくい。すなわち、大電流を流す場合や長期間使用する場合の信頼性が高く、かつ、腐食に対する信頼性の高い配線層33を得ることができる。

(もっと読む)

2,681 - 2,700 / 2,805

[ Back to top ]