Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

2,701 - 2,720 / 2,805

半導体装置の製造方法、半導体装置、露光マスクおよび露光装置

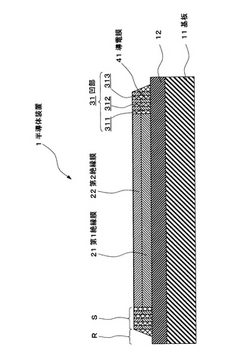

【課題】基板周辺部における少なくとも第2絶縁膜に複数の凹部を形成するすることで、配線を形成する研磨時の絶縁膜剥がれを防止することを可能とする。

【解決手段】基板11上に少なくとも2層以上の配線層を備えた多層配線を形成する工程を備え、配線層を形成する配線は、基板11上に設けられた絶縁膜に配線用凹部(図示せず)を形成して配線用凹部内に導電膜41を埋め込むように絶縁膜上に導電膜41を形成する工程と、導電膜41を研磨して配線用凹部内に導電膜41を残すことで配線を形成する工程とにより形成される半導体装置の製造方法であって、絶縁膜は、第1絶縁膜21と第2絶縁膜22とを積層したものからなり、絶縁膜上に導電膜41を形成する前に、基板周辺部における少なくとも第2絶縁膜22に複数の凹部31を形成する工程を備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】 配線の終端部におけるボイドの爆発により配線に損傷が生じるのを抑制した半導体装置及びその製造方法を提供する。

【解決手段】 絶縁膜11上に、複数の配線13aを互いに並ぶように形成すると共に、複数の配線13aの端部13c近傍に、複数の配線13aと交わる方向にダミーパターン13bを形成する。次いで、絶縁膜11上、複数の配線13a上、及びダミーパターン13b上に、第2の絶縁膜を形成する。その後、絶縁膜11、複数の配線13a、ダミーパターン13b及び第2の絶縁膜を加熱し、配線13a相互間のボイドが膨張しても、ダミーパターン13bが設けられているため、配線端部の近傍でボイドが爆発するのを防止でき、それにより配線が損傷することを抑制できる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 大電流を流す場合や長期間使用する場合の信頼性が高く、かつ、腐食に対する信頼性の高い配線を備えた半導体装置およびその製造方法を提供する。

【解決手段】 銅配線層30と、銅配線層30に比べ酸素による腐食の少ないアルミ配線層32を銅配線層30の上に形成した積層構造の配線層33を形成する。したがって、配線層33が銅配線層30を有するため、エレクトロマイグレーションによる断線が生じ難く、大電流を流す場合や長期間使用する場合の信頼性を向上させることができる。また、配線層33形成後に配線層33が露出した状態で酸素を含む雰囲気中における処理を行なう場合でも、配線層33が腐食されにくい。すなわち、大電流を流す場合や長期間使用する場合の信頼性が高く、かつ、腐食に対する信頼性の高い配線層33を得ることができる。

(もっと読む)

半導体装置の製造方法

【目的】 ポーラス状に形成される多孔質低誘電率(p−lowk)膜内へのバリアメタルに用いたメタルの拡散を抑制することを目的とする。

【構成】 p−lowk膜を基体上に形成するp−lowk膜形成工程(S102)と、前記p−lowk膜表面側に形成される空孔が前記p−lowk膜内部側の空孔へ連結する連結位置における開口サイズより大きい分子(Ta−R1)を前記p−lowk膜表面に吸着させるTa[N(C2H5)2]5供給工程(S106)と、前記分子(Ta−R1)と反応するNH3を供給し、TaN膜を形成するNH3供給工程(110)と、前記開口サイズより小さい分子(Ta−R2)を吸着させるTaCl5供給工程(S114)と、前記分子(Ta−R2)と反応するNH3を供給し、TaN膜をさらに形成するNH3供給工程(120)と、を備えたことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 信頼性の高い半導体装置およびその製造方法を提供する。

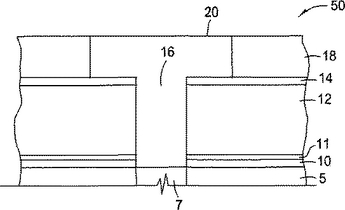

【解決手段】 半導体装置は、層間絶縁膜1と、層間絶縁膜1内に形成された下部配線5と、層間絶縁膜1上に形成されたライナー膜11と、ライナー膜11上に形成された層間絶縁膜12とを備えている。下部配線5に下部孔8が開口しており、ライナー膜11および層間絶縁膜12には下部孔8に繋がる上部孔10が開口しており、下部孔8の口径d2は上部孔の口径d1よりも大きくなっている。さらに、下部孔8の内壁面に形成された導電膜15と、上部孔10の内壁面に沿って形成されたバリアメタル13と、上部孔10内および下部孔8内を埋めるように形成されたCu膜19とを備えている。導電膜15はバリアメタル13と同じ物質を含んでいる。

(もっと読む)

半導体装置およびそれを用いた半導体モジュール

【課題】 貫通電極を少ない面積で高密度に設ける。

【解決手段】 半導体装置100は、シリコン基板101と、シリコン基板101を貫通する断面矩形の貫通孔中に充填された構造体120を設ける。構造体120は、筒状貫通電極103と、ストライプ状貫通電極107と、シリコン105と、第一の絶縁膜109と、第二の絶縁膜111と、第三の絶縁膜113と、を備える。筒状貫通電極103を、シリコン基板101を貫通する筒状の導電体とする。また、ストライプ状貫通電極107を、シリコン基板101を貫通し、筒状貫通電極103の内側に筒状貫通電極103から離間して設ける。筒状貫通電極103の内側の領域に、複数の貫通電極107を互いに略平行に設ける。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】ダマシン配線に含まれる不純物の濃度を低下させて、配線中の欠陥を低減させる事が可能な半導体装置の製造方法を提供する。

【解決手段】ウェハW上の層間絶縁膜1に幅が0.3μm以下の細幅配線溝1a及び幅が0.3μmを超える太幅配線溝1bを形成する。層間絶縁膜1上にバリアメタル膜2及びシード膜3を形成する。その後、細幅配線溝1a全体に埋め込まれ、かつ太幅配線溝1bの一部に埋め込まれるように膜4を電解めっき法により形成する。太幅配線溝1bの他の部分に埋め込まれるように膜4よりも不純物濃度が低い膜5をスパッタ法により形成する。熱処理により膜4中の不純物を膜5中に拡散して、配線膜6を形成する。最後に層間絶縁膜1上の不要なバリアメタル膜2及び配線膜6を除去し、細幅配線と太幅配線を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】下部電極形成工程を別途設けることなく、少ない占有面積で大きな容量を持つMIMキャパシタを備えた半導体装置及びその製造方法を提供する。

【解決手段】MIMキャパシタ形成領域Aの第2の絶縁膜6には、Ta/TaNのようなバリア膜からなる下部電極12とAl2O3のような金属酸化膜からなる容量絶縁膜13とTiNのようなバリア膜からなる上部電極14とを有するMIMキャパシタ15が形成されている。一方、配線形成領域Bの第2の絶縁膜6には、上部に設けられた第2配線部W2と下部に設けられた第2プラグ部P2が一体化形成されたバリア膜8bと導電膜9bからなる第2層配線10bが形成されている。そして、MIMキャパシタ15の下部電極12と第2層配線10bのバリア膜8bは共通のバリア膜を用いて同時に形成されたものである。

(もっと読む)

半導体装置の製造方法及び半導体装置の製造装置

【課題】 溝とビアを有する低誘電率絶縁膜上にバリアメタルを成膜する前のビア底の高抵抗層の除去手段として、プラズマによる絶縁膜ダメージのない半導体装置の製造方法及び製造装置を提供する。

【解決手段】 溝とビアを有する低誘電率絶縁膜102上にバリアメタルを成膜する前に、ビア底の高抵抗層104を、還元性のガスを用いた熱還元法にて除去し、真空保持のまま、バリアメタル105、めっきのシード層としての銅を形成する。

(もっと読む)

半導体装置

【課題】

酸化シリコン層、窒化シリコン層の積層ライナを備えたSTIを有し、帯電を低減できる半導体装置およびその製造方法を提供する。

【解決手段】

半導体装置は、シリコン基板と、前記シリコン基板の表面から下方に向かって形成され、前記シリコン基板の表面に活性領域を画定するトレンチと、前記トレンチの内壁を覆う酸化シリコン層の第1ライナ層と、前記第1ライナ層の上に形成された窒化シリコン層の第2ライナ層と、前記第2ライナ層の上に形成され、前記トレンチを埋める絶縁物の素子分離領域と、前記活性領域に形成されたpチャネルMOSトランジスタと、前記pチャネルMOSトランジスタを覆って,前記シリコン基板上方に形成され,紫外光遮蔽能を有さない窒化シリコン層のコンタクトエッチストッパ層と、前記コンタクトエッチストッパ層の上方に形成され、紫外光遮蔽能を有する窒化シリコン層の遮光膜と、を有する。

(もっと読む)

耐酸化性が良好な次世代ダマシンバリヤ適用のための二層膜

基板を処理する方法であって、フェニル基を含む有機シリコン化合物を含む処理ガスを処理チャンバに供給するステップと、処理ガスを反応させて低k誘電物質によるダマシン又はデュアルダマシン適用においてバリヤ層として用いられる低kシリコンカーバイドバリヤ層を堆積させるステップとを含む、前記方法が提供される。低kシリコンカーバイドバリヤ層上に酸素を含まない有機シリコン化合物を含む処理ガスからのシリコン原子にフェニル基がほとんど結合されていないシリコンカーバイドキャップ層を堆積する方法が提供される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 多孔質絶縁膜を含む層間絶縁膜の誘電率を実効的に低減させ、微細で高信頼性のダマシン配線を有する半導体装置の実用化を容易にする。

【解決手段】 下層配線1上に多孔質の第1低誘電率膜2bを含む第1層間絶縁膜2が形成され、第1低誘電率膜2bに設けられたビアホール3の側壁に第1サイドウォールメタル4が形成され、その後に第1エッチングストッパー層2aがエッチングされて下層配線1が露出される。そして、ビアホール3内にビアプラグ5が埋め込まれる。同様に、多孔質の第2低誘電率膜6bを含む第2層間絶縁膜6のトレンチ7内の側壁に第2サイドウォールメタル8設けられた後に第2エッチングストッパー層6aがエッチングされ上記ビアプラグ5に接続する上層配線9が形成される。

(もっと読む)

配線形成方法及び配線形成装置

【課題】 基板表面に配線用の微細凹部を形成した後の一連の配線形成処理を、ドライ処理とウェット処理の混合した処理を経ることなく連続的に安定して行えるようにする。

【解決手段】 表面に堆積した絶縁膜62の内部に配線用の微細凹部64を形成した基板Wを用意し、この基板Wの表面にウェット処理によりバリア層68を形成し、このバリア層68の表面にウェット処理によりシード層70を形成し、このシード層形成後の基板の表面にウェット処理により配線層72を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の更なる微細化に対応可能な、微細化されたコンタクトが確実に形成された素子特性に優れ、歩留まりの良い半導体装置、およびその製造方法を得る。

【解決手段】半導体基板上にゲート絶縁膜を介してゲート電極を形成する工程と、前記ゲート電極を覆うエッチング保護膜を形成する工程と、前記エッチング保護膜を覆うように前記半導体基板上にバリアメタル層を形成する工程と、前記バリアメタル層上に導電性材料を堆積して導電性膜を形成する工程と、前記導電性膜上にレジストマスクを形成する工程と、前記レジストマスクをエッチングマスクとして前記導電性膜を選択的にエッチング除去してコンタクトを形成する工程と、前記レジストマスクを除去する工程と、前記半導体基板上における前記導電性膜がエッチング除去された領域に絶縁性材料を堆積して層間絶縁膜を形成する工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】 配線間の絶縁膜を可能な限り除去して十分に低誘電率化を図り、エアギャップ形成時に配線にダメージを与えない構造を設けることで信頼性を向上させた半導体装置を提供する。

【解決手段】 複数の配線を内部に形成した絶縁膜6の上下層に当該絶縁膜6よりウェットエッチング耐性が高い絶縁膜5,9を形成してなる配線層部と、絶縁膜6よりウェットエッチング耐性が高い材料からなり、配線を被覆するようにその周囲に形成された絶縁膜7と、上下層の絶縁膜5,9及び絶縁膜7と配線が内部に形成された絶縁膜4とのエッチング耐性の違いに基づいて、上下層の絶縁膜5,9及び絶縁膜7で囲まれた配線間の絶縁膜4を選択的にエッチング除去してなるエアギャップ部12とを備える。

(もっと読む)

半導体装置

【課題】パッド部に流れる過電流が抑制されてパッド部におけるESD耐性が向上された半導体装置を提供する。

【解決手段】基板2上に第1の電位が与えられた第1のパッド8と、パッド8に電気的に接続された第1の導電層5が設けられている。基板2との間に少なくとも1層の第1の導電層5を挟んで第1の電位とは異なる第2の電位が与えられている第2のパッド13が設けられているとともに、少なくとも1層の第2の導電層10がパッド13に電気的に接続されてパッド8,13と基板2との間に設けられている。基板2上には、複数層の絶縁層4が積層されて設けられている。各絶縁層4は、パッド8および導電層5の少なくとも一方とパッド13および導電層10の少なくとも一方との間で容量絶縁膜となる。

(もっと読む)

半導体装置およびその製造方法

【課題】 セルフアライン形成技術によりセルフアライン形成領域の絶縁膜に形成されたコンタクトホールの径に比較してさらに開孔幅の大きな穴部を絶縁膜の上部に形成するためセルフアライン形成領域を再度エッチング処理する必要があったとしても、セルフアライン形成領域内のセルフアラインマスク膜に悪影響が及ぼされることなく、さらにセルフアライン形成領域に対して複数回に分けて接続配線を埋込み形成する必要をなくす。

【解決手段】 領域CB2に対して第1のコンタクトホール16を形成した後、フォトレジスト38、塗布型酸化膜39、フォトレジスト40の3層構造の多層レジスト構造41を形成し、第5のシリコン酸化膜23の上部に穴部24および25を形成する。

(もっと読む)

半導体装置の製造方法及び半導体装置の製造装置

【課題】 本発明は上記問題を解決するためになされたもので、空孔を有する低誘電率絶縁膜上にバリアメタルを成膜する前におけるビア底の高抵抗層の除去手段として、プラズマを用いない新規な半導体装置の製造方法及び製造装置を提供することにある。

【解決手段】 本発明は、低誘電率絶縁膜(102)上にバリアメタルを成膜する前に、ビア底の高抵抗層(104)を除去してなる半導体装置の製造方法において、前記ビア底の高抵抗層(104)を、熱を加えながら、還元性のガスを用いた熱還元法にて除去し、真空保持のまま、バリアメタル(105)、めっきのシード層としての銅を形成することを特徴とする半導体装置の製造方法である。

(もっと読む)

半導体装置及びその製造方法

【課題】 機械的強度に優れると共に、低抵抗であって且つ絶縁膜に対する密着性の高いバリアメタル膜を有する半導体装置を提供する。

【解決手段】 基板(1)上に形成された絶縁膜(6)と、絶縁膜(6)中に形成された埋め込み金属配線(10)と、絶縁膜(6)と金属配線(10)との間に形成されたバリアメタル膜(A1)とを備えた半導体装置において、バリアメタル膜(A1)は、絶縁膜(6)が存在している側から金属配線(10)が存在している側へ向かって順に積層されている金属酸化物膜(7)、金属化合物膜(8)及び金属膜(9)よりなる。金属化合物膜(8)の弾性率は、金属酸化物膜(7)の弾性率よりも大きい。

(もっと読む)

半導体装置およびその製造方法

【課題】 貫通電極を有する半導体装置において、少ない面積で高密度に貫通電極を設ける。

【解決手段】 半導体装置100において、シリコン基板101を貫通する孔に充填された多重貫通プラグ111を設ける。多重貫通プラグ111は、円柱状で中実の第一の貫通電極103、第一の貫通電極103の円筒面を覆う第一の絶縁膜105、第一の絶縁膜105の円筒面を覆う第二の貫通電極107、および第二の貫通電極107の円筒面を覆う第二の絶縁膜109からなり、これらは同じ中心軸を有する。また、第一の絶縁膜105、第二の貫通電極107および第二の絶縁膜109の上断面は円環状とする。

(もっと読む)

2,701 - 2,720 / 2,805

[ Back to top ]