Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

2,721 - 2,740 / 2,805

半導体装置の配線構造体及びその形成方法

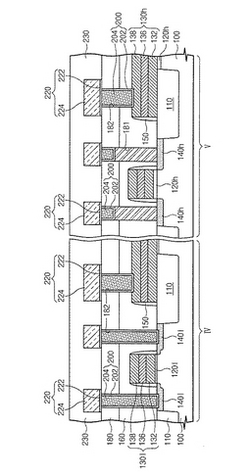

【課題】 半導体装置の配線構造体およびその形成方法を提供する。

【解決手段】 この半導体装置は半導体基板100上に配置された層間絶縁膜、前記層間絶縁膜を貫通する第1コンタクト構造体181および第2コンタクト構造体182、前記層間絶縁膜上に配置されて前記第1コンタクト構造体と前記第2コンタクト構造体に連結される金属配線220を具備する。この際、前記第1コンタクト構造体は順次に積層された第1プラグおよび第2プラグ200を含み、前記第2コンタクト構造体は前記第2プラグを含む。

(もっと読む)

半導体装置の製造方法

【課題】 寄生容量の増加を抑制しつつ、所望のゲート耐圧を有するパワーMISFETを製造できる技術を提供する。

【解決手段】 基板上に多結晶シリコン膜を堆積し、その多結晶シリコン膜で溝部7、8を埋め込んだ後、その多結晶シリコン膜をパターニングすることにより、活性セル領域においては溝部7内にてゲート電極11を形成し、ゲート配線領域においては溝部8内を埋め込み、一部が溝部8内から連続して溝部8の外部に延在し、ゲート電極11と電気的に接続するゲート引き出し電極12を形成し、溝部8外のゲート引き出し電極12には、ゲート引き出し電極12の端部から延在するスリット14を形成する。その後、基板上に酸化シリコン膜19およびBPSG膜20を堆積する。

(もっと読む)

薄膜トランジスタの作製方法

【課題】 しかし、薄膜トランジスタを有する表示装置では、同一対象物、例えば同一絶縁膜のエッチング条件を最適化することが難しかった。これは、同一絶縁膜において、エッチングする絶縁膜の膜厚や面積が異なるためである。特に面積の小さなコンタクトホールは、エッチングする量がその他の開口部と異なる。

【解決手段】 上記課題を鑑み本発明は、第1のマスクを用いて、第1の領域の対象物をエッチングして広面積な開口部を形成し、第2のマスクを用いて、第2の領域の前記対象物をエッチングして微細な開口部、つまりコンタクトホールを形成することを特徴とする。

(もっと読む)

基板処理方法及び装置

【課題】 CMPによって形成した配線の表面に、配線の信頼性を低下させることなく、無電解めっきによって、保護膜を安定して形成でき、しかもスロープットを向上させることができるようにする。

【解決手段】 表面に配線用凹部を形成し配線材料を該配線用凹部内へ埋め込みつつ成膜した基板を用意し、該凹部内以外の余剰な配線材料を化学的機械研磨により除去して該凹部内の配線材料を配線と成し、前記研磨直後に基板の表面を洗浄液に接触させて研磨残渣と配線表面の酸化膜を除去し、前記洗浄液に接触させた基板表面を触媒処理液に接触させて前記配線の表面に触媒を付与し、前記触媒を付与した基板表面を洗浄した後、乾燥させる。

(もっと読む)

半導体素子の製造方法

【課題】 シリコンを含むN型の導電領域と直接接続される導電パターンの形成時に、N型の導電領域と接続される部分のコンタクト抵抗の増大を防止し、バリア膜の厚さ増大に伴う導電パターンの寄生容量の増大を防止できる半導体素子の製造方法を提供すること。

【解決手段】 シリコンを含むN型の導電領域(207)にN型の不純物をドープして、N型の高濃度不純物拡散領域(212)を形成する工程と、CVD法を用いて高濃度不純物拡散領域(212)上にバリア用第1金属膜を蒸着し、高濃度不純物拡散領域(212)のシリコンと前記第1金属膜の金属とを反応させて、高濃度不純物拡散領域(212)と前記第1金属膜との間の界面に金属シリサイドを形成する工程、前記第1金属膜上に導電膜を形成する工程、及び、前記導電膜と前記第1金属膜とを選択的にエッチングして、導電パターンを形成する工程を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体装置の小型化を可能にする。

【解決手段】 基板21上のエピタキシャル層22に、ゲート電極32と、n-型オフセットドレイン領域35、n型オフセットドレイン領域39およびn+型ドレイン領域42からなるドレイン領域と、n-型ソース領域36およびn+型ソース領域43からなるソース領域とを有するLDMOSFEを形成するとともに、n型ウエル27上に複数のショットキ電極52を形成してショットキ電極52およびn型ウエル27間にショットキ接合を形成することでショットキダイオード素子を形成している。複数のショットキ電極52はプラグ63およびアノード電極74を介して互いに電気的に接続されている。複数のショットキ接合部の間および両側に設けられたn+型半導体領域44は、プラグ63およびカソード電極73を介して互いに電気的に接続されている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 誘電体膜の段差被覆性がよく、かつ誘電体物質の廃棄量を少なくする。

【解決手段】 下地膜8上に、パターニングされた下部電極11を形成する工程と、インクジェット方式の塗布機構を用いて、下部電極11上に誘電体物質を塗布する工程と、塗布された誘電体物質を加熱することにより、下部電極11上に誘電体膜12を形成する工程と、誘電体膜12上に上部電極を形成する工程とを具備する。上部電極を形成する工程は、下地膜8上及び誘電体膜12上に層間絶縁膜を形成する工程と、層間絶縁膜に、誘電体膜上に位置する開口部を形成する工程と、開口部の中及び層間絶縁膜上に導電体を堆積する工程と、層間絶縁膜上から導電体を除去することにより上部電極を形成する工程とを具備する。

(もっと読む)

基板処理方法及び装置

【課題】 例えば配線等の下地金属の内部にボイドを発生させることなく、下地金属の露出表面に無電解めっきによって金属膜を確実に形成でき、しかも、スループットを向上させることができるようにする。

【解決手段】 下地金属を形成した基板の表面に無電解めっきにより金属膜を形成するに際し、基板の表面を、カルボキシル基を有する有機酸またはその塩の水溶液に界面活性剤を添加した洗浄液で洗浄し、洗浄後の基板の表面を、金属触媒イオンを含む溶液に前記洗浄液を混合した処理液に接触させて基板の表面に触媒を付与する。

(もっと読む)

半導体装置及びその製造方法

【課題】 多孔質絶縁膜を含む層間絶縁膜の誘電率を実効的に低減させ、微細で高信頼性のダマシン配線を有する半導体装置の実用化を容易にする。

【解決手段】 下層配線1上に多孔質の第1低誘電率膜2bを含む第1層間絶縁膜2が形成され、第1層間絶縁膜2に設けられたビアホール3内にその側壁に設けられた第1側壁保護膜4を介して第1バリア層5およびビアプラグ6が形成される。同様に、多孔質の第2低誘電率膜7bを含む第2層間絶縁膜7のトレンチ8内にその側壁に設けられた第2側壁保護膜9を介して第2バリア層10および上層配線11が形成される。ここで、第1側壁保護膜4および第2側壁保護膜9は多孔質の低誘電率膜で成り、その空孔の含有率は30%以下であり、空孔の寸法は2nm以下である。

(もっと読む)

半導体装置及びその製造方法

【課題】 本発明の目的は、低抵抗であって且つ絶縁膜及び配線との間で高い密着性を有するバリアメタル膜を有する半導体装置を提供する。

【解決手段】 半導体装置は、基板(1)上に形成された絶縁膜(6,8)と、絶縁膜(6,8)中に形成された埋め込み配線(14)と、絶縁膜(6,8)と埋め込み配線(14)との間に形成されたバリアメタル膜(A1)とを有する。バリアメタル膜(A1)は、絶縁膜(6,8)が存在している側から埋め込み配線(14)が存在している側へ向かって順に積層されている金属酸化物膜(11)、遷移層(12a)及び金属膜(13)よりなり、遷移層(12a)は、金属酸化物膜(11)の組成と金属膜(13)の組成とのほぼ中間的な組成を有する単一の原子層よりなる。

(もっと読む)

半導体装置及びその製造方法

【課題】静電破壊耐性を向上し得る半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極とドレイン領域とソース領域とを有する半導体装置であって、ドレイン領域は、ゲート電極の第1の側に形成された第1導電型の第1の不純物拡散領域18aと;第1の不純物拡散領域より深く形成された第1導電型の第2の不純物拡散領域20aと;第1の不純物拡散領域より浅く形成され、不純物拡散層より不純物濃度が高い第1導電型の第3の不純物拡散領域28a、28bと;第3の不純物拡散領域上に形成され、ドレインコンタクト部22Dに接続されるシリサイド膜32a、32bとを有し、ドレインコンタクト部とサイドウォール絶縁膜との間にシリサイド膜が形成されていない領域が存在しており、ドレインコンタクト部の下方の半導体基板内に第2の不純物拡散領域が形成されていない。

(もっと読む)

半導体装置

【課題】 銅を主構成材料とする配線構造において、ストレスマイグレーションによるボイドの発生を抑制し、信頼性の高い半導体装置を提供する

【解決手段】 半導体基板上の絶縁膜上に形成される多層配線構造において、主構成材料が銅からなる第1の配線の上面に接するように、下から順にバリア性が高く、かつ圧縮応力を有する第1の絶縁膜、引張応力を有する第2の絶縁膜、前記第1の絶縁膜と前記第2の絶縁膜よりも誘電率の低い第3の絶縁膜が少なくとも積層されており、前記第1の絶縁膜、前記第2の絶縁膜、および前記第3の絶縁膜を貫通し前記第1の配線に接するようにビアホールが設けられている配線構造とする。

(もっと読む)

半導体装置

【課題】 ダマシン配線構造体を有する半導体装置において、シールリングと配線あるいは電極パッドとの短絡発生を無くする。

【解決手段】 半導体装置の層間絶縁膜の溝側壁に形成され導電性のバリア材料膜から成る上層バリア層4、溝内に埋め込まれ配線材料膜から成るたとえば10μm幅の上層シールリング配線5が設けられ、上層シールリング配線5内に混在して複数の島状の絶縁体6が形成されている。この島状の絶縁体6は、上記ダマシン配線が形成される層間絶縁膜により形成される。そして、素子形成領域に第1上層溝配線7、第2上層溝配線8等が配設され、上層バリア層4がその周囲に設けてある。ここで、上層シールリング配線5および両上層配線は共に(デュアル)ダマシン配線構造になる。

(もっと読む)

導線近傍にスキャッタリング・バーを配置させてなる半導体デバイス

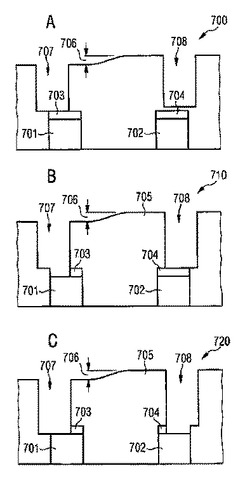

【課題】

疎密のパターンを備える半導体デバイス100のリソグラフィー技術を改善する方法を提供する。

【解決手段】

スキャッタリング・バー108aおよび108bを孤立した導線106bの両側に配置することによりリソグラフィーの結果を改善する半導体デバイス100の製造方法である。このスキャッタリング・バー108aおよび108bは、半導体デバイスパターニング時における孤立した導線106bの焦点深度を向上させるに十分な幅を有し、かつ、該導線106bの焦点深度を向上させるに十分な距離だけ該孤立した導線106bから離間させて配置される。半導体デバイス100の製造が終了した後にも、このスキャッタリング・バー108aおよび108bは残したままとする。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置、例えばSRAMのメモリセルのα線によるソフトエラーを低減する。

【解決手段】基板1aをエッチングして第1配線溝HM1を形成し、第1配線溝HM1下の素子分離2(または素子分離溝2および絶縁層1c)をエッチングして第2配線溝HM2を形成し、第1配線溝HM1および第2配線溝HM2の内壁に沿って局所配線16a,16bを形成し、一方の局所配線16aを下部電極ELとして、その下部電極EL上に容量絶縁膜となる窒化シリコン膜17、さらに上部電極EUを形成することにより、容量CA1の面積を増加させて、メモリセルの記憶ノードに相対的に大きな静電容量を付加する。

(もっと読む)

半導体装置

【課題】Low−k膜を層間絶縁膜として用いた半導体装置であっても、ダイシング時に発生するクラックがシールリング部へ伝播するのを抑制し、半導体装置の信頼性を向上する技術を提供する。

【解決手段】ダイシング領域側の各層にダミービア125,135,145,155,165を形成する。ダミービア125,135,145,155,165は上面からみて、縦横に等間隔に形成する。ダイシング時にクラックが発生しても、ダミービア125,135,145,155,165によって、クラックがシールリング部190にまで伝播するのを抑制することができる。その結果、回路形成領域の吸湿耐性を向上させ、信頼性の劣化を防止することができる。

(もっと読む)

半導体装置

【課題】 ボンディングパッドの下面にも電子部品を配置することができる構造を備えた半導体装置を提供する。

【解決手段】 外部接続端子を構成するボンディングパッド24と、ボンディングパッド24の下面に、少なくとも二層の銅膜44,16と、前記隣接する銅膜44,16同士を接続するように設けられる接続ビア18から形成されるボンディングパッド下部領域48と、ボンディングパッド下部領域48を取り囲むように銅膜および隣接する銅膜同士を接続する環状導体より構成されるシールリング42と、シールリング42の外側においてボンディングパッド24に接続される配線26と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】 アスペクト比の大きいコンタクトプラグにおいて、タングステン層等のプラグ用の下地導電層を形成した場合に、剥離による不良を低減することができる半導体装置の製造方法を提供する。

【解決手段】 導電層2の上に形成された層間絶縁層3を有するシリコン基板1において、層間絶縁層3の上にコンタクトホール5を形成するためのマスクを形成するマスク形成工程と、層間絶縁層3をドライエッチング法によりコンタクトホール5を形成するコンタクトホール形成工程と、コンタクトホール5内に導電層6aを形成する導電層形成工程と、前記コンタクトホール内に導電層6aよりも低応力の低応力導電層6bを形成する低応力導電層形成工程とを有する。

(もっと読む)

層構造の製造方法

本発明は、層構造の製造方法に関するものである。導電層および犠牲層をパターニングし、形成する。これらの層の上に、電気絶縁層を形成し、犠牲層の表面領域が露出するようにパターニングする。該露出した領域を除去し、そうすることによって露出したパターン形成された導電層の表面領域を、導電性材料からなる構造によって覆う。  (もっと読む)

(もっと読む)

相互接続構造の製造方法

【課題】 従来のデュアル・ダマシンとULK IMD材料との統合が有する問題を解決するための相互接続構造を形成する方法を提供する。

【解決手段】 相互接続構造は、原子層堆積又は超臨界流体ベースのプロセスによって薄いコンフォーマルな不動態化誘電体及び/又は拡散障壁キャップ及び/又はハード・マスクを堆積させるステップを含む方法により製造される。

(もっと読む)

2,721 - 2,740 / 2,805

[ Back to top ]