Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

2,761 - 2,780 / 2,805

製造方法

【課題】 基板内に導電性構造体を形成する方法を提供すること。

【解決手段】 表面上に多段階層構造体を形成する方法が記載される。この方法は、表面上に硬化可能な液体層を堆積させるステップと、内部に多層パターンを有するスタンプを液体層に圧入し、該パターンによって定められる多段階層構造体を該液体層内に生成するステップと、液体層を硬化させ、内部に多段階層構造体を有する固体層を生成するステップとを含む。機械的位置合わせを用いて、構造体を形成することになる基板上に離間配置された複数の突出部及びスタンプのパターン内の相補的陥凹部を介して、基板に対するスタンプの光学的位置合わせを強化することができる。

(もっと読む)

導電性構成部品、貫通ビア及び導電性貫通ウェーハ・ビアを含む半導体構成部品を製造するためのプロセス及び集積化スキーム

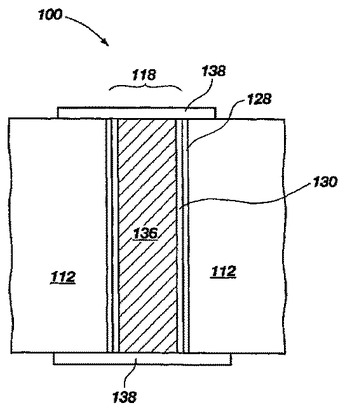

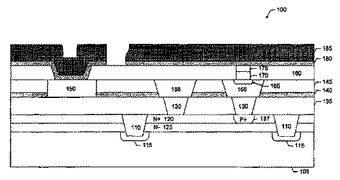

半導体構成部品に導電性ビアを形成するための方法が開示される。この方法は、第1の表面及び反対側の第2の表面を有する基板112を設けるステップを含む。この基板に、第1の表面と反対側の第2の表面の間に延びる少なくとも1つの穴118が形成される。基板のこの少なくとも1つの穴を画定している側壁にシード層128が形成され、導電層130でコーティングされ、この少なくとも1つの穴の内部の残りの空間に、導電性材料又は非導電性充てん材料136が導入される。基板を貫通した導電性ビアを、ブラインド・ホールを使用して形成する方法も開示される。本発明の導電性ビアを含む基板を有する半導体構成部品及び電子システムも開示される。  (もっと読む)

(もっと読む)

無電解堆積のエンドポイントを検出するための装置および方法

基板の表面に向けて電磁放射を方向付けて、該基板の該表面上の部材から反射された該電磁放射の強度の変化を1つ以上の波長で検出することによって無電解堆積プロセスをコントロールするための装置および方法。一実施形態において、該基板が検出機構に対して移動されると、無電解堆積プロセスステップの検出された終了が測定される。別の実施形態において、多数の検出ポイントが、該基板の該表面にわたる該堆積プロセスの状態を監視するために使用される。一実施形態において、該検出機構は該基板上で無電解堆積流体に浸される。一実施形態において、コントローラは、記憶されたプロセス値、異なる時間に収集されたデータの比較、および種々の算出された時間依存データを使用して無電解堆積プロセスを監視、記憶および/またはコントロールするために使用される。 (もっと読む)

集積接続部およびその製造方法

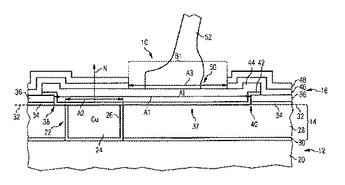

本発明は、電気的に導電性ではない絶縁層(34,36)における切り欠き部(37)に、少なくとも部分的または全体的に配置された外部導電構造部(44)を有する接続部に関する。切り欠き部(37)の底部には、導電性の内部導電構造部(22)が、絶縁層(34,36)の一方側に配置され、コンタクト領域において外部導電構造部と境界を形成している。コンタクト面は、切り欠き部(37)の他方側において、外部導電構造部(44)に配置されている。コンタクト領域とコンタクト面とは、互いに重ならないか、部分的にのみ重なっている。切り欠き部(37)の底部は、法線方向から見ると、コンタクト面の少なくとも半分または全面に重なるように配置されている。その結果、絶縁層(34、36)の段状部分は、コンタクト面と内部導電構造部(22)との間に延びる主要電流路の外側において、切り欠き部(37)の端部に位置する。  (もっと読む)

(もっと読む)

半導体装置、半導体装置の製造方法及びプラズマCVD用ガス

本発明は、420℃以下の熱履歴を経たフッ素添加カーボン膜からなる絶縁膜を備えた半導体装置に関する。本発明の特徴は、前記フッ素添加カーボン膜中の水素原子の含有量が、前記熱履歴を経る前において、3原子%以下であることにある。 (もっと読む)

金属−絶縁物−金属キャパシタおよび配線構造

【課題】 金属−絶縁物−金属キャパシタおよび配線構造を提供する。

【解決手段】 ダマシン工程を利用してMIMキャパシタおよび配線構造を含む半導体装置を製造する。前記MIMキャパシタおよび配線構造は静電容量を増やしつつ同じ深さで形成する。

(もっと読む)

溝配線を有する半導体装置および半導体装置の製造方法

【課題】 多層配線において、ショートやビア抵抗増加のような目合わせずれによる問題を回避し、信頼性の高い多層配線を得る。

【解決手段】 半導体装置は、第1配線層(201)と、層間絶縁層(202〜208)とを具備する。第1配線層(201)は、基板の上面側に設けられ、第1配線を含む。層間絶縁層(202〜208)は、前記第1配線層(201)上に設けられ、一方の端を前記第1配線に接続されたビアと、前記ビアの他方の端に接続された第2配線とを含む。前記層間絶縁層(202〜208)はシリコン酸化膜より低い比誘電率を有する。前記層間絶縁層(202〜208)の上部は、下側から順に、シリコン酸化膜(206)、シリコン窒化膜(207)、シリコン酸化膜(208)を備える。

(もっと読む)

チタン・タングステンのベース層および関連構造体を含む導電構造体を形成する方法

基板、基板上の導電パッド、および基板上の絶縁層を含む電子デバイスを形成する方法であって、上記絶縁層は導電パッドの一部を露出するバイアホールを有する。詳細には、絶縁層上であり導電パッドの露出部分上に導電構造体を形成できる。導電構造体は、チタン・タングステン(TiW)のベース層と、アルミニウムおよび/または銅のうちの少なくとも1つの導電層とを含みうる。さらに、導電構造体のベース層を、導電層と絶縁層との間に形成できる。関連デバイスについても説明する。

(もっと読む)

(もっと読む)

半導体基板上の、超臨界流体による物質の蒸着

集積回路デバイス製造のための半導体基板のような基板上への、超臨界流体を利用した物質の蒸着。蒸着は、基板表面に蒸着される物質の前駆体を含む、超臨界流体をベースとする組成物を使用して行われる。そのようなアプローチにより、気相蒸着工程に必要な揮発性および搬送性がないために、蒸着への適用には全く不適切であった前駆体の使用が可能になる。 (もっと読む)

集積回路におけるコンタクトサイズをサイジングすることによって多層コンタクトを製造するための方法

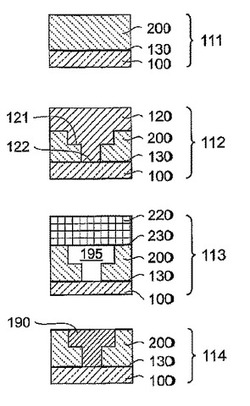

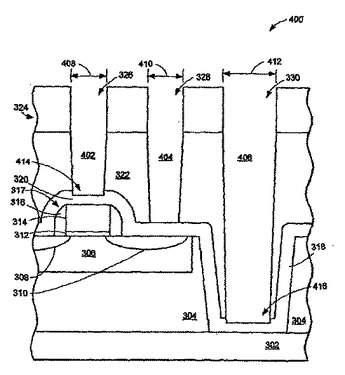

集積回路を形成するための方法(600)は、第1半導体基板(202)上の半導体デバイス(317)表面上の誘電材(322)における第1深さに第1開口部(228)、(338)、(402)をエッチングし、第1半導体基板(202)表面上の誘電材(322)において第2深さに第2開口部(230)、(340)、(404)をエッチングする。第1開口部(228)、(338)、(402)、及び第2開口部(230)、(340)、(404)は、エッチングラグに起因してほぼ同時に第1及び第2深さにエッチングするためにそれぞれ異なってサイズされる。第1開口部(228)、(338)、(402)、及び第2開口部(230)、(340)、(404)は、導電材で充填される。  (もっと読む)

(もっと読む)

多層配線構造の製造方法

【課題】高集積化、微細化されたパターンにおいて、ビアホール等を良好に埋め込み、かつ電気抵抗率の低い埋め込み型の多層配線構造を提供する。

【解決手段】埋め込み型の多層配線構造の製造方法が、絶縁層に孔部を形成する工程と、孔部の表面に、物理的真空堆積法で、平均膜厚が0.2nm以上で10nm以下である触媒層6、または触媒層の平均膜厚が、触媒層の材料原子の1原子層以上で10nm以下である触媒層6、を形成する工程と、触媒層を触媒に用いた無電解めっき法により、孔部の表面に無電解めっき層7を形成する工程と、無電解めっき層をシード層に用いた電解めっき法で、孔部を電解めっき層8で埋め込む工程とを含む。

(もっと読む)

ビア開口部中に形成されるポリマーメモリデバイス

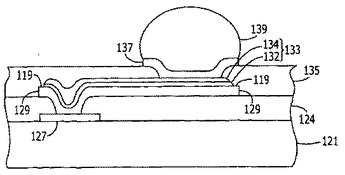

本発明は、ビア内にポリマーメモリデバイスを製造する方法に関する。この方法は、少なくとも1つの金属を含む層をその上に備える半導体基板を提供するステップと、この金属を含む層中に少なくとも1つの銅コンタクトを形成するステップと、銅コンタクト上に少なくとも1つの絶縁層を形成するステップと、絶縁層に少なくとも1つのビアを形成し、銅コンタクトの少なくとも一部を露出するステップと、ビアの下側部分にポリマー材料を形成するステップと、ビアの上側部分にトップ電極材料層を形成するステップとを含む。  (もっと読む)

(もっと読む)

デバイス内にバリア層を有するコンタクトホールを形成する方法及び得られるデバイス

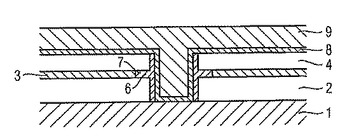

デバイスの下層(2)にコンタクトを形成する方法は、コンタクトホール(5)を形成するステップと、デバイスのコンタクトホール内にバリア材からなるコンタクトホールバリア層(7)を形成するステップと、コンタクトホールの底面のコンタクトホールバリア層をエッチングするステップと、コンタクトホール内にライナ材(8)を堆積するステップと、コンタクトホールに導電性材料(9)を充填するステップとを有する。半導体、受動素子、キャパシタ又はFeRAMなどのデバイスが上記方法に従って形成される。コンタクトホールの側壁にあるコンタクトホールバリア層(7)が、水素及び/又は酸素の側方拡散を抑制する。コンタクトホールバリア層は、ウェットエッチングプロセスによって生じる既存のバリア層(3)内のボイド(6)を充填するために上記プロセス後に、又は既存のバリア層への損傷を抑制するために上記プロセス前に行うことができる。

(もっと読む)

(もっと読む)

バリヤ金属上に直接銅めっきするマルチステップ電着法

本発明の実施形態は、基板表面に、通常はバリヤ層に銅シード層を堆積させる方法を教示している。その方法は、基板表面を銅溶液に入れるステップであって、該銅溶液が錯体形成銅イオンを含んでいる、前記ステップを含んでいる。電流又はバイアスを基板表面に印加し、錯体形成銅イオンを還元してバリヤ層に銅シード層を堆積させる。 (もっと読む)

電解加工装置及び電解加工方法

本発明は、被加工物の不良品化を招くと考えられるピットの発生を効果的に防止することができるようにした電解加工装置及び電解加工方法を提供する。この電解加工装置は、被加工物を加工する加工電極(210)と、被加工物に給電する給電電極(212)と、加工電極(210)と給電電極(212)との間に電圧を印加する電源(232)と、加工電極(210)及び給電電極(212)を内部に収納した耐圧容器(200)と、耐圧容器(210)内に高圧液体を供給する高圧液体供給系(204)を有する。  (もっと読む)

(もっと読む)

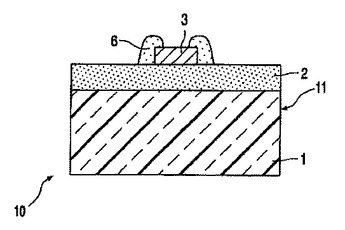

半導体デバイスを製造する方法およびその方法で使用するための装置

本発明は、基板(1)および少なくとも1つの半導体要素を含んだ半導体本体(11)を有した半導体デバイス(10)の製造方法に関する。その方法では、要素の形成後、少なくとも1つの電気的絶縁層(2)または電気的導体層(3)を含んだ層構造が形成され、開口部が、パターン形成されたフォトレジスト層(4)およびエッチング・プロセスの助けによって層構造中に形成され、残渣が、エッチング・プロセス中に半導体本体(11)の表面上に形成され、エッチング・プロセス後に、フォトレジスト層(4)が、酸素含有化合物を使用する処理によって灰にされ、その後、表面が、酸を水で希釈した溶液を含んだ洗浄剤を、室温より高い温度に加熱して使用する洗浄作業を受け、それによって形成された残渣が除去される。本発明によれば、硫酸が、洗浄剤用の酸として選択される。  (もっと読む)

(もっと読む)

ライン及びビア導体のための異なる材料を有するデュアル・ダマシン相互接続構造体

【課題】 ライン導体のために用いられるものと異なる、ビア又はスタッドのための材料を用いて、デュアル・ダマシン相互接続構造体を形成する方法を提供すること。

【解決手段】 ライン導体に用いられるものとは異なる、ビア又はスタッドのための材料を用いるか、又はトレンチ・ライナに用いられるものとは異なる、ビア・ライナのための材料を用いるか、或いは該トレンチ・ライナのものと異なるビア・ライナ厚を有する、デュアル・ダマシンのバックエンド・オブ・ライン(back−end−of−line:BEOL)相互接続構造体を形成する方法が開示される。改善された機械的強度のために、ビアに厚い超硬合金を用いる一方で、トレンチに薄い超硬合金だけを用い、抵抗を低くすることが好ましい。

(もっと読む)

銅メタライゼーションのためのALD窒化タンタルの集積

窒化タンタル/タンタルバリア層を堆積させるための方法および装置が、集積処理ツールでの使用のために提供される。遠隔発生プラズマによる洗浄ステップの後、窒化タンタルは原子層堆積法で堆積され、タンタルはPVDで堆積される。窒化タンタル/タンタルは、堆積された窒化タンタルの下の導電性材料を露呈するために、誘電体層の部材の底部から除去される。場合によって、さらなるタンタル層が、除去ステップの後に物理気相堆積法で堆積されてもよい。場合によって、窒化タンタル堆積およびタンタル堆積は同一の処理チャンバで生じてもよい。シード層が最後に堆積される。 (もっと読む)

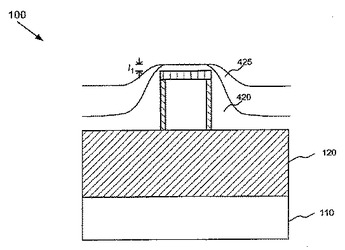

化学機械研磨プレーナ化のためのデュアルシリコンゲート層を有するFINFET

FinFETタイプの半導体デバイスは、フィン構造(210)を含んでいる。この上には、比較的薄いアモルファスシリコン層(420)を形成し、それから非ドープポリシリコン層(425)を形成する。この半導体デバイスは、アモルファスシリコン層(420)がフィン構造の損傷を防ぐ停止層として働く化学機械研磨(CMP)を使用してプレーナ化することができる。  (もっと読む)

(もっと読む)

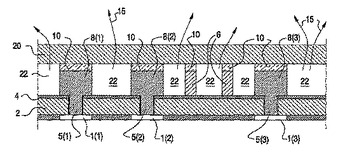

多孔質の誘電体層とエアギャップとを有する基板の製造方法、および基板

金属ライン(8(i))の間および誘電体内にエアギャップを形成する方法である。方法は、デュアルダマシン(dual damascene)構造を得ること、拡散バリア層(10)を、平坦化された面に直接加えること、およびリソグラフィステップを行なうことからなり、これにより、金属ラインを、拡散バリア層の下に遮蔽する。任意として、金属ライン(8(i))間の大きな誘電体領域(6)のいくつかの部分も、遮蔽される。露出した拡散バリア層部分および下にある誘電体がエッチングされる。典型的には150〜450℃の温度に加熱することにより、揮発性成分に分解することができる材料の層が加えられ、エッチングまたはCMPにより平坦化される。分解性生成物に対して透過性である誘電体層(20)が堆積され、その後、基板は加熱される。次いで、使い捨て層が分解し、透過性の誘電体層を通じて消滅し、その後に、金属ライン(8(i))および大きな誘電体領域の間に、エアギャップ(22)を残す。  (もっと読む)

(もっと読む)

2,761 - 2,780 / 2,805

[ Back to top ]