Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

281 - 300 / 2,805

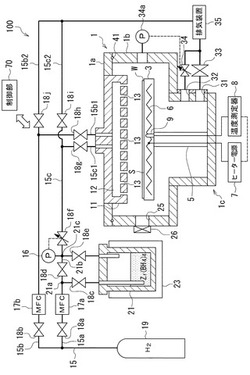

成膜方法、成膜装置及び半導体装置の製造方法

【課題】熱CVD法によって、M(BH4)4(Mは、Zr又はHfを意味する)を原料としてM/Zr比が適正範囲内で良質なMBx膜(Mは前記と同じ意味を有し、xは1.8〜2.5の数を意味する)を成膜する。

【解決手段】ガス供給源19から、ガス供給配管15aを介してH2ガスを原料容器21内に供給する。原料容器21内では、導入されたH2ガスとの接触によって、固体原料のZr(BH4)4が気化する。そして、成膜ガスとしてのH2ガスとZr(BH4)4ガスの混合ガスが、ガス供給配管15c,15c1、シャワーヘッド11のガス拡散空間12及びガス吐出孔13を介して処理容器1内に導入され、ウエハW上の絶縁膜の表面を覆うように、ZrBx膜の薄膜が形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】プローブ針の先端を研磨する時間を短縮することと接触抵抗を低く安定させること。

【解決手段】半導体基板上に形成された電子回路と、前記半導体基板上に形成され、前記電子回路と電気的に接続し、金属膜34と前記金属膜より硬い材料の層36とを備え、上視した場合前記層と前記金属膜とが配置された第1領域40と、前記金属膜が配置され前記層が形成されない第2領域42とを備えるパッド16と、を具備する半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の配線間の容量低減を実現するとともに、ミスアライメント・ビアを対策する。

【解決手段】配線上及び配線間のスペース領域に絶縁膜74を形成し、隣接配線間隔が狭い配線の上面を露出するスルーホールの周辺領域の絶縁膜74をリザーバーとして残して、周辺領域以外の絶縁膜74を除去し、絶縁膜74が除去された配線間のスペース領域に空隙を残しつつ、配線上に絶縁膜77を形成する。

(もっと読む)

グラフェン配線およびその製造方法

【課題】配線構造における電気特性の向上を図る。

【解決手段】グラフェン配線の製造方法は、絶縁膜13内に、配線溝30を形成し、前記配線溝内の全面に、触媒膜14を形成し、前記配線溝内の前記触媒膜上に、前記配線溝の底面に対して垂直方向に積層された複数のグラフェンシート16a〜16eで構成されるグラフェン層16を形成することを具備する。

(もっと読む)

半導体装置の製造方法

【課題】微細で良好な形状のコンタクトホールを有する半導体装置の製造方法を提供する。

【解決手段】絶縁膜36上にフォトレジスト膜42を形成する工程と、フォトレジスト膜42に開口部44を形成する工程と、開口部44が形成されたフォトレジスト膜42をマスクとして絶縁膜36をエッチングすることによりコンタクトホール48を形成する工程とを有し、コンタクトホール48を形成する工程は、開口部44が形成されたフォトレジスト膜42上に保護膜46を堆積しながら絶縁膜36をプラズマエッチングする第1の工程と、フォトレジスト膜42上に堆積された保護膜46を一旦除去する第2の工程と、保護膜46が一旦除去されたフォトレジスト膜42上に他の保護膜を新たに堆積しながら絶縁膜36を更にプラズマエッチングする第3の工程とを含んでいる。

(もっと読む)

装置

【課題】ボイドが存在しても高い信頼性を確保可能な配線構造を提案する。

【解決手段】実施形態に係わる装置は、第1の溝10を有する絶縁層13と、第1の溝10内に形成され、上部に凹部16を有する銅を含む第1の配線層15と、第1の配線層15の凹部16の内面上に形成され、少なくとも1つのグラフェンシートから構成されるグラフェン層17とを備える。

(もっと読む)

グラフェン配線およびその製造方法

【課題】配線構造における電気特性の向上を図る。

【解決手段】グラフェン配線は、配線溝を有する絶縁膜13と、前記配線溝内の両側面の前記絶縁膜上に形成された第1触媒膜15と、前記配線溝内の両側面の前記第1触媒膜上に形成され、両側面に対して垂直方向に積層された複数のグラフェンシートで構成された第1グラフェン層16と、を具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】薄型化及び小型化を図る半導体装置を提供する。

【解決手段】半導体装置1は、半導体チップ10と、半導体チップ10の上に積層された多層配線構造30と、多層配線構造30内に埋設された電子部品60,80と、を備える。半導体チップは、半導体基板11と、半導体基板上に形成された内部配線20と、内部配線を被覆するようにして半導体基板上に形成された封止層16と、を有し、多層配線構造が封止層上に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】バリアメタル層の金属配線に対する密着性を向上させつつ、金属配線の低抵抗化を図った半導体装置の製造方法を提供する。

【解決手段】層間絶縁膜15に形成された凹部16、17内にバリアメタル層20を形成した後、凹部16、17内にCu配線層23を形成する。バリアメタル層20の形成工程は、凹部16、17内にTi含有量が50原子%を超える第1のTiNx膜18を形成した後、側壁部上と比較して底部上に相対的に多く形成されるように、Ti含有量が第1のTiNx膜18より多い第2のTiNx膜(またはTi膜)19を形成する。

(もっと読む)

成膜方法及び成膜装置

【課題】 ボイド等の発生を防止できるように凹部内に金属膜の成膜を施すことができる成膜方法である。

【解決手段】 処理容器22内でプラズマにより金属のターゲット76から金属イオンを発生させてバイアスにより引き込んで凹部4が形成されている被処理体に金属の薄膜を堆積させる成膜方法において、ターゲットから金属イオンを生成し、その金属イオンをバイアスにより引き込んで凹部内に下地膜90を形成する下地膜形成工程と、金属イオンを発生させない状態でバイアスにより希ガスをイオン化させると共に発生したイオンを引き込んで下地膜をエッチングするエッチング工程と、ターゲットをプラズマスパッタリングして金属イオンを生成し、その金属イオンをバイアス電力により引き込んで金属膜よりなる本膜92を堆積しつつ、その本膜を加熱リフローさせる成膜リフロー工程とを有する。

(もっと読む)

半導体ウェハおよびそれにより形成した半導体装置

【課題】半導体ウェハの保護層に形成された溝のアスペクト比が0.5以上である場合においても、再配線を形成する際のレジスト膜に破壊が生じることを防止する手段を提供する。

【解決手段】半導体ウェハが、集積回路を形成した複数の能動領域と、隣合う能動領域間に設けられたダイシング領域と、能動領域とダイシング領域とを覆う保護層5と、保護層の能動領域の外側を掘込んで形成されたガイド溝21と、能動領域の保護層上を覆う保護膜7と、保護膜上に形成され、集積回路に電気的に接続する第2の配線9とを備え、ガイド溝のアスペクト比が0.5以上の場合にそのガイド溝を保護膜で覆う。

(もっと読む)

配線形成方法

【課題】下層配線層と配線シード層との密着性を低下させないで高く維持することが可能な配線形成方法を提供する。

【解決手段】下層配線層4と絶縁性バリヤ層6と層間絶縁膜8と上層配線層が順次積層された被処理体に対して上層配線層と、連通配線層16とを形成する配線形成方法において、絶縁性バリヤ層を残した状態で連通ホール9Bを形成し、連通ホール内に犠牲膜を埋め込み、トレンチ9Aを形成するパターンマスク62を形成する前処理工程と、トレンチを形成するトレンチ形成工程と、犠牲膜60とパターンマスクとをアッシングするアッシング工程と、トレンチ内と連通ホール内に熱処理によりバリヤ層10を形成するバリヤ層形成工程と、異方性エッチングにより連通ホールの底部のバリヤ層と絶縁性バリヤ層とを除去する異方性エッチング工程と、配線シード層12を形成する配線シード層形成工程とを有する。

(もっと読む)

半導体装置

【課題】抵抗値の温度依存性の小さい抵抗素子を有する半導体装置を提供する。

【解決手段】半導体装置は、金属抵抗素子層Rm1,Rm2を有する。金属抵抗素子層Rm1は、金属抵抗膜層Rm11を含む。金属抵抗素子層Rm2は、金属抵抗膜層Rm12を含む。金属抵抗膜層Rm11は、窒化チタン抵抗および窒化タンタル抵抗のうちの一方であり、金属抵抗膜層Rm12は、窒化チタン抵抗および窒化タンタル抵抗のうちの他方である。窒化チタン抵抗の抵抗値は正の温度係数を有する一方、窒化タンタル抵抗の抵抗値は負の温度係数を有する。コンタクトプラグCP2によって、金属抵抗膜層Rm11と金属抵抗膜層Rm12とが電気的に接続されるので、窒化チタン抵抗の温度係数と窒化タンタル抵抗との温度係数が相殺される。これにより温度係数を小さくすることができる。

(もっと読む)

半導体ウエハ装置およびその製造方法

【課題】 所望の配線構造を形成することができ、かつウエハ有効領域の欠陥率の増加を防止することのできる半導体ウエハ装置の製造方法を提供する。

【解決手段】 半導体ウエハ装置の製造方法は、(a)回路領域に半導体素子を形成した半導体ウエハ上に半導体素子に接続された下層配線パターンを形成する工程と、(b)下層配線パターンを覆って半導体ウエハ上に層間絶縁膜を形成する工程と、(c)回路領域上で下層配線パターンに接続されたビア導電体とその上に配置された配線パターンとを、回路領域外の周辺領域上で配線パターンに対応する導電体パターンを、層間絶縁膜に埋め込んで形成する工程とを含む。導電体パターンは電気的に分離された状態で形成される。

(もっと読む)

半導体装置の製造方法

【課題】めっき工程の埋設不良を抑制する。

【解決手段】半導体基板100上に設けられた層間絶縁膜320に開口部を形成する工程と、開口部上面にバリア層340を形成するバリア層形成工程と、バリア層340上に配線シード層を形成する配線シード層形成工程を有する。また、バリア層形成工程は、選択成膜工程と、スパッタエッチング工程を有する。バリア層340の選択成膜工程は、バリア層340を、開口部の平面部342のみに選択的に成膜する。次いで、バリア層340のスパッタエッチング工程は、平面部342のバリア層340をスパッタエッチングしながらバリア層340のスパッタ粒子を開口部の側壁部344に堆積させる。

(もっと読む)

半導体装置の製造方法

【課題】容量コンタクトパッドと容量コンタクトプラグが一体となった構造を形成する。これにより、従来は2回、必要だったフォトリソグラフィ工程を1回に削減して、製造コストを低減する。

【解決手段】半導体装置の製造方法では、層間絶縁膜上に、開口を有するマスクパターンを形成する。このマスクパターンを用いて、層間絶縁膜をエッチングすることにより、開口の下の層間絶縁膜内に容量コンタクトホールを形成する。湿式エッチングにより、マスクパターン内の開口を大きくした後、開口内に導電材料を埋め込むことにより、それぞれ容量コンタクトプラグ及び容量コンタクトパッドを形成する。この後、容量コンタクトパッド上にキャパシタを形成する。

(もっと読む)

半導体装置の製造方法

【課題】フォトリソグラフィ工程を行う際に、光が乱反射することを抑制することができる半導体装置の製造方法を提供する。

【解決手段】基板1上に下層配線構成膜2aを形成し、当該下層配線構成膜2aをパターニングして下層配線2を形成する工程と、基板1に下層配線2を覆う層間絶縁膜4を形成し、層間絶縁膜4にビアホールを形成する工程と、スパッタ法により層間絶縁膜4上に第1上層配線構成膜7aを形成する工程と、第1上層配線構成膜7aを形成する工程の温度より高い温度で、第1上層配線構成膜7aをリフローする工程と、リフローする工程より低い温度のスパッタ法により第1上層配線構成膜7a上に第2上層配線構成膜8aを形成する工程と、第2上層配線構成膜8a上に反射防止膜9を成膜する工程と、反射防止膜9上にレジストを形成する工程と、を含む工程を行う。

(もっと読む)

半導体装置の製造方法

【課題】メタルゲートプロセスにおけるプリメタル層間絶縁膜の平坦性を向上できるようにする。

【解決手段】まず、半導体基板1の上に、ゲート絶縁膜3を介在させてゲート電極4を形成する。その後、半導体基板1にゲート電極4をマスクとしてソース・ドレイン領域を形成する。続いて、ゲート電極4を覆うように半導体基板1上の全面に第1の酸化シリコン膜10を形成する。その後、ゲート電極4をストップ膜とするCMP法により、第1の酸化シリコン膜10を平坦化する。続いて、ゲート電極4を含む第1の酸化シリコン膜10の上に、第2の酸化シリコン膜11を形成する。その後、ゲート電極4をストップ膜とするCMP法により、第2の酸化シリコン膜10を平坦化する。さらに、ゲート電極4を含む第2の酸化シリコン膜10の上に、第3の酸化シリコン膜12を形成する。

(もっと読む)

配線の形成方法及びその配線を有する表示装置の形成方法

【課題】従来のCMPを伴うダマシン法を用いた配線や電極の形成は、製造工程が煩雑であり高コスト化している。表示装置等の大型基板に配線形成を行うには平坦性等の高精度が要求されて好適せず、また研磨による配線材料の除去・廃棄量が多いという課題がある。

【解決手段】配線の形成方法及び配線を有する表示装置の形成方法は、基板上若しくは回路素子上に設けられた第1の金属拡散防止膜上に、金属シード層をCVD法により形成し、フォトレジストマスクを用いて選択的に無電解メッキ法、又は電解メッキ法により、金属配線層を形成し、金属シード層及び第1の金属拡散防止膜の不要領域除去と、金属シード層及び金属配線層及び第1の金属拡散防止膜の側面を含む表面を覆うように無電解メッキ法による第2の金属拡散防止膜の選択的な形成とにより配線及び電極を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリセル領域の周辺に金属電極を有するアンチフューズを製造歩留り良く形成する。

【解決手段】MOSトランジスタを備えたメモリセルを有するメモリセル領域と、アンチフューズを備えた周辺回路領域とを有する半導体装置において、メモリセルを構成するコンタクトプラグ又はビット配線と同層に形成される周辺回路のコンタクトプラグ又は配線を用いて、アンチフューズの電極を形成する。

(もっと読む)

281 - 300 / 2,805

[ Back to top ]