Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

801 - 820 / 2,805

電子装置、電子装置の製造方法、電子機器

【課題】端子間の接合性に優れ高い信頼性を備えたものにするとともに、端子の狭ピッチ化も容易に対応できる電子装置、電子装置の製造方法、電子機器を提供する。

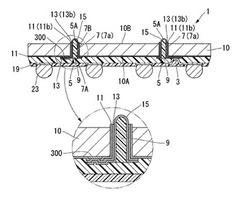

【解決手段】本発明の半導体装置1は、半導体基板10と、半導体基板10に形成された貫通孔7内に設けられるとともに半導体基板10の能動面10A側に部分的に突出する貫通電極5と、を有し、貫通電極5は、樹脂コア9と、樹脂コア9の少なくとも一部を覆う導電膜15と、を有する。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】多層配線構造の半導体装置のパッケージ工程や環境試験において、膜剥れが起き難い技術を提供する。

【解決手段】絶縁層中に配線層が構成された下層配線層、前記下層配線層上に設けられた層間絶縁層、前記層間絶縁層の上に設けられた絶縁層中に配線層が構成された上層配線層、及び前記層間絶縁層に構成された前記下層配線層の配線層と前記上層配線層の配線層とを電気的に接続する為の接続層とを具備する半導体装置において、

前記層間絶縁層A7に、該層間絶縁層A7の上層および/または下層に繋がる埋設層A15が構成され、前記埋設層A15および接続層A12を有する層間絶縁層A7の平均弾性率が10GPa以上であるよう構成されてなる半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】能動素子、受動素子等の損傷や特性変化を防止しつつ、より小型化が図れる半導体装置を提供する。

【解決手段】複数の層2〜4が積層された半導体装置において、最上部に位置する第1配線層59と、最上部から下方の2番目に位置する第2配線層54と、第1配線層59と第2配線層54の間に形成された金属膜56と、金属層56の外周に形成され、第1配線層59と第2配線層54を接続する第1導電性プラグ58と、金属膜56及び第1配線層59の上方に形成されたパッド62と、パッド62と第1配線59を接続する第2導電性プラグ61とを有する。

(もっと読む)

半導体装置

【課題】ゲート電極の抵抗を低減しつつ、寄生容量やチップ面積の増大を抑制して、高周波特性を向上できる半導体装置を提供する。

【解決手段】実施形態の半導体装置は、ソース拡散層110とドレイン拡散層120とゲート電極100とにより構成された単位電界効果トランジスタを電気的に並列接続したマルチフィンガー構造の電界効果トランジスタと、この電界効果トランジスタの上部に電気的に接続した多層配線構造とを備え、ソース拡散層110の第2の配線(M1配線150)およびドレイン拡散層120の第3の配線(M1配線150)より上層にゲート電極100の第1の配線(M2配線160)を設けるものである。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の小型化が進んでも半導体装置の信頼性向上を図ることができる技術を提供する。

【解決手段】本発明の技術的思想は、積層形成される窒化シリコン膜SN1〜SN3のそれぞれの膜厚を一定値ではなく、トータルの総膜厚を一定に保ちながら、上層の窒化シリコン膜SN3から下層の窒化シリコン膜SN1にしたがって膜厚を薄くするように構成している点にある。これにより、歪シリコン技術を実効あらしめる窒化シリコン膜SN1〜SN3の引張応力を確保しながら、特に、最上層の窒化シリコン膜SN3の埋め込み特性を改善できる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置における基板貫通電極の形成において、貫通電極形成用穴内部にバリア層やめっきのためのシード層を成膜する際、貫通電極穴内部の成膜レートと、基板平面部の成膜レートが大きく異なるために、貫通電極形成用穴内部で所定の膜厚を得ようとすると、基板平面部には必要以上の厚みをもった膜が形成されてしまう。結果として、後工程でのウエットエッチングによる配線パターニングの際に、基板横方向へのエッチング液の入り込みによる大幅な寸法シフトが発生し、微細化の妨げとなっている。

【解決手段】貫通電極形成用穴の開口部を除く基板平面部にフォトレジストを形成してから成膜を行い、成膜後にフォトレジスト表面に付着した膜と共にフォトレジストを除去することで、貫通電極形成用穴内部に付着した薄膜は残したまま基板平面部を露出され、改めて基板平面部に必要分だけ成膜を行うことで課題を解決する。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】半導体集積回路装置の集積度の向上を図ることのできる技術を提供する。

【解決手段】セルの高さ方向に隣接して配置されるセルrow上段の2入力NAND回路6とセルrow下段のインバータ回路1との間の結線に、2層目以上の配線を用いずに、1層目の配線M1よりも下層に位置し、2入力NAND回路6またはインバータ回路1を構成するMISFETのゲート電極7N2,7P2と一体化した導電体膜からなる配線8を用いる。

(もっと読む)

半導体素子及びその製造方法

【課題】本発明は、半導体素子及びその製造方法を開示する。

【解決手段】本発明は、コア/周辺回路領域でトランジスタの接合領域とメタルラインを、ビットラインを利用して連結せずメタルプラグを利用して連結することにより、コア/周辺回路領域に形成されるビットライン等もセル領域と同様に均一な形態のパターンを有することができるようにする。これを介し、本発明ではコア/周辺回路領域におけるビットラインパターニングの不良を防止し、ビットライン形成時にSPT(Spacer Pattern Technology)を適用することができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線層に新たな機能を有する素子を設けた半導体装置を提供する。

【解決手段】半導体基板上に形成された第1配線層150、及び半導体素子200を備える。第1配線層150は、絶縁層156と、絶縁層156の表面に埋め込まれた第1配線154とを備える。半導体素子200は、半導体層220、ゲート絶縁膜160、及びゲート電極210を備える。半導体層220は、第1配線層150上に位置する。ゲート絶縁膜160は、半導体層220の上又は下に位置する。ゲート電極210は、ゲート絶縁膜160を介して半導体層220の反対側に位置する。

(もっと読む)

半導体装置及びその製造方法

【課題】Q値の高いモノリシックインダクタ素子を備える半導体装置及びその製造方法を提供する。

【解決手段】半導体装置50は、半導体基板1と、半導体基板1上に設けられた層間絶縁膜6と、層間絶縁膜6の上部に埋め込むように設けられ、スパイラルパターンを有する第1インダクタ配線層7と、層間絶縁膜6上及び第1インダクタ配線層7上を覆うように設けられ、第1インダクタ配線層7に沿って延びる少なくとも一つの溝状接続孔10を有するバリア絶縁膜9と、バリア絶縁膜10上に、第1インダクタ配線層7に沿って延びるように形成されると共に、溝状接続孔10を埋め込んで第1インダクタ配線層7に電気的に接続された第2インダクタ配線層11とを備える。第2インダクタ配線層11は、その長さ方向に延びるように上面側に設けられた少なくとも一つの溝状凹部12を有する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】エアギャップ部を有し、かつ、高い機械的強度を有する半導体装置およびその製造方法を提供する。

【解決手段】酸素を含有する層間絶縁膜IL1の複数の溝部の側壁を被覆するバリア金属層ALが形成される。複数の溝部を充填するように配線金属層PCが形成される。層間絶縁膜IL1の酸素を熱拡散させることによってバリア金属層ALの少なくとも一部を酸化することで、酸化物バリア層BL1が形成される。配線金属層のうち複数の溝部の外側の部分を除去することによって、第1および第2の配線間領域IW1,IW2と第1〜第3の配線WR1〜WR3とが形成される。第1の配線間領域IW1を覆い、かつ第2の配線間領域IW2上に開口部OPを有するライナー膜LN1が形成される。開口部OPを介したエッチングが行なわれる。

(もっと読む)

半導体装置およびその製造方法

【課題】ボラジン系化合物の絶縁膜を用いて、絶縁材料と配線材料との間の密着性や、機械強度等の特性が向上された半導体装置およびその製造方法を提供する。

【解決手段】凹部に第1の導体層が埋め込まれた第1の絶縁層と、第1の絶縁層上に形成されたエッチングストッパー層と、エッチングストッパー層上に形成された第2の絶縁層と、第2の絶縁層上に形成された第3の絶縁層と、第2の絶縁層と第3の絶縁層との凹部に埋め込まれた第2の導体層と、を含む半導体装置であって、第2の絶縁層および第3の絶縁層は、炭素含有ボラジン化合物を原料として化学的気相反応成長法によって形成され、第3の絶縁層の炭素含有率が、第2の絶縁層の炭素含有率よりも小さく、第2の導体層の外周に、金属材料で構成された導体拡散防止層が形成されている半導体装置である。

(もっと読む)

配線構造

【課題】断線が発生することを抑制可能な配線構造を提供する。

【解決手段】始めに、半導体装置の表面にアルミニウム金属膜5を形成する。次に半導体装置の表面に窒化チタン膜6を形成する。そして最後に半導体装置の表面にアルミニウム金属膜7を形成する。すなわち、シリコン基板1と電極4とを接続する電気配線を金属膜の3層構造により段階的に形成する。これにより、シリコン基板1と絶縁膜2との間に形成される段差の底部部分において金属膜の被覆率が低くなることによって断線が生じることを防止できる。

(もっと読む)

半導体装置およびその製造方法

【課題】MIM構造のキャパシタを含む半導体装置において、安定した容量値を与える。

【解決手段】半導体装置100は、基板(不図示)上に形成された絶縁膜154、同層に形成されるとともに、絶縁膜154を介して対向配置された第1の電極および第2の電極、を有するMIMキャパシタ200とを含む。第1の電極および第2の電極は、それぞれ、基板の積層方向において、他の領域300に形成されたビア130および当該ビア上に当該ビアに接続して設けられた配線132が形成された層にわたって延在する第1の高アスペクトビア110および第2の高アスペクトビア120により構成される。

(もっと読む)

表示装置用Al合金膜、表示装置およびスパッタリングターゲット

【課題】バリアメタル層を省略して透明画素電極と直接接続させた場合にも低コンタクト抵抗を十分かつ確実に示す表示装置用Al合金膜を提供する。

【解決手段】表示装置の基板上で、透明導電膜と直接接続されるAl合金膜であって、該Al合金膜は、Geを0.05〜1.0原子%、Ni、Ag、CoおよびZnよりなる群から選択される少なくとも1種を0.03〜2.0原子%、および希土類元素群から選ばれる少なくとも1種の元素を0.05〜0.5原子%含有し、かつ、前記Al合金膜中に、長径20nm以上のGe含有析出物が100μm2当たり50個以上存在することを特徴とする表示装置用Al合金膜。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】エッチングストッパ膜を有し、配線間容量の増大を抑制可能な半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体基板11と、半導体基板11の表面上部に配設された層間絶縁膜29と、層間絶縁膜29に埋め込まれ、半導体基板11に対向する上面が層間絶縁膜29の上面と面一に配設され、互いに離間して配置された複数のビアプラグ31と、層間絶縁膜29及びビアプラグ31の表面上部に配設された層間絶縁膜39と、層間絶縁膜39によって分離され、ビアプラグ31と接続され、ビアプラグ31に対向する上面が層間絶縁膜39の上面と面一に配設され、層間絶縁膜39を挟んで相対向する側面に、層間絶縁膜29の側から順に、層間絶縁膜29とはエッチング性が異なり且つ層間絶縁膜39より比誘電率の高い側壁絶縁膜35、及び側壁絶縁膜35とはエッチング性が異なる側壁絶縁膜37を有する複数の第2配線33とを備える。

(もっと読む)

半導体装置の製造方法

【課題】デュアルダマシン法による解像限界以下の溝(トレンチ)及び凹部(孔又はビア)のパターンをCD値を高精度に形成することができる半導体装置の製造方法を提供する。

【解決手段】被エッチング層上に、第1のハードマスク膜と、第2のハードマスク膜とを成膜する成膜工程S11と、第1のピッチを有し、第2のハードマスク膜よりなるパターンであって、溝のパターンを形成する際のエッチングマスクとなる溝形成用マスクパターンを形成するための第1の溝形成用マスクパターン形成工程S12〜S14と、第4のピッチで設けられた開口部を有する第2のレジスト膜と、第2のレジスト膜の開口部と連通し、第2のレジスト膜の開口部の寸法より小さい寸法の開口部を有する第1の有機膜とよりなる第2レジストパターンを用いて、第1のハードマスク膜をエッチングする第1の凹部形成用マスクパターン形成工程S15〜S18とを有することを特徴とする。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】本発明は、しきい値電圧のばらつきが大きいトランジスタのしきい値電圧を調整してしきい値電圧のばらつきを低減することを可能にする。

【解決手段】基板11と絶縁層12とシリコン層13が積層されてなるSOI基板10の該シリコン層13の表面側にトランジスタ20を形成する工程と、SOI基板10上に、トランジスタ20を被覆する第1絶縁膜30と、トランジスタ20に電気的に接続される配線部40とを形成する工程と、配線部40を通じてトランジスタ20のしきい値電圧を測定する工程と、第1絶縁膜30表面に第2絶縁膜を介して支持基板を形成する工程と、SOI基板10の裏面側の基板11と絶縁層12の少なくとも一部を除去する工程と、測定されたしきい値電圧に基づいてトランジスタ20のしきい値電圧を調整する工程を有する。

(もっと読む)

半導体装置

【課題】製造ばらつきに関わらず、切断箇所を制御できる構成の電気ヒューズを得る。

【解決手段】半導体装置は、基板(不図示)に形成された電気ヒューズ100を含む。電気ヒューズ100は、一端側に設けられた第1の配線112と、第1の配線112とは異なる層に形成された第2の配線122と、第1の配線112と第2の配線122と接触してこれらを接続する第1のビア130と、他端側に設けられ、第1の配線112と同層に第1の配線112から離間して形成された第3の配線142と、第3の配線142と第2の配線122と接触してこれらを接続し、第1のビア130よりも抵抗が低くなるよう構成された第2のビア132と、を含み、切断時に電気ヒューズ100を構成する導電体が外方に流出してなる流出部が形成されて切断される。

(もっと読む)

配線構造及びその形成方法、並びに半導体装置

【課題】炭素元素からなる線状構造体を有する接続部の更なる低抵抗化を実現して、更なる接続部の微細化を可能とする。

【解決手段】ビア孔28a内を充填し、配線溝32aの内壁面を覆うように、例えば超臨界CVD法により、ビア孔28a内におけるCNT28d間の空隙及びCNT28dの中空内を導電材料34で埋め込み、ビアプラグ33と、ビアプラグ33上で配線溝32aの内壁面を覆う下地膜32bとを同時形成する。

(もっと読む)

801 - 820 / 2,805

[ Back to top ]