Fターム[5F033NN29]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールの形状 (1,366)

Fターム[5F033NN29]の下位に属するFターム

断面が長方形以外 (728)

コンタクトホールの平面形状 (560)

Fターム[5F033NN29]に分類される特許

1 - 20 / 78

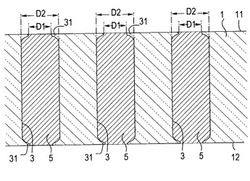

縦導体充填構造

【課題】ウエハ等の基板に設けられた縦孔内に、脱落、抜け等を生じることなく、完全充填された縦導体充填構造を提供すること。

【解決手段】基板1の厚み方向に設けられた縦孔3内に縦導体5を充填した縦導体充填構造であって、孔開口端が内側に突出する凸縁31となっており、凸縁31−31間で見た孔径D1が、孔内壁面3−3間で見た内径D2よりも小さい。

(もっと読む)

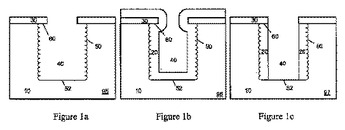

半導体装置及び半導体装置の製造方法

【課題】新規な構造のコンタクトプラグを有する半導体装置を提供する。

【解決手段】

半導体装置は、半導体基板と、半導体基板に形成され、ソース/ドレイン領域及びゲート電極を有するトランジスタと、トランジスタのソース/ドレイン領域及びゲート電極を覆う絶縁膜と、絶縁膜中に形成され、トランジスタのソース/ドレイン領域またはゲート電極に接されるコンタクトプラグとを有し、コンタクトプラグは、絶縁膜の厚さ方向に延在しトランジスタのソース/ドレイン領域またはゲート電極に接触する柱部と、柱部の上部から絶縁膜の表面と平行な方向に張り出し上面が平坦化された鍔部とを有する。

(もっと読む)

貫通電極を備えた配線基板とその製造方法

【課題】深孔相互間の距離を狭くする事ができ、深孔を微細化しても周囲の配線基板から及ぼされる応力の増加が防止でき、信頼性が保たれ、プロセス全体を低コストできる配線基板とその製造方法を提供する。

【解決手段】基体の主表面からその反対側裏面の両面に貫通する複数の貫通孔を備え、それらの孔が実質的に金属で埋められて貫通電極とされており、それらの内の少なくとも2以上の電極が電気的に並列に接続されている配線基板の製造方法であって、それらの2以上の孔を形成する場合に、それらの2以上の孔を含む領域より大きいサイズのマスクパターンを利用してそれらの2以上の孔を陽極酸化法を含む自己組織的穴明けプロセスにより所定の深さ以上の孔を形成した後に裏面から基体を削って、孔を裏面に露出させて貫通孔とする事を特徴とする配線基板の製造方法。

(もっと読む)

半導体装置及びその作製方法

【課題】多層配線を形成する際における配線の加工に要する工程を簡便にすることを課題

とする。また、開口径の比較的大きいコンタクトホールに液滴吐出技術やナノインプリン

ト技術を用いた場合、開口の形状に沿った配線となり、開口の部分は他の箇所より凹む形

状となりやすかった。

【解決手段】高強度、且つ、繰り返し周波数の高いパルスのレーザ光を透光性を有する絶

縁膜に照射して貫通した開口を形成する。大きな接触面積を有する1つの開口を形成する

のではなく、微小な接触面積を有する開口を複数設け、部分的な凹みを低減して配線の太

さを均一にし、且つ、接触抵抗も確保する。

(もっと読む)

表示装置及びマスク

【課題】マスクの枚数を増やすことなく、ストレージキャパシタの電極間から半導体パターンを除去して高画質化を実現させる表示装置及びその製造方法を提供する。

【解決手段】本発明によるTFTパネルの製造では、半導体パターンとTFTのドレイン電極とを、同じマスクを利用したエッチングで同時にパターニングする。一方、画素電極の直下に形成される絶縁膜のパターニングには別のマスクを利用する。ドレイン電極を覆う絶縁膜の領域では、中央部の全体を感光させ、周辺部を半分の厚みまで感光させる。ストレージ電極の上方を覆う絶縁膜の領域は薄い一部を残して感光させる。ドレイン電極を覆う誘電膜をエッチングしてドレイン電極を露出させるとき、絶縁膜のその薄い一部がその下地の誘電膜を保護する。その後、絶縁膜のその薄い一部を画素電極の一部に置換し、保護された誘電膜を隔ててストレージ電極と対向させる。

(もっと読む)

ヴィア構造およびその作製方法

【課題】より小さな径の基板貫通ヴィアが形成できるようにする。

【解決手段】基板101の回路が形成されている主表面101a側から所望の孔径の範囲で形成可能な深さに形成された第1孔部102と、基板101の裏面側から形成されて第1孔部102に接続する第2孔部103と、第1孔部102の内部に形成された第1孔部配線104と、第1孔部配線104に接続して基板101の主表面101a側に形成された表面配線層105と、第2孔部103の内部に第1孔部配線104に接続して形成された第2孔部配線106と、第2孔部配線106に接続して基板101の裏面側に形成された裏面配線層107とを備える。

(もっと読む)

貫通配線基板の製造方法

【課題】貫通配線基板の両面に実装するデバイスの電極配置が多様で且つ高密度である小型のデバイスであっても、実装するデバイス間の電極を自由度高く電気的に接続することが可能な貫通配線基板及びその製造方法の提供。

【解決手段】第1面1と第2面2とを有する基板と;第1面及び第2面の間を貫通する貫通孔内に、導電性物質を充填又は成膜して形成された複数の貫通配線12a,12bと;を備え、貫通配線同士は、互いに離間し、且つ基板の平面視において、重なり部分を少なくとも1つ備え、基板の第1面側又は第2面側からレーザー照射して、貫通孔を形成する領域を改質する工程Aと;前記改質された領域を除去して、貫通孔を形成する工程Bと;を含み、工程Aにおいて、複数の貫通孔形成領域のうち、レーザーの入射面から遠い方の重なり部分をレーザー照射した後に、レーザーの入射面から近い方の重なり部分をレーザー照射する貫通配線基板の製造方法。

(もっと読む)

配線基板の製造方法

【課題】コンタクトホールを、生産性良く、低コストで、且つ信頼性良く製造する配線基板の製造方法を提供する。

【解決手段】基板1に第1電極3及び第2電極7が形成される。第1電極3及び第2電極7を連通するように形成された微細穴の側壁部及び底部に、導電膜9を形成してコンタクトホール2を形成する。この配線基板100の製造する際に、微細穴を形成する微細穴形成工程において、微細穴の側壁部の開口端側に相対的に浅い溝からなる第1溝領域4が形成され、微細穴の側壁部の底部側に相対的に深い溝からなる第2溝領域5が形成される。このように区分けした溝領域4,5のうち、第2溝領域5に導電性材料を含有する液体を付与して、導電膜9を形成する。

(もっと読む)

半導体装置

【課題】半導体装置の性能を向上させる。また、半導体装置の信頼性を確保する。また、半導体装置のチップサイズの縮小を図る。特に、SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を損なわずにゲート電極の下部のウエルの電位を制御し、寄生容量の発生を防ぐ。また、MOSFETにおける欠陥の発生を防ぐ。

【解決手段】ゲート電極配線3に形成された孔部27内を通るウエルコンタクトプラグ8により、ゲート電極2の下部のウエルの電位を制御することで寄生容量の発生を防ぐ。また、ゲート電極2に沿って素子分離領域4を延在させることで、ゲッタリング効果によりゲート絶縁膜における欠陥の発生を防ぐ。

(もっと読む)

半導体装置及びその製造方法

【課題】シェアードコンタクトを備えた半導体装置において、コンタクトホールの開口不良やコンタクト抵抗の増大を防止しつつ、接合リーク電流の発生に起因する歩留まりの低下を防止する。

【解決手段】半導体基板100におけるゲート電極103の両側にソース/ドレイン領域106が形成されている。シェアードコンタクトは、ソース/ドレイン領域106とは接続し且つゲート電極103とは接続しない下層コンタクト113と、下層コンタクト113及びゲート電極103の双方に接続する上層コンタクト118とを有する。

(もっと読む)

電極構造体及びその製造方法、並びに半導体装置

【課題】精度良く形成された小型化された電極を備えた電極構造体及びその製造方法、並びに半導体装置を提供する。

【解決手段】第1の層間絶縁膜13に、第1の方向に延在する複数の第1の溝16を形成し、第1の溝16の対向する2つの側面及び底面を覆うように第1の導電膜32を形成し、第1の導電膜32が形成された複数の第1の溝16を第1の絶縁膜19で充填し、第1の層間絶縁膜13、第1の絶縁膜19、及び第1の導電膜32の上面に、第2の方向に延在する複数の開口部を有したハードマスク層33を形成し、異方性エッチング法により、複数の開口部から露出された部分の第1の絶縁膜19及び第1の導電膜32を除去することで、第1の溝16に第1の導電膜32よりなる電極を形成すると共に、第1の層間絶縁膜13に第1の溝16と交差する第2の溝17を複数形成し、ハードマスク層33を除去した後、第2の溝17を第2の絶縁膜21で充填する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の微細化に対処しうる、製造が容易で安価な低コンタクト抵抗の半導体装置およびその製造方法を得る。

【解決手段】Si基板(1)上の不純物領域(7)を覆うように層間絶縁膜(8)が形成され、その層間絶縁膜(8)には、層間絶縁膜(8)を貫通して不純物領域(7)を掘り込むようにコンタクトホール(9)が形成されている。コンタクトホール(9)内には、金属膜(10)、バリア層(11)、金属シリサイド(12)およびソース、ドレイン配線(14)が形成されている。ソース、ドレイン配線(14)は、タングステンから形成されている。

(もっと読む)

ビア及びエッチングされた構造におけるコンフォーマル絶縁層の形成方法及びパターン形成方法

マスク層の下にアンダーカット形状を形成するエッチングプロセスによって基板にビアが形成される。ビアはコンフォーマルな絶縁層で覆われ、この構造にエッチングプロセスを実施して水平面から絶縁層を取り除くと共にビアの垂直な側壁の絶縁層を残す。ビアの上部領域はエッチバックプロセスの際、アンダーカットハードマスクによって保護される。  (もっと読む)

(もっと読む)

積層型半導体装置

【課題】積層された複数の半導体チップ間で貫通電極切替情報を共有する。

【解決手段】複数の半導体チップ間でデータ転送を行うための複数の貫通電極を互いに共有した積層型半導体装置であって、複数の半導体チップに含まれる第1の半導体チップIFは、複数の貫通電極のうちデータ転送を行う貫通電極を指定する貫通電極切替情報SWを保持し、複数の半導体チップに含まれる第2の半導体チップCC0〜CC7に貫通電極切替情報SWを転送する。本発明によれば、貫通電極切替情報SWが第1の半導体チップIFから第2の半導体チップCC0〜CC7に転送されることから、第2の半導体チップには貫通電極切替情報SWを不揮発的に記憶する回路を設ける必要がない。これにより、第2の半導体チップのチップ面積を縮小することが可能となる。

(もっと読む)

半導体装置

【課題】ビアホールのアスペクト比が高くなればなるほど、バリアメタルのカバレッジが悪くなる。つまり、ビアホールの直径に対して深さが深ければ深いほど、ビアホールのボトム部に形成されるバリアメタルが不十分になり易い。その結果、ビアホール底部のアルミ層やチタン膜において、高抵抗化が起きる。また、ビアホール底端においては、電界が集中し、EM(ElectroMigration)によって劣化し、品質や寿命の低下が起きる。

【解決手段】ビアホールの開口後、2度のエッチングによってボトム部およびトップ部の形状をラウンド化する。その結果、ビアホールの低抵抗化および品質や寿命の向上が得られる。

(もっと読む)

半導体素子及びその製造装置

【課題】汎用性が高く、低コストで省資源である方法を採用し、実用性に富み、任意の場所、任意の形状に金属又は半導体を二次元的又は三次元的に形成できる半導体素子及びその製造装置を提供する。

【解決手段】炭素材料と金属酸化物材料又は半導体酸化物材料とを有する還元反応構造1Aを持つ層構造30Aを準備し、還元反応構造1Aに対して局所的にエネルギーを集中することが可能で、かつ還元反応構造1Aに対して2次元的又は3次元的に走査することが可能な熱源を用い、この熱源によって酸化還元反応が起こる温度以上に還元反応構造1Aの一部を走査しつつ選択的に加熱して、炭素材料により金属酸化物材料又は半導体酸化物材料をそれぞれ金属又は半導体に還元し、所望の形状の金属領域又は半導体領域(金属層又は半導体層3A)を形成することによって製造されることを特徴とする半導体素子40Aとすることにより上記課題を解決する。

(もっと読む)

半導体装置の製造方法

【課題】第1領域におけるライナー膜の膜厚と、第2領域におけるライナー膜の膜厚とが互いに異なる半導体装置において、コンタクトホールの形成時に、活性領域及び素子分離領域に削れが形成されることを防止する。

【解決手段】ゲート構造体Gbが密に配置された第1領域におけるライナー膜22b及び層間絶縁膜23に、互いに隣接するゲート構造体同士の間の領域を開口して、底部に第1の膜厚を有するライナー膜が残存する第1のコンタクトホール28rを形成する。次に、ゲート構造体が疎に配置された第2領域におけるライナー膜及び層間絶縁膜に、互いに隣接するゲート構造体同士の間の領域を開口して、底部に第2の膜厚を有するライナー膜が残存する第2のコンタクトホール34rを形成する。次に、第1のコンタクトホールの底部に残存するライナー膜、及び第2のコンタクトホールの底部に残存するライナー膜を除去する。第1の膜厚と第2の膜厚とは、同等である。

(もっと読む)

半導体装置及びその製造方法

【課題】柱状構造体の形成の際のリソグラフィの合わせずれの許容度を拡大し、デバイス特性の劣化を抑制する半導体装置及びその製造方法を提供する。

【解決手段】第1層と、前記第1層の主面の上に設けられた第2層と、前記主面を貫通し、前記第1層と前記第2層とに延在する導電性の柱状構造体と、前記主面の前記第2層の側において前記柱状構造体の側壁に付設された側部と、を備えたことを特徴とする半導体装置を提供する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】基板に発生する応力を低減できる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体素子が形成される素子領域を有する基板と、素子領域の隣接部分の基板に形成されるビアホールと、ビアホール内に絶縁層を介して設けられる導通部と、基板と絶縁層との間に設けられる緩衝層とを備え、緩衝層は、基板の熱膨張係数と緩衝層の熱膨張係数との差が、基板の熱膨張係数と絶縁層の熱膨張係数との差より小さい材料から形成される。

(もっと読む)

半導体パッケージ

【課題】異方性導電材料により貫通孔内電極の導通部分を形成することにより、信頼性の高い半導体パッケージを提供する。

【解決手段】半導体基板1に形成した貫通孔2の内部を異方性導電材料12により充填し、貫通孔2の上部で半導体基板1に設けられた配線層5と異方性導電材料12とを接続し、貫通孔2の下部に導電部材8の一部を挿入して、該導電部材8と異方性導電材料12とを接続することにより配線層5と導電部材8とを電気的に接続する。これにより貫通孔2の側壁構造に影響されない導通経路を貫通孔2の中央部に設けることができる。

(もっと読む)

1 - 20 / 78

[ Back to top ]