Fターム[5F033PP11]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | CVD(化学的気相成長法) (3,065) | MOCVD(有機金属CVD) (177)

Fターム[5F033PP11]に分類される特許

21 - 40 / 177

配線回路基板及びその製造方法

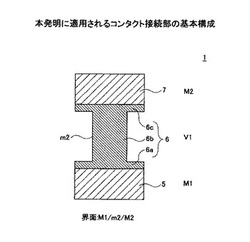

【課題】配線回路基板において、コンタクト抵抗の上昇を抑制し、熱応力による断線を防止することのできるコンタクト構造を提供する。

【解決手段】 配線回路基板は、第1配線層(5)、第2配線層(7)、及び前記第1配線層と前記第2配線層を電気的に接続するコンタクト配線(6)を有する。前記コンタクト配線は、前記第1配線層のコンタクト面を被覆する第1被覆部(6a)と、前記第2配線層のコンタクト面を被覆する第2被覆部(6c)と、前記第1被覆部と前記第2被覆部の間に延びるプラグ部(6b)を有する。前記第1被覆部、前記プラグ部、及び前記第2被覆部は、同一の導電性材料で一体的に形成された内部に界面のないコンタクト配線である。

(もっと読む)

空隙組込みの構造体及び方法

【課題】 空隙を組み込んだ構造体及びその形成方法を提供する。

【解決手段】 VLSI及びULSI用の空隙含有金属・絶縁体相互接続構造体を、光パターン化可能低k材料を用いて作成する方法、及び形成した空隙含有金属・絶縁体相互接続構造体を開示する。より具体的には、本明細書で説明する方法は、内部に種々異なる深さの空隙がフォトリソグラフィにより画定された光パターン化可能低k材料の内部に構築される相互接続構造体を提供する。本発明の方法においては、空隙を形成するのにエッチ・ステップは必要としない。光パターン化可能低k材料内部の空隙を形成するのに、エッチ・ステップを必要としないで、本発明において開示する方法は、高信頼性の相互接続構造体を提供する。

(もっと読む)

半導体装置の製造方法

【課題】キャパシタの誘電体膜を構成する強誘電体又は高誘電体の結晶性が良好であり、キャパシタのスイッチング電荷量が高く、低電圧動作が可能で信頼性が高い半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板110にトランジスタT1、T2を形成した後、ストッパ層120及び層間絶縁膜121を形成する。そして、層間絶縁膜121にコンタクトホールを形成し、層間絶縁膜121上に銅膜を形成してコンタクトホール内に銅を埋め込む。その後、低圧CMP研磨又はECMP研磨により層間絶縁膜121上の銅膜を除去して表面を平坦化し、プラグ124a,124bを形成する。次いで、バリアメタル125、下部電極126a、強誘電体膜127及び上部電極128aを形成する。このようにして、強誘電体キャパシタ130を有する半導体装置(FeRAM)が形成される。

(もっと読む)

パターン形成体の製造方法、機能性素子の製造方法および半導体素子の製造方法

【課題】本発明は、高精細なパターニングが可能なパターン形成体の効率的な製造方法を提供することを主目的とする。

【解決手段】本発明は、基板上に形成され、表面が疎水性を示す疎水性層上にフォトレジストパターンを形成するフォトレジストパターン形成工程と、上記フォトレジストパターンが形成された上記疎水性層の表面にエネルギーを照射して親水化し、親水性領域を形成する親水化工程と、上記フォトレジストパターンを剥離し、上記疎水性層表面に、上記親水性領域と上記親水化工程にて上記フォトレジストパターンで覆われていた疎水性領域とがパターン状に形成された親疎水パターンを形成するフォトレジストパターン剥離工程とを有することを特徴とするパターン形成体の製造方法を提供することにより、上記目的を達成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、バリアメタルの絶縁膜及びCuに対する密着性と、Cu拡散防止とを両立する。

【解決手段】 第1絶縁膜に設けた凹部の側壁に第2絶縁膜を形成し、第2絶縁膜の内側に順に第2絶縁膜との密着性が優れている第1の導電性バリア層、炭素を含有する第2の導電性バリア層、及び、Cu系埋込電極との密着性が優れている第3の導電性バリア層の3層構造のバリア層を介してCu系埋込電極を設けるとともに、前記第1の導電性バリア層と前記第2の導電性バリア層との界面と、前記第2の導電性バリア層と前記第3の導電性バリア層との界面に炭素混合領域を設ける。

(もっと読む)

コンタクトプラグ、配線、半導体装置およびコンタクトプラグ形成方法

【課題】金属シリサイド膜と銅コンタクトプラグ本体との間の拡散バリア層として、薄膜の酸化マンガンで構成された拡散バリア層を用いてはいるものの、金属シリサイド膜への銅原子の拡散、侵入を確実に抑止することができるようにする。

【解決手段】本発明のコンタクトプラグ10は、半導体装置の絶縁膜4に設けられたコンタクトホール5に形成され、コンタクトホール5の底部に形成された金属シリサイド膜3と、コンタクトホール5内で金属シリサイド膜3上に形成され、非晶質でシリコンを含む第1の酸化マンガン膜6aと、その第1の酸化マンガン膜6a上に形成され、微結晶を含む非晶質の第2の酸化マンガン膜6bと、その第2の酸化マンガン膜6b上に、コンタクトホール5を埋め込むように形成された銅プラグ層7と、を備えることを特徴としている。

(もっと読む)

半導体装置およびその製造方法

【課題】MIM容量素子形成時に生じる異常放電による容量絶縁膜の絶縁破壊を抑えることができて、高容量密度のMIM容量素子を得る。

【解決手段】半導体基板2上に、下部電極4−容量絶縁膜5−上部電極6からなるMIM容量素子1を有する半導体装置であって、上部電極4を構成する上部電極用金属膜は容量絶縁膜5との界面が、有機金属気相成長法(MOCVD)によりプラズマを用いないで堆積したアモルファス状のTiN膜などの金属窒化膜で構成されている。

(もっと読む)

表示装置の形成方法

【課題】従来のCMPを伴うダマシン法を用いた配線や電極の形成は、製造工程が煩雑であり高コスト化している。表示装置等の大型基板に配線形成を行うには平坦性等の高精度が要求されて好適せず、また研磨による配線材料の除去・廃棄量が多いという課題がある。

【解決手段】表示装置の形成方法は、基板上に下地絶縁層を設け、その層上に配線パターンに沿った第1の銅拡散防止層を設ける。次に、その第1の銅拡散防止層上面に第1の銅拡散防止層の幅より僅かに狭い銅配線層を積層し、銅配線層の全表面を覆うように、第2の金属拡散防止層を設ける方法である。

(もっと読む)

半導体装置

【課題】MIM構造の容量素子を有する半導体装置において、容量素子の信頼性を向上させることのできる技術を提供する。

【解決手段】下部電極DEと、容量絶縁膜CELと、上部電極UEとからなる容量素子において、下部電極DEを、半導体基板1の主面上の絶縁膜に形成された電極溝17aの内部に埋め込まれた金属膜によって構成し、上部電極UEを、TiN膜(下層金属膜)22と、TiN膜(下層金属膜)22上に形成されたTi膜(キャップ金属膜)23との積層膜によって構成する。

(もっと読む)

半導体装置の製造方法

【課題】銅配線を有する半導体装置において、銅配線の配線抵抗やコンタクトと抵抗を増加することなく信頼性を向上しうる半導体装置の製造方法を提供する。

【解決手段】絶縁膜に形成された開口部内に、銅に対して拡散防止作用を有する第1金属材料を含む第1の膜と、酸素を含有する銅膜を含む第2の膜と、銅と、酸素と結合することにより銅に対して拡散防止作用を有する第2金属材料とを含む第3の膜と、銅を主材料とする第4の膜とを含む配線層を形成した後、熱処理により、絶縁膜と第4の膜との間に、第1金属材料、第2金属材料及び酸素を含むバリア層を形成する。

(もっと読む)

Cu配線の形成方法

【課題】配線形成後に500℃以上の高温プロセスが存在する場合に適用可能なCu配線を形成すること。

【解決手段】500℃以上の温度の処理をともなう後工程が施されるCu配線の形成方法は、表面にトレンチおよび/またはホールを有する基板上の少なくともトレンチおよび/またはホールの底面と側面に、Cuの格子面間隔との差が10%以内の格子面間隔を有する金属からなる密着膜を形成する工程と、密着膜の上に前記トレンチおよび/またはホールを埋めるようにCu膜を形成する工程と、 Cu膜形成後の基板に350℃以上のアニール処理を行う工程と、Cu膜を研磨してCu膜のトレンチおよび/またはホールに対応する部分のみを残存させる工程と、研磨後のCu膜にキャップを形成してCu配線とする工程とを有する。

(もっと読む)

コンタクトプラグ、配線、半導体装置およびコンタクトプラグ形成方法

【課題】薄膜であっても銅(Cu)原子の金属シリサイド膜などへの拡散を充分に安定して抑止でき、尚且つ、小さな接触抵抗をもたらす比抵抗の小さな銅(Cu)からコンタクトプラグを形成できるようにする。

【解決手段】 本発明のコンタクトプラグ100は、半導体装置の絶縁膜104に設けられたコンタクトホール105に形成され、コンタクトホール105の底部に形成された金属シリサイド膜103と、コンタクトホール105内で金属シリサイド膜103上に形成された酸化マンガン膜106と、酸化マンガン膜106上に、コンタクトホール105を埋め込むように形成された銅プラグ層107と、を備え、酸化マンガン膜は非晶質からなる膜である、ことを特徴としている。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の設計自由度が高く、ゲート電極及びソース/ドレイン領域に接続されるコンタクト部の形成に問題が生じ難く、微細化プロセスに適した半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、(a)基体21上にゲート電極31を形成し、基体にソース/ドレイン領域37及びチャネル形成領域35を形成し、ソース/ドレイン領域37上にゲート電極31の頂面と同一平面内に頂面を有する第1層間絶縁層41を形成した後、(b)第1層間絶縁層41に溝状の第1コンタクト部43を形成し、(c)全面に第2層間絶縁層51を形成した後、(d)第1コンタクト部43の上の第2層間絶縁層51の部分に孔状の第2コンタクト部53を形成し、その後、(e)第2層間絶縁層51上に、第2コンタクト部53と接続された配線61を形成する各工程から成る。

(もっと読む)

高アスペクト比のフィーチャーへのタングステン堆積方法

【課題】高アスペクト比のフィーチャーをタングステン含有材料で充填する。

【解決手段】部分的に製造された半導体基板上の高アスペクト比のフィーチャーをタングステン含有材料で充填する方法が提供される。ある実施形態においては、当該方法は高アスペクト比のフィーチャーにタングステン含有材料を部分的に充填する工程とフィーチャー空洞から部分的に充填された材料を選択的に除去する工程とを有する。これらの方法を用いて処理された基板においては、高アスペクト比のフィーチャーに充填されたタングステン含有材料のステップカバレッジが改善され、シームの大きさが低減する。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、埋込導体構造の密着性とCu拡散防止能を両立する。

【解決手段】 半導体基板上に設けた絶縁膜に設けた埋込導体用の凹部内に埋め込まれたCuまたはCuを最大成分とする合金からなるCu系埋込導体層と、前記凹部に露出する前記絶縁膜との間にCoを最大成分とするとともに、少なくともMn、O及びCを含むCoMn系合金層を設ける。

(もっと読む)

成膜方法

【課題】 金属前駆体を用いて形成される金属含有膜を半導体装置の内部構造体に利用しても、金属汚染の発生を抑制することが可能な成膜方法を提供すること。

【解決手段】 基板の裏面を疎水化処理する工程(ステップ1)と、裏面が疎水化処理された基板の表面上に、π電子を含む金属前駆体を用いたCVD法を用いて、金属含有膜を形成する工程(ステップ2)と、を備える。

(もっと読む)

成膜方法

【課題】 キャップ膜、もしくはバリア膜として使用することが可能な膜を、形成するか形成しないかを選択することが可能となる成膜方法を提供すること。

【解決手段】 銅を使用している配線と絶縁膜とが表面に露出している基板に対してマンガン含有膜を成膜する成膜方法であって、銅を使用している配線上に、マンガン化合物を用いたCVD法を用いてマンガン含有膜を形成する工程(ステップ2)を備える。

(もっと読む)

ビアがガウジングされた相互接続構造体及びその製造方法

【課題】 ビア開口部の底部にガウジング構造部を含む相互接続構造体、及びその形成方法を提供する。

【解決手段】 本発明の方法は、ビア開口部の上に配置されるライン開口部内の堆積されたトレンチ拡散バリアの被覆率に影響を与えず、及び/又は、ビア開口部及びライン開口部を含む相互接続誘電体材料内にスパッタリングを行なうことによりビア開口部の底部にガウジング構造部を生成することに起因する損傷を生じさせない。こうした相互接続構造体は、最初に相互接続誘電体内にライン開口部を形成し、その後、ビア開口部、次いでガウジング構造部を形成することによって、ビア開口部の底部内にガウジング構造部を提供することにより達成される。

(もっと読む)

層間絶縁膜および配線構造と、それらの製造方法

【課題】 低誘電率で且つCFx、SiF4等のガスの発生がなく安定な半導体装置の層間絶縁膜とそれを備えた配線構造を提供する。

【解決手段】 下地層上に形成された絶縁膜を備えた層間絶縁膜において、前記層間絶縁膜は、実効誘電率が3以下である。配線構造は、層間絶縁膜と、層間絶縁膜に形成されたコンタクトホールと、前記コンタクトホール内に充填された金属とを備え、前記絶縁膜は、前記下地層上に形成され、表面が窒化されたフルオロカーボン膜を備えている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】複数の容量部が接続された容量プレート上面とロジック部とで配線層の高さを同じにするメモリ混載の半導体装置、および製造方法を提供する。

【解決手段】半導体装置の製造方法は、ロジック部の第1領域3の第1層間層43、53に配線34を形成する工程と、配線形成後にメモリ部の第2領域2の第1層間層43、53における表面領域をエッチングする工程と、エッチングした領域に容量12用の複数のシリンダ開口部を形成する工程と、複数のシリンダ開口部に下部電極層12C、誘電体層12B及び共通上部電極12A、13を形成して、複数の容量部12を形成する工程とを具備する。複数の容量部12を形成する工程は、第1層間層43、53の上面と共通上部電極12A、13の上面とが略同一平面上になるように共通上部電極12A、13を形成する工程を備える。

(もっと読む)

21 - 40 / 177

[ Back to top ]