Fターム[5F033PP11]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | CVD(化学的気相成長法) (3,065) | MOCVD(有機金属CVD) (177)

Fターム[5F033PP11]に分類される特許

101 - 120 / 177

半導体素子及びその製造方法

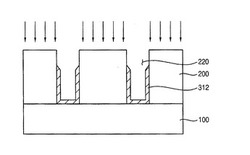

【課題】コンタクトプラグの形成のための平坦化工程で障壁層が損傷することを防止することができる半導体素子及びその製造方法を提供する。

【解決手段】本発明の半導体素子の製造方法は、半導体基板上に複数の導電性構造物間の空間を埋め立てて上面が平坦化された絶縁膜を形成し、絶縁膜を部分的に除去して基板の一部を露出する開口を形成する。その後、開口の下部側壁及び底面に沿って形成された残留金属膜と開口の上部側壁及び残留金属膜の表面に沿って形成された金属窒化膜とを含む障壁層を形成する。障壁層を含む開口を埋め立てて金属プラグを形成する。

(もっと読む)

成膜方法及び成膜装置

【課題】Mn含有膜やCuMn含有合金膜等を、CVD等の熱処理によって形成することにより、微細な凹部でも、高いステップカバレッジで埋め込むことができ、しかも、同一の処理装置で連続的な処理を行うようにして装置コストを大幅に低減化することができる成膜方法を提供する。

【解決手段】真空引き可能になされた処理容器14内で、遷移金属を含む遷移金属含有原料ガスと酸素含有ガスとにより被処理体Wの表面に、熱処理により薄膜を形成する。これにより、例えばMn含有膜やCuMn含有合金膜等を、CVD等の熱処理によって形成する際に、微細な凹部でも、高いステップカバレッジで埋め込むことが可能となる。

(もっと読む)

低温で基板のステップカバレージを改良する方法及び装置

【課題】基板のステップカバレージを均一にし、金属層を平坦にする方法を提供し、サブハーフミクロンの適用分野において連続してボイドのない接点またはバイアを形成することを目的とする。

【解決手段】本発明の1つの態様において、耐熱性層が、高アスペクト比の接点またはバイアを有する基板上に堆積される。CVDによる金属層が、低温で耐熱性層上に堆積され、PVD金属に対して共形のウェッティング層を提供する。次に、PVD金属が、前に形成されたCVD金属層上に、その金属の溶融点より低い温度で堆積される。結果として生じるCVD/PVD金属層は、実質的にボイドのないものである。金属被覆法は、統合された処理システムで実施されるのが好ましく、そのシステムは、PVDおよびCVD処理チャンバの両方を含み、基板が真空環境に入ると、バイアおよび接点の金属被覆が、CVDによるAl層上に酸化物層を形成することなく行うことができる。

(もっと読む)

タングステン膜の形成方法

【課題】本発明は半導体ウエハ等の被処理体に形成された凹凸部内にタングステン膜を形成するタングステン膜の形成方法に関し、Si基板上に形成された凹凸内に良好にタングステンの埋めこみを行うことを課題とする。

【解決手段】処理容器50内にMO−TiN膜からなるバリア膜3が形成されたSi基板Wを載置する工程と、処理容器50にWF6ガスとSiH4ガスとを交互に繰り返して供給する繰り返し工程を含み、前記バリア膜3上に第一のタングステン膜5を形成する工程と、処理容器50にWF6ガスとH2ガスとを同時に供給し、第一のタングステン膜5上に第二のタングステン膜6を形成する工程とを含むタングステン膜の形成方法であって、前記繰り返し工程では、Si基板Wの温度を150℃以上350℃以下に維持すると共に、前記WF6ガスの供給量を133Pa sec以上10kPa sec以下とし、WF6ガスのバリア膜3上への吸着量を飽和させる。

(もっと読む)

拡散バリアフィルムを含む半導体素子の形成方法

【課題】電気抵抗が低く、下部導電体と上部導電体間の拡散を防止する、拡散バリアフィルムの形成方法を提供する。

【解決手段】下部導電体102を含む基板100上に層間絶縁膜104を形成する。これに形成された開口部106に補助拡散バリア膜108を形成する。この上に拡散バリアフィルム120を形成する。この膜は、金属有機化学気相蒸着法による金属窒化物で形成され、部分的にプラズマ処理される。この結果、プラズマ処理された層とプラズマ処理されない層の積層膜となる。これにより、拡散バリアフィルムの比抵抗を減少させると共に、優れたバリア特性を有することができる。さらにこの上に粘着金属層122、第1アルミニウム膜130、第2アルミニウム膜132を形成する。これらの膜をパターンニングして上部導電体とプラグとする。

(もっと読む)

リセスチャネル構造を有するトランジスタを含む半導体装置およびその製造方法

【課題】特性異常の発生を低減することのできるリセスチャネル構造を有するトランジスタを含む半導体装置およびその製造方法を提供すること。

【解決手段】半導体シリコン基板の活性領域に設けられた第一のリセスおよび素子分離領域に設けられた第二のリセスと、リセスチャネル構造を有するトランジスタと、を少なくとも有する半導体装置であって、

前記トランジスタは、前記第一のリセス内部に設けられたゲート電極を有し、

前記ゲート電極は、前記第一のリセス内部に設けられた部分に加えて、前記第二のリセス内部に設けられた部分を有し、

前記第一のリセス内部に設けられた前記ゲート電極の部分と、前記第二のリセス内部に設けられた前記ゲート電極の部分とは、前記活性領域と前記素子分離領域との境界面と同一の面で互いに電気的に接続されていることを特徴とする半導体装置およびその製造方法。

(もっと読む)

金属膜の成膜方法、多層配線構造の形成方法、半導体装置の製造方法、成膜装置

【課題】金属膜を吸着および分解プロセスの繰り返しにより、効率よく成膜する。

【解決手段】成膜方法は、被処理基板表面に金属元素のカルボニル原料を気相分子の形で、前記気相分子の分解を抑制する気相成分と共に、前記気相成分の分圧を、前記カルボニル気相原料分子の分解が抑制される第1の分圧に設定して供給する第1の工程と、前記被処理基板表面において前記気相成分の分圧を、前記カルボニル原料の分解が生じる第2の分圧に変化させ、前記被処理基板表面に前記金属元素を堆積させる第2の工程と、よりなることを特徴とする。

(もっと読む)

層間絶縁膜および配線構造と、それらの製造方法

【課題】 リーク電流の発生や熱アニールによる膜の縮小が抑制された、低誘電率で安定な層間絶縁膜を提供することにある。

【解決手段】 層間絶縁膜は、Si原子を含有するハイドロカーボン層とN原子を含有するフルオロカーボン層とを積層してなり、かつ前記ハイドロカーボン層は、C原子数に対するH原子数の比(H/C)が0.8乃至1.2となる割合でH原子とC原子とを含有する。

(もっと読む)

金属シリサイド晶子上にナノ構造物を形成する方法、並びにこの方法により得られる構造物及びデバイス

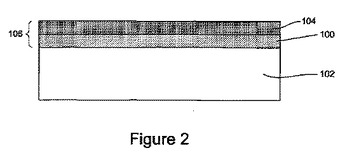

本発明の種々の実施形態は、非単結晶基板上にナノ構造物を形成する方法、並びにその結果得られるナノ構造物及びナノスケール機能デバイスに関する。本発明の一実施形態では、ナノ構造物を形成する方法は、金属層(100)及びシリコン層(104)を含む多層構造物(106)を形成することを含む。多層構造物(106)は、熱工程にかけられ、それにより金属シリサイド晶子(110)が形成される。金属シリサイド晶子(110)上にはナノ構造物(114)が成長される。本発明の別の実施形態では、構造物は、非単結晶基板(102)及び非単結晶基板(102)上に形成された層(108)を含む。層(108)は、金属シリサイド晶子(110)を含む。金属シリサイド晶子(110)上にいくつかのナノ構造物(114)が形成されてもよい。開示の構造物は、電子デバイス及び/又は光電子デバイスで使用されるいくつかの異なるタイプの機能デバイスを形成するために使用することができる。  (もっと読む)

(もっと読む)

多孔質低誘電率層の製造方法及び構造、相互接続処理方法及び相互接続構造

【課題】多孔質低誘電率層を形成する方法が、記載されている。

【解決手段】CVDプロセスは、基板に導入され、ここで、枠体前駆体及びポロゲン前駆体は供給される。枠体前駆体の供給の終了期間において、CVDプロセスの生成物の密度と否定的に相関している少なくとも一つの堆積パラメータの値は、減少する。

(もっと読む)

Cu配線膜形成方法

【課題】半導体デバイスでCu配線を用いる場合に、拡散バリア用下地膜とCu配線膜との密着性を、簡易な構成と簡略な工程で向上させることができ、製作コストの低下と生産効率の向上を実現できるCu配線膜形成方法を提供する。

【解決手段】拡散バリア用TiN膜を下地膜として成膜し、この下地膜の上にCu配線膜を成膜する方法であって、前記下地膜の成膜工程とCu配線膜の成膜工程の間に、下地膜の成膜工程後大気にさらすことなく真空一貫の状態で前記下地膜を200℃以上の温度で加熱するアニール工程を設ける。このアニール工程ではアンモニア単体またはアンモニアガスを含むガスを用い、該アニール工程の後、前記Cu膜をCVD法により成膜することで、前記下地膜とその後の成膜で堆積する上層のCu膜との密着性を高くすることができる。アニール工程は、下地膜の成膜を行うチャンバと同じチャンバで実施することもできる。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の高いBGAを有する半導体装置を提供する。

【解決手段】第1の主面上にパッド電極53を形成された半導体基板の第2の主面から前記パッド電極53に到達するビアホールVHを形成する工程と、前記ビアホールVH内を含む前記半導体基板の第2の主面上に絶縁膜を形成する工程と、前記絶縁膜上に緩衝層60を形成する工程と、前記ビアホールVHの底部の絶縁膜をエッチング除去する工程と、前記ビアホールVHを通して、前記パッド電極53と電気的に接続され、かつ前記ビアホールVHから前記緩衝層60上に延びる配線層64を形成する工程と、前記配線層64上に導電端子66を形成する工程と、前記半導体基板を複数の半導体チップ51Aに分割する工程と、を具備することを特徴とする。

(もっと読む)

薄膜の形成方法、成膜装置及び記憶媒体

【課題】原料として有機酸銅を用いることにより、微細な凹部を埋め込みつつ銅の薄膜を膜厚の制御性良く、しかも高い成膜レートで堆積させることができる成膜装置を提供する。

【解決手段】被処理体Wの表面に薄膜を形成する成膜装置20において、排気可能になされた処理容器22と、被処理体を載置するための載置台24と、被処理体を加熱するための加熱手段26と、処理容器に設けられて、処理容器内へガスを導入するためのガス導入部56と、ガス導入部へ気体の有機酸銅を供給する原料ガス供給手段68と、装置全体の動作を制御する装置制御部100とを備え、被処理体の表面に薄膜として銅膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】キャパシタ構造への水分・水素の浸入を可及的に防止するも、面内膜厚分布が極めて低く極めて優れた表面平坦性を有する層間絶縁膜を形成し、誘電体特性への影響やコンタクト抵抗のバラツキ等を抑えた信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】極低水分含有量のシリコン酸化膜である第1の絶縁膜3と、第1の絶縁膜3よりも水分含有量の多い、従って面内膜厚分布率の小さいシリコン酸化膜である第2の絶縁膜4との積層膜を形成し、これをCMPにより研磨する。強誘電体キャパシタ構造2の直上には第2の絶縁膜4が残らず除去され、第1の絶縁膜3の表面がある程度露出するまで研磨する。このとき、第1の絶縁膜3における第1の部分の上面から第2の絶縁膜4の上面にかけて表面平坦化されてなり、第1の絶縁膜3と、第1の絶縁膜3の第2の部分上に残る第2の絶縁膜4とからなる層間絶縁膜10が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極を好適な仕事関数を有する導電材料から構成することができ、ゲート電極の構成材料と層間絶縁層のエッチング条件との関係を考慮する必要のない半導体装置を提供する。

【解決手段】NMISFET及びPMISFETを含む半導体装置であって、各ゲート電極32A,32Bは、層間絶縁層の下層部28Aに設けられたゲート電極形成用開口部に埋め込まれており、NMISFETのゲート電極32Aの少なくとも底面部と側面部は第1の導電材料33Aから構成されており、PMISFETのゲート電極32Bの少なくとも底面部と側面部は第1の導電材料とは異なる第2の導電材料33Bから構成されており、各ゲート電極32A,32Bの頂面上には、導電性を有する保護層35A,35Bが形成されており、各ゲート電極用コンタクトプラグ44A,44Bは、保護層35A,35Bを介して、各ゲート電極32A,32Bの頂面に接続されている。

(もっと読む)

半導体装置とその製造方法

【課題】強誘電体キャパシタが備えるキャパシタ誘電体膜の特性を向上させることが可能な半導体装置とその製造方法を提供すること。

【解決手段】第1導電膜23の上に、少なくともゾル・ゲル法による成膜ステップを含む成膜方法により第1強誘電体膜24bを形成する工程と、第1強誘電体膜24bの上に、スパッタ法により第2強誘電体膜24cを形成する工程と、第2強誘電体膜24cの上に第2導電膜25を形成する工程と、第1導電膜23、第1、第2強誘電体膜24b、24c、及び第2導電膜25をパターニングして、下部電極23a、キャパシタ誘電体膜24a、及び上部電極25aを備えたキャパシタQを形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置の製造方法

【課題】TiNを含む金属膜上におけるレジスト除去速度の低下を抑え、レジスト残りが発生することがない安定したレジスト除去を実現できるようにする。

【解決手段】半導体装置の製造方法は、基板10の上に窒化チタンを含む金属膜12を形成する工程(a)と、金属膜12の上に酸化膜13を形成する工程(b)と、酸化膜13の上にレジストパターン14を形成する工程(c)と、レジストパターン14をマスクとして金属膜13を選択的にエッチングする工程(d)と、工程(d)よりも後に、レジストパターン14を酸素プラズマにより除去する工程(e)とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】強誘電体キャパシタが備えるキャパシタ誘電体膜の特性を向上させることが可能な半導体装置の製造方法を提供すること。

【解決手段】第1導電膜の上に、ゾル・ゲル法により強誘電体膜24を形成する工程と、強誘電体膜24上に第1導電性酸化金属膜25dを形成する工程と、第1導電性金属酸化膜25dに対して第1のアニールを行う工程と、第1導電性酸化金属膜25d上に第2導電性酸化金属膜25eを形成する工程と、第1導電膜23、強誘電体膜24、及び第2導電膜25をパターニングしてキャパシタを形成する工程とを有し、第1導電性酸化金属膜25dを形成する工程において、スパッタガスにおける酸素流量比が増大することにより強誘電体膜24の強誘電体特性が向上することを利用し、強誘電体特性を酸素流量比で調節する半導体装置の製造方法による。

(もっと読む)

半導体装置の製造方法

【課題】王水を用いることなくニッケルプラチナ膜の未反応部分を選択的に除去しうるとともに、プラチナの残滓が半導体基板上に付着するのを防止しうる半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極16と、ゲート電極16の両側のシリコン基板10内に形成されたソース/ドレイン拡散層24とを有するMOSトランジスタ26を形成し、シリコン基板10上に、ゲート電極16及びソース/ドレイン拡散層24を覆うようにNiPt膜28を形成し、熱処理を行うことにより、NiPt膜28とソース/ドレイン拡散層24の上部とを反応させ、ソース/ドレイン拡散層24上に、Ni(Pt)Si膜34a、34bを形成し、過酸化水素を含む71℃以上の薬液を用いて、NiPt膜28のうちの未反応の部分を選択的に除去するとともに、Ni(Pt)Si膜34a、34bの表面に酸化膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】シリサイド層の凝集を抑えることができ、コンタクト抵抗が低抵抗化され、断線の発生が抑制された半導体装置とその製造方法を提供する。

【解決手段】半導体装置は、半導体基板101上に形成されたゲート電極104および不純物拡散領域105と、ゲート電極14および不純物拡散領域105の上に形成されたシリサイド層106と、シリサイド層106上に形成された第1のエッチングストップ膜110とを備えている。第1のエッチングストップ膜110は、シリサイド層106上に設けられた下層コンタクトプラグ109の側面を囲んで形成される。

(もっと読む)

101 - 120 / 177

[ Back to top ]