Fターム[5F033PP11]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | CVD(化学的気相成長法) (3,065) | MOCVD(有機金属CVD) (177)

Fターム[5F033PP11]に分類される特許

121 - 140 / 177

半導体装置の製造方法

【課題】CMP(化学的機械研磨)法による金属膜の研磨をウエハ全体で過不足なく行うことが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、窪み5aが設けられた絶縁膜5の上にバリア層6を形成する工程S5と、金属膜7の一部7aが窪み5aに埋め込まれるようにバリア層6の上に金属膜7を形成する工程S6と、一部7aを残すように金属膜6をCMP法により研磨する工程S7とを具備する。バリア層6は、その配向性が半導体ウエハ1のウエハ面の全体で一様になるように形成される。よって、金属膜7の配向性がウエハ面の全体で一様になる。金属膜の結晶構造は、下地材料の表面状態の影響を受けるためである。金属膜の配向性の違いによりCMP法による研磨速度が異なるから、金属膜7の配向性がウエハ面の全体で一様であるとCMP法による研磨に過不足が生じることが防がれる。ゆえに、チップ歩留まりが向上する。

(もっと読む)

集積回路のメタライゼーションスキームにおけるバリア層のボトムレス堆積方法

【課題】デュアルダマシンメタライゼーションにおいて、Cu配線構造のバリア材料を絶縁層の表面上のみに選択的に形成し、接続構造部のエレクトロマイグレーションを抑制するとともに、下層導電層との接続抵抗を低減する選択的堆積方法を提供する。

【解決手段】Cu層20上の絶縁層14,15をエッチングしてトレンチとビアを開孔する。ビア底部のCu層の表面10に原子層成長(ALD)ブロック層を形成する。この後、原子層成長(ALD)法を用いてTiNバリア材料26を絶縁層表面12、13に堆積する。ブロック層により、ビア底部のCu層の表面にはバリアは形成されないため、ビア底部のCuは露出した状態のままである。開口部内にCu18を充填するとCu層に直接接続することが出来る。

(もっと読む)

金属統合のための新規な構造体及び方法

【課題】 誘電体材料内に形成されたライン開口部の水平面から拡散バリアが除去されるのを回避し、よって、誘電体材料内に損傷を導入しない、新しい改善された統合方法を提供すること。

【解決手段】 ビア開口部の1つの底部にガウジング構造部を含む相互接続構造体と、これを形成する方法が提供される。本発明によると、相互接続構造体を形成する方法は、上を覆うライン開口部内の付着された拡散バリアの被覆率を低下させず、ビア開口部及びライン開口部を含む誘電体材料内に、Arスパッタリングによって引き起こされる損傷を導入しない。本発明によると、このような相互接続構造体は、拡散バリア層を、ビア開口部内にのみ含み、上を覆うライン開口部内には含んでいない。この特徴は、ライン開口部の内部の導体の体積含有率を減少させることなく、ビア開口部領域の周りの機械的強度及び拡散特性の両方を強化する。本発明によると、このような相互接続構造体は、ライン開口部を形成し、かつ、ライン開口部内に拡散バリアを付着させる前に、ビア開口部の底部にガウジング構造部を形成することによって達成される。

(もっと読む)

金属配線構造用のルテニウム膜の形成方法

【課題】薄く且つ連続的なRu膜を形成する。

【解決手段】 反応室内で基板上にルテニウム(Ru)薄膜を堆積させる方法であって、(i)反応室内にルテニウム前駆体のガスを供給して、非環式ジエニルを含むルテニウム複合体であるルテニウム前駆体のガスを基板に吸着させる段階と、(ii)励起した還元ガスを反応室内に供給して、基板に吸着されたルテニウム前駆体を活性化させる段階と、(iii)段階(i)と(ii)を繰り返し、それにより基板上にルテニウム薄膜を形成する段階とを含む方法。

(もっと読む)

半導体素子の製造装置及びこれを用いた半導体素子の製造方法

【課題】本発明は、半導体素子の製造装置及びこれを用いた半導体素子の製造方法を提供するためのものである。

【解決手段】半導体素子の製造装置は、基板を移送するトランスファーチャンバーと、トランスファーチャンバーに連結され、基板の上に珪化窒化チタニウム層を形成するための第1工程チャンバーと、トランスファーチャンバーに連結され、珪化窒化チタニウム層の上にタンタリウム層を形成するための第2工程チャンバーと、トランスファーチャンバーに連結され、タンタリウム層の上に銅シード層を形成するための第3工程チャンバーと、を含む。これによって、効率よく銅配線を形成することができる。

(もっと読む)

半導体装置の製造方法、半導体装置の製造装置、半導体装置及び記憶媒体

【課題】銅膜とその下地膜との密着性がよく、配線間の抵抗の小さな半導体装置の製造方法等を提供する。

【解決手段】大気中の水分を吸収した多孔質の絶縁層(SiOC膜11)にトレンチ100の形成された基板(ウエハW)を処理容器内に載置し、バルブメタルからなる第1の下地膜(Ti膜13)を被覆する。絶縁層から放出された水分により、絶縁層と接する第1の下地膜の表面が酸化されてパッシベーション膜13aが形成される。一方、第1の下地膜の表面をバルブメタルの窒化物または炭化物からなる第2の下地膜に被覆し、その表面に銅の有機化合物を原料とするCVDにより銅膜15を成膜する。

(もっと読む)

半導体装置の製造方法、半導体装置の製造装置及び記憶媒体

【課題】有機不純物層の形成を抑え、且つ銅膜と下地となる金属との密着性のよい半導体装置の製造方法等を提供する。

【解決手段】チタン等の酸化傾向の高い金属からなるバリアメタル層13(下地膜)が被覆された基板(ウエハW)を処理容器内に載置し、水蒸気の供給の開始と同時またはその後、銅の有機化合物(例えばCu(hfac)TMVS)からなる原料ガスを供給して、水蒸気により酸化物層13aが形成されたバリアメタル層13の表面に銅膜を成膜する。次いで、このウエハWに熱処理を施して、酸化物層13aを、バリアメタル層13を構成する金属と銅との合金層13bに変換する。

(もっと読む)

成膜方法、成膜装置及び記憶媒体

【課題】有機不純物層の形成や銅膜の異常成長が少なく、下地膜との密着性のよい銅膜の成膜方法等を提供する。

【解決手段】基板が載置された処理容器内に水蒸気が存在する状態で、銅の有機化合物(例えばCu(hfac)TMVS)からなる原料ガスを供給して基板上に銅の密着層を形成する。次いで、処理容器内の水蒸気と原料ガスとを排出して、その後、処理容器内に再び原料ガスを供給することにより密着層の表面に銅膜を成膜する。

(もっと読む)

半導体素子のビットライン形成方法

【課題】ビットラインの抵抗を減らすための半導体素子のビットライン形成方法を提供する。

【解決手段】半導体素子のビットライン形成方法に関するものであり、所定の構造物が形成された半導体基板上にバリア金属膜を形成する段階と、バリア金属膜上に非晶質チタンカーボンニトリド膜を形成する段階と、ボロンガスが含まれた雰囲気で非晶質チタンカーボンニトリド膜上にタングステンシード層を形成する段階と、タングステンシード層上にタングステン膜を形成してビットラインを形成する段階を含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】フッ素添加カーボン膜を絶縁膜例えば層間絶縁膜として用い、この絶縁膜に銅を含む金属配線を形成するにあたり、絶縁膜と金属配線との間において、フッ素及び銅の拡散を防ぐこと。

【解決手段】フッ素添加カーボン膜からなる絶縁膜と、この絶縁膜に形成された銅配線と、の間に、フッ素の拡散を防止するための第1の膜であるチタン膜を形成し、第1の膜と胴配線との間に銅の拡散を防止するための第2の膜であるタンタル膜を形成する。

(もっと読む)

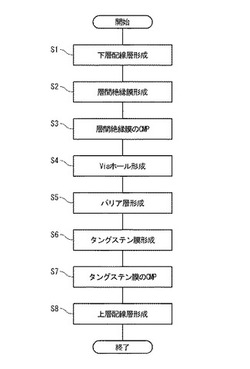

半導体装置の製造方法

【課題】接続孔部分における電気的特性のばらつきを低減することにより、半導体装置の信頼性および製造歩留まりを向上させることのできる技術を提供する。

【解決手段】成膜装置のドライクリーニング処理用のチャンバ57に備わるウエハステージ57a上に半導体ウエハSWを置いた後、還元ガスを供給して半導体ウエハSWの主面上をドライクリーニング処理し、続いて180℃に維持されたシャワーヘッド57cにより半導体ウエハSWを100から150℃の第1の温度で熱処理する。次いで半導体ウエハSWをチャンバ57から熱処理用のチャンバへ真空搬送した後、そのチャンバにおいて150から400℃の第2の温度で半導体ウエハSWを熱処理することにより、半導体ウエハSWの主面上に残留する生成物を除去する。

(もっと読む)

高融点金属窒化膜の形成方法

【課題】バリアメタルの材料となる高融点金属窒化物の成長工程を有する高融点金属窒化膜の形成方法に関し、配線のバリアメタルとなる高融点金属窒化物を低温で低抵抗に形成し、しかも、膜成長の際の反応生成物のチャンバ内の付着を防止するとともに、自然酸化膜の除去からコンタクトメタル、バリアメタルの成長までを減圧下で行うことを目的とする。

【解決手段】高融点金属のアルキルアミノ化合物を含むソースガスと還元性ガスとを使用して半導体基板上に化学気相成長法により高融点金属窒化膜を形成する高融点金属窒化膜の形成方法であって、還元性ガスを活性化する工程を含むことを特徴とする。

(もっと読む)

半導体容量素子の構造とその製造方法

【課題】本発明の課題は、十分な強誘電体特性を有する半導体容量素子及びその製造方法を提供することにある。

【解決手段】上記のような課題は、強誘電体と下部電極界面を単一とすることにより達成される。すなわち、本発明に係る半導体容量素子は、所定の電極材料を複数積層して形成される下部電極と;前記下部電極の一部の側壁に形成されるサイドウォールと;前記下部電極上に形成される誘電体層と;前記誘電体層上に形成される上部電極とを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】積層された導電性バリア層の酸素バリア性を向上させると共に、積層された導電性バリア層に生じる浮きや剥離を防止してコンタクト抵抗の安定化を図る。

【解決手段】半導体装置は、容量素子21とトランジスタのソース領域又はドレイン領域13とを電気的に接続するコンタクトプラグ15と、該コンタクトプラグ15の上に形成された高融点金属のみの窒化物である窒化チタンからなる導電層16Aと、窒化チタンアルミニウム膜、イリジウム膜及び酸化イリジウム膜の積層膜からなる酸素の拡散を防止する多結晶状の導電性酸素バリア層17とを有している。結晶配向性が低い窒化チタンからなる導電層16Aを導電性酸素バリア膜17の下側に設けたことにより、導電層16Aの直上に形成される導電性酸素バリア膜である窒化チタンアルミニウム膜は緻密な膜構造となるため、酸素の侵入を効果的に防止することができる。

(もっと読む)

銅配線膜形成方法及び配線膜

【課題】半導体基板上に形成され、凹部が設けられた絶縁膜上に拡散バリア用下地膜を形成し、その上に第1の銅膜を形成し、当該第1の銅膜を電極とした電解メッキ法により第2の銅膜を形成する銅配線膜形成方法において、密着性の改善に有効なCuシード膜のアニール処理を行っても、半導体基板上のホールやトレンチパターンの上角部(開口部近傍)といった基板表面において、Cuシード膜が弾かれその下の拡散バリア用下地膜が露出する現象を起こさずにアニール処理が行える方法と、これによる配線膜を提供する。

【解決手段】拡散バリア用下地膜の形成から前記第1の銅膜形成までの工程が、前記半導体基板を大気に晒すことなく真空一貫の状態で行われると供に、当該工程の間に、到達真空度で1×10-4Pa以下の真空状態にしてから前記拡散バリア用下地膜が加熱される。

(もっと読む)

接続部構造及びその製造方法

【課題】シリサイド上に接続孔を形成する際のエッチングで、高抵抗の変質層が発生することを防止する。

【解決手段】 基板中もしくは基板上に導電層を形成する。次に、導電層上を含む基板上に第1の金属膜を形成する。次に、基板に対して熱処理を行なって第1の金属膜と導電層とを反応させ、導電層上に選択的にシリサイド膜を形成する。次に、選択CVD法によりシリサイド膜上のみに第2の金属膜を形成する。次に、第2の金属膜上を含む基板上に絶縁膜を形成する。次に、絶縁膜の所定領域を開口して、第2の金属膜に到達するコンタクトホールを形成する。次に、コンタクトホール内を洗浄して、コンタクトホール底面における第2の金属膜表面に形成された変質層を除去する。

(もっと読む)

半導体装置およびその製造方法

【課題】Wを材質とするコンタクトプラグあるいはビアプラグを有する半導体装置およびその製造方法であって、コンタクトプラグあるいはビアプラグ内のバリアメタル膜を薄く形成する場合であっても、バリアメタル膜の下層に影響を与えにくい半導体装置およびその製造方法を実現する。

【解決手段】コンタクトホールまたはビアホール内に、TiN膜等のバリアメタル膜を形成する。その後、WF6ガスをB2H6ガスにより還元させるCVD法により、W核付け膜をバリアメタル膜上に形成する。そして、CVD法によりW核付け膜上にコンタクトプラグまたはビアプラグとしてWプラグを形成する。

(もっと読む)

銅でないメッキ可能層の上への銅の直接電気メッキのための方法

【課題】銅でないメッキ可能層の上への銅の直接電気メッキのためのプロセスを提供する。

【解決手段】半導体構造物中に相互配線を形成するためのプロセスであって、基板の上に誘電体層を形成する工程と、誘電体層の上に第一の障壁層を形成する工程と、第一の障壁層の上に第二の障壁層を形成する工程であって、第二の障壁層は、ルテニウム、白金、パラジウム、ロジウムおよびイリジウムからなる群から選ばれ、第二の障壁層の形成は、第二の障壁層中の酸素のバルク濃度が20原子パーセントまたはそれ未満となるように操作される工程と、第二の障壁層の上に導電層を形成する工程と、を含むプロセス。本プロセスは、さらに、第二の障壁を処理して第二の障壁層の表面の酸化物の量を減少させる工程を含むことができる。

(もっと読む)

半導体装置およびその製造方法

【課題】抵抗特性が改善され、信頼性が向上する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、下部配線110、層間絶縁膜100、200、拡散防止膜120、240、上部配線230を備えている。層間絶縁膜200は、下部配線110上に形成され、下部配線110の上面が露出するビアホール230aを有する。拡散防止膜240は、ビアホール230aの両側壁に形成される。上部配線230は、ビアホール230aを埋め込み、下部配線110と直接接触する。下部配線110内にはビアホール230aの延びる方向に拡散防止膜120の成分を含む不純物領域130が形成される。

(もっと読む)

半導体装置の製造方法

【課題】試作段階において、クラックや剥離のない高信頼度な低抵抗配線を備えた半導体装置を提供する。

【解決手段】まず、FIBによって所定のLSI配線11上の絶縁膜12を加工除去し、LSI配線11の表面を露出する接続穴13を形成する。続いて、第1のCVDガス雰囲気中でFIBを照射することによって接続穴13に例えばW(タングステン)を埋め込み、LSI配線11と電気的に接続されるコンタクト3を形成する。続いて、DMAu−TfacまたはHfacCu−tmvsの第2のCVDガス4雰囲気中でレーザ光5を重畳走査することによって、コンタクト3と電気的に低抵抗で接続されるAuまたはCuからなる導電性膜6を形成する。

(もっと読む)

121 - 140 / 177

[ Back to top ]