Fターム[5F033PP21]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | 成膜の方向性制御 (169)

Fターム[5F033PP21]の下位に属するFターム

コリメータを用いるもの (34)

バイアスを印加するもの (37)

化学的エッチングを伴うもの (5)

Fターム[5F033PP21]に分類される特許

1 - 20 / 93

半導体装置、および半導体装置の製造方法

【課題】実効的な低配線間容量を維持しつつ、高密着性かつ高い配線間絶縁信頼性を有する多層配線技術を提供する。

【解決手段】第一の絶縁膜は、シリコン、酸素及び炭素を含むシロキサン構造を含む少なくとも1層以上の絶縁膜であり、第一の絶縁膜内部のシロキサン構造は炭素原子数がシリコン原子数よりも多く、第一の絶縁膜と金属との界面及び第一の絶縁膜と第二の絶縁膜との界面のうち少なくとも何れか一方に、第一の絶縁膜内部よりも単位体積当たりの炭素原子数が少なく、且つ酸素原子数が多い改質層が形成されていることを特徴とする半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】アルミ膜を用いて生産コストの低減を図りながら、歩留りおよび信頼性を両立できる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板1上に形成された酸化膜3上に指向性スパッタによってチタン膜41が形成される。このチタン膜41上に通常のスパッタによって窒化チタン膜42が形成される。さらに、窒化チタン膜42上に、通常のスパッタによってアルミ膜43が形成される。チタン膜41は、(002)配向し、アルミ膜43は(111)配向する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子の容量の増大が実現される半導体装置を提供する。

【解決手段】半導体装置は、基板(半導体基板1)と、半導体基板1上に形成されており、配線および絶縁層により構成された配線層が複数積層された多層配線層と、平面視において、半導体基板1内の記憶回路領域に形成されており、多層配線層内に設けられた凹部40内に埋め込まれた少なくとも1以上の容量素子19および周辺回路を有する記憶回路200と、平面視において、半導体基板1内の記憶回路領域とは異なる領域である論理回路領域に形成された論理回路100と、当該凹部40内において、下部電極14、容量絶縁膜15、及び上部電極16から構成される前記容量素子19上に積層している上部接続配線18と、容量素子19が埋め込まれている配線層のうち最上層に設けられた論理回路100を構成する配線8bの上面に接するように設けられたキャップ層6cと、を備え、上部接続配線18の上面30とキャップ膜6cの上面34とが、同一面を構成している。

(もっと読む)

半導体構造およびその製造方法

【課題】カーボンナノチューブによりビアプラグを構成する半導体装置の製造方法において、製造効率を向上させる製造方法を提供する。

【解決手段】絶縁膜中にビアホールを形成し、ビアホールの底に触媒粒子3cを付着させる。ビアホール中において触媒粒子を起点に、カーボンナノチューブを絶縁膜の表面を超えて成長させ、複数のカーボンナノチューブよりなるカーボンナノチューブの束を形成する。絶縁膜上に前記カーボンナノチューブの束を覆って、誘電体膜の塗布液を塗布し、絶縁膜上における塗布液の厚さを、絶縁膜上における塗布膜の表面の高さが絶縁膜表面におけるカーボンナノチューブの高さ以下になるように減少させる。厚さが低減された塗布膜を硬化させて誘電体膜4Dを形成し、誘電体膜を除去して絶縁膜の表面を露出させ、絶縁膜の表面に、カーボンナノチューブによりビアプラグ4VA,4VBを形成する。

(もっと読む)

貫通配線基板の製造方法及び貫通配線基板

【課題】貫通孔の底面部付近において、導電層をカバレッジ良く形成し、接触不良がなく、電気的な安定性を向上させた貫通配線を、工程やコストを増加することなく形成する。

【解決手段】半導体基板の一方の面に第一絶縁層を介して導電部を形成する第一工程、ドライエッチング法により半導体基板の他方の面側から第一絶縁層が露呈するように貫通孔を形成する第二工程、貫通孔の内壁面および底面に第二絶縁層を形成する第三工程、第二絶縁層及び第一絶縁層のうち貫通孔の底面に位置する部分を除去し導電部を露呈する第四工程、第二絶縁層上に導電層を形成し該導電層を導電部と電気的に接続する第五工程、を有し、第四工程において、第二絶縁層に続いて導電部の一部をエッチングすると共に、エッチングにより除去された第一金属成分とエッチングガス成分とからなる第一副生成物を、貫通孔の底面部及びその近傍に位置する内壁面部に堆積させ、テーパー部を形成する。

(もっと読む)

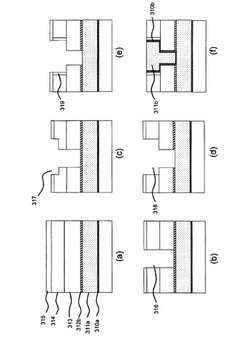

半導体装置の製造方法

【課題】めっき工程の埋設不良を抑制する。

【解決手段】半導体基板100上に設けられた層間絶縁膜320に開口部を形成する工程と、開口部上面にバリア層340を形成するバリア層形成工程と、バリア層340上に配線シード層を形成する配線シード層形成工程を有する。また、バリア層形成工程は、選択成膜工程と、スパッタエッチング工程を有する。バリア層340の選択成膜工程は、バリア層340を、開口部の平面部342のみに選択的に成膜する。次いで、バリア層340のスパッタエッチング工程は、平面部342のバリア層340をスパッタエッチングしながらバリア層340のスパッタ粒子を開口部の側壁部344に堆積させる。

(もっと読む)

半導体基板の製造方法

【課題】ビア配孔内に形成したカーボンナノチューブを埋め込む埋め込み膜が基板に均一に形成されないため基板の平坦化処理工程において層間絶縁膜が不均一に研磨されて、下層配線と上部電極がビア配線以外で電気的につながってしまう場合が発生する。

【解決手段】半導体基板における層間絶縁膜内のビアホール内にカーボンナノチューブを形成した後、基板全体をフッ化処理することにより、カーボンナノチューブが存在するビアホールにのみ埋め込み膜が形成され、その後に基板全体の平坦化処理のために基板を研磨する工程において、層間絶縁膜が局所的に研磨されることを防止する。

(もっと読む)

スパッタリング方法

【課題】 1μm以上の開口径を有する高アスペクト比のTSVホールHがパターニング形成された処理対象物に対して、被覆性よく成膜できるスパッタリング方法を提供する。

【解決手段】 真空チャンバ1内に処理対象物と、処理対象物に形成しようとする金属膜に応じて作製されたターゲット2とを対向配置し、処理対象物の全面に亘って垂直な磁場が作用するように垂直磁場を発生させ、この真空チャンバ内にスパッタガスを導入し、ターゲットに所定の電力を投入して真空チャンバ内にプラズマを形成してターゲットをスパッタリングし、処理対象物に高周波バイアス電力を投入してターゲットからのスパッタ粒子やプラズマ中で電子で電離したイオンを引き込むようにしたものにおいて、前記バイアス電力を、200〜600Wの範囲とする。

(もっと読む)

基板貫通の相互接続部を形成する方法

【課題】表側と裏側とを有する基板を含むマイクロエレクトロニクス・デバイスに基板を貫通する相互接続部を形成する方法を提供する。

【解決手段】基板の表側に回路素子(134)を形成するステップと、回路素子(134)に達するトレンチ(138)を基板の裏側に形成するステップと、ポリマー絶縁材料からなる層(140)をトレンチ(138)内に形成するステップと、ポリマー絶縁材料からなる層(140)を基板の表側から露出させるために、回路素子(134)に開口(150)を形成するステップと、ポリマー絶縁材料からなる層(140)のうち開口(150)によって露出された部分を基板の表側から除去するステップと、回路素子(134)と電気的に通じている導電相互接続層(142)をトレンチ(138)内に形成するステップと、を有する。

(もっと読む)

基板の配線方法及び半導体製造装置

【課題】基板上に形成された配線用パターンの底部までCu埋め込みが可能な基板の配線方法を提供する。

【解決手段】真空状態に保持された処理容器100内にて配線用パターンが形成された基板を配線する方法であって、ウエハ上の配線用パターンを所望のクリーニングガスにより洗浄する前工程と、前工程後、クラスタ化された金属ガス(金属ガスクラスタCg)を用いて配線用パターン内に金属ナノ粒子を埋め込む埋め込み工程と、を含むことを特徴とする基板の配線方法が提供される。

(もっと読む)

半導体装置の製造方法

【課題】高密度のカーボンナノチューブを容易に配線に用いることができる半導体装置の製造方法を提供する。

【解決手段】絶縁膜7にビアホール9を形成し、ビアホール9内及び絶縁膜7上に触媒部12を形成する。絶縁膜7上の触媒部12を不活化し、ビアホール9内の触媒部12を起点としてビアホール9内にカーボンナノチューブを成長させる。

(もっと読む)

配線を形成する方法及びプラズマスパッタリアクタ

【課題】アスペクト比の高いホール内に、被覆性の良好な、コンタクト抵抗の低いバリア層を形成する半導体装置の製造方法を提供する。

【解決手段】タンタルまたはタンタルナイトライド等のライナー材料をホール内にスパッタ堆積する。ロングスロースパッタリング、自己イオン化プラズマ(SIP)スパッタリング、誘導結合プラズマ(ICP)再スパッタリング及びコイルスパッタリングを1つのチャンバ内で組み合わせたリアクタ150を使う。ロングスローSIPスパッタリングは、ホール被覆を促進する。ICP再スパッタリングは、ホール底部のライナー膜の厚さを低減して、第1のメタル層との接触抵抗を低減する。ICPコイルスパッタリングは、ICP再スパッタリングの間、再スパッタリングによる薄膜化は好ましくないホール開口部に隣接しているような領域上に、保護層を堆積する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】バリアメタルの被覆性を向上させる。

【解決手段】本発明の半導体装置は、キャップ絶縁膜1d上に形成された絶縁膜と、絶縁膜に形成された配線溝と、配線溝の底面に形成されたビア孔と、少なくともビア孔の側壁を覆うバリアメタル膜と、を有する。ビア孔は、径が異なる複数の孔から構成されており、複数の孔は、下に向けて径が小さくなるように深さ方向に接続し、複数の孔の接続部にキャップ絶縁膜に対してほぼ平行な面を有する。

(もっと読む)

半導体装置の製造方法

【課題】保護素子としてSBDを搭載したMOSFETにおいては、SBDの特性を確保するためアルミニウム・ソース電極下のアルミニウム拡散バリア・メタル膜として、TiW(タングステンを主要な成分とする合金)膜が使用される。しかし、本願発明者らが検討したところによると、タングステン系バリア・メタル膜はTiN等のチタン系バリア・メタル膜と比べて、バリア性が低い柱状粒塊を呈するため、比較的容易にシリコン基板中にアルミニウム・スパイクが発生することが明らかとなった。

【解決手段】本願発明は、アルミニウム系メタル層と下層のシリコン系半導体層の間のバリア・メタル層として、タングステン系バリア・メタル膜をスパッタリング成膜によって形成する際、その下層をウエハ側にバイアスを印加したイオン化スパッタにより成膜し、上層をウエハ側にバイアスを印加しないスパッタにより成膜するものである。

(もっと読む)

半導体装置の製造方法

【課題】最新の0.15μmパワーMOSFETにおいては、微細化によるセル・ピッチの縮小のためトレンチ部(ソース・コンタクト用の溝)において、アルミニウム・ボイド(アルミニウム系電極内に形成されるボイド)が多発することが、本願発明者らによって明らかにされた。この欠陥の発生は、主にアスペクト比が前世代の0.84から一挙に2.8に上昇したことによると考えられる。

【解決手段】本願の一つの発明は、アスペクト比の大きい繰り返し溝等の凹部をアルミニウム系メタルで埋め込む際に、アルミニウム系メタル・シード膜の形成から埋め込みに至るまで、イオン化スパッタリングにより、実行するものである。

(もっと読む)

被処理体の成膜方法及び処理システム

【課題】線幅やホール径が小さな凹部や高アスペクト比の凹部に対して十分な埋め込みを行うことが可能な成膜方法を提供する。

【解決手段】凹部6を有する絶縁層4が表面に形成された被処理体Wに対して薄膜を形成する成膜方法において、前記凹部内の表面を含めて前記被処理体の表面にTiを含むバリヤ層12を形成するバリヤ層形成工程と、前記バリヤ層上にRuを含むシード層16を形成するシード層形成工程と、前記シード層上に前記シード層に対する導通性を補助するためにCuを含む補助シード層164を形成する補助シード層形成工程とを有する。

(もっと読む)

高アスペクト比プラグの充填方法

【課題】高アスペクト比を有するプラグを充填する方法を提供する。

【解決手段】高アスペクト比を有するプラグを充填する本発明の方法においては、核形成層を、バイアの側壁上ではなく、バイアの底に形成する。プラグ充填はバイアの底からトップへの方向であり、側壁から内側へではない。得られるプラグは、無ボイドであり、継ぎ目無しである。

(もっと読む)

半導体装置の製造方法

【課題】デュアルダマシン溝(接続孔)内への異物の残留を回避し、配線接続の信頼性および半導体装置性能の向上を図る。

【解決手段】第4配線層の配線33上に絶縁膜34〜38を順次形成し(絶縁膜34,36,38はシリコン窒化膜からなる。絶縁膜35,37はシリコン酸化膜からなる)、絶縁膜38に溝パターン40a、40bをフォトリソグラフィを用いて転写する。絶縁膜38の溝パターン40を埋め込む反射防止膜41を形成し、さらに孔パターン43を有するレジスト膜42を形成する。レジスト膜42の存在下でエッチング処理を施し、絶縁膜38,37,36および絶縁膜35の一部に孔パターン43を転写する。その後、レジスト膜42,反射防止膜41を除去し、絶縁膜38をマスクとして溝パターン40を絶縁膜37に、孔パターン43を絶縁膜35に転写する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置における基板貫通電極の形成において、貫通電極形成用穴内部にバリア層やめっきのためのシード層を成膜する際、貫通電極穴内部の成膜レートと、基板平面部の成膜レートが大きく異なるために、貫通電極形成用穴内部で所定の膜厚を得ようとすると、基板平面部には必要以上の厚みをもった膜が形成されてしまう。結果として、後工程でのウエットエッチングによる配線パターニングの際に、基板横方向へのエッチング液の入り込みによる大幅な寸法シフトが発生し、微細化の妨げとなっている。

【解決手段】貫通電極形成用穴の開口部を除く基板平面部にフォトレジストを形成してから成膜を行い、成膜後にフォトレジスト表面に付着した膜と共にフォトレジストを除去することで、貫通電極形成用穴内部に付着した薄膜は残したまま基板平面部を露出され、改めて基板平面部に必要分だけ成膜を行うことで課題を解決する。

(もっと読む)

配線構造及びその形成方法、並びに半導体装置

【課題】炭素元素からなる線状構造体を有する接続部の更なる低抵抗化を実現して、更なる接続部の微細化を可能とする。

【解決手段】ビア孔28a内を充填し、配線溝32aの内壁面を覆うように、例えば超臨界CVD法により、ビア孔28a内におけるCNT28d間の空隙及びCNT28dの中空内を導電材料34で埋め込み、ビアプラグ33と、ビアプラグ33上で配線溝32aの内壁面を覆う下地膜32bとを同時形成する。

(もっと読む)

1 - 20 / 93

[ Back to top ]