Fターム[5F033PP22]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | 成膜の方向性制御 (169) | コリメータを用いるもの (34)

Fターム[5F033PP22]に分類される特許

1 - 20 / 34

半導体装置、および半導体装置の製造方法

【課題】実効的な低配線間容量を維持しつつ、高密着性かつ高い配線間絶縁信頼性を有する多層配線技術を提供する。

【解決手段】第一の絶縁膜は、シリコン、酸素及び炭素を含むシロキサン構造を含む少なくとも1層以上の絶縁膜であり、第一の絶縁膜内部のシロキサン構造は炭素原子数がシリコン原子数よりも多く、第一の絶縁膜と金属との界面及び第一の絶縁膜と第二の絶縁膜との界面のうち少なくとも何れか一方に、第一の絶縁膜内部よりも単位体積当たりの炭素原子数が少なく、且つ酸素原子数が多い改質層が形成されていることを特徴とする半導体装置。

(もっと読む)

バリアメタル層の形成方法、及び、バリアメタル層の形成装置

【課題】金属層と、金属層上に形成された窒化金属層とからなるバリアメタル層を形成する際に、金属層の抵抗値が高められることを抑えつつ、窒化金属層を形成することのできるバリメタル層の形成方法、及びバリアメタル層の形成装置を提供する。

【解決手段】マルチチャンバ装置10は、Ti層を形成する金属層形成チャンバ13と、Ti層上に、該Ti層を構成するTiCl4と、NH*とを用いてTiN層を形成する窒化金属層形成チャンバ14とを備えている。窒化金属層形成チャンバ14では、TiN層が形成される前に、Ti層の表面が窒化される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子の容量の増大が実現される半導体装置を提供する。

【解決手段】半導体装置は、基板(半導体基板1)と、半導体基板1上に形成されており、配線および絶縁層により構成された配線層が複数積層された多層配線層と、平面視において、半導体基板1内の記憶回路領域に形成されており、多層配線層内に設けられた凹部40内に埋め込まれた少なくとも1以上の容量素子19および周辺回路を有する記憶回路200と、平面視において、半導体基板1内の記憶回路領域とは異なる領域である論理回路領域に形成された論理回路100と、当該凹部40内において、下部電極14、容量絶縁膜15、及び上部電極16から構成される前記容量素子19上に積層している上部接続配線18と、容量素子19が埋め込まれている配線層のうち最上層に設けられた論理回路100を構成する配線8bの上面に接するように設けられたキャップ層6cと、を備え、上部接続配線18の上面30とキャップ膜6cの上面34とが、同一面を構成している。

(もっと読む)

貫通配線基板の製造方法及び貫通配線基板

【課題】貫通孔の底面部付近において、導電層をカバレッジ良く形成し、接触不良がなく、電気的な安定性を向上させた貫通配線を、工程やコストを増加することなく形成する。

【解決手段】半導体基板の一方の面に第一絶縁層を介して導電部を形成する第一工程、ドライエッチング法により半導体基板の他方の面側から第一絶縁層が露呈するように貫通孔を形成する第二工程、貫通孔の内壁面および底面に第二絶縁層を形成する第三工程、第二絶縁層及び第一絶縁層のうち貫通孔の底面に位置する部分を除去し導電部を露呈する第四工程、第二絶縁層上に導電層を形成し該導電層を導電部と電気的に接続する第五工程、を有し、第四工程において、第二絶縁層に続いて導電部の一部をエッチングすると共に、エッチングにより除去された第一金属成分とエッチングガス成分とからなる第一副生成物を、貫通孔の底面部及びその近傍に位置する内壁面部に堆積させ、テーパー部を形成する。

(もっと読む)

半導体装置の製造方法

【課題】めっき工程の埋設不良を抑制する。

【解決手段】半導体基板100上に設けられた層間絶縁膜320に開口部を形成する工程と、開口部上面にバリア層340を形成するバリア層形成工程と、バリア層340上に配線シード層を形成する配線シード層形成工程を有する。また、バリア層形成工程は、選択成膜工程と、スパッタエッチング工程を有する。バリア層340の選択成膜工程は、バリア層340を、開口部の平面部342のみに選択的に成膜する。次いで、バリア層340のスパッタエッチング工程は、平面部342のバリア層340をスパッタエッチングしながらバリア層340のスパッタ粒子を開口部の側壁部344に堆積させる。

(もっと読む)

半導体装置およびその製造方法

【課題】より低コストで、より信頼性の高いMIMキャパシタを有する、より信頼性の高い半導体装置、およびその製造方法を提供する。

【解決手段】本製造方法は、半導体基板SUBを準備する工程と、半導体基板SUBの一方の主表面上に、アルミニウム層AC1を有する第1の金属電極LEL1と、第1の金属電極LEL1上の誘電体層DECと、誘電体層DEC上の第2の金属電極UELとを形成する工程とを備える。第1の金属電極LEL1を形成する工程においては、表面がRmax<80nm、Rms<10nm、Ra<9nmの関係を満たすように、アルミニウム層AC1が形成される。第1の金属電極LEL1を形成する工程には、少なくとも1層の第1のバリア層T1を形成する工程と、第1のバリア層T1上に、アルミニウム層AC1を形成する工程と、アルミニウム層AC1を構成する結晶を再結晶化する工程とを含んでいる。

(もっと読む)

半導体装置の製造方法

【課題】余分な工程を追加することなく、コンタクト抵抗の増加を抑制する半導体装置を提供する。

【解決手段】半導体装置の製造方法では、Cu配線上の第2層間絶縁膜内に設けたコンタクトホール内に第1のTi膜、TiN膜、第2のTi膜、第1のAl膜、及び第2のAl膜をこの順に形成する。第1のTi膜を成膜する際には、コンタクトホール底面上の第1の部分と第2層間絶縁膜上の第2の部分の膜厚の比(第1の部分)/(第2の部分)を0.05以下とする。また、第2のAl膜はアルミ・リフロー法を用いて形成し、この際に第2のTi膜及び第1のAl膜をアルミニウム・チタン合金膜とする。

(もっと読む)

半導体装置およびその製造方法

【課題】バリアメタルのステップカバレッジを向上させるボーダレスコンタクト構造を有する半導体装置を提供する。

【解決手段】低抵抗金属層と高融点金属元素を含む第1のバリアメタル膜を順次積層した構造の配線パタ―ン42Aと、配線パタ―ンを覆う層間絶縁膜43と、層間絶縁膜中に形成され、配線パタ―ンの上面の一部と側壁面の一部を露出し、さらに配線パタ―ンに、露出上面および露出側壁面を連結して形成された斜面をも露出斜面42dとして露出するビアホール43Aと、ビアホールの側壁面、露出上面および露出側壁面、さらに前記露出斜面に形成された、少なくとも低抵抗金属層の構成元素および高融点金属元素を含む導電性側壁膜43bと、導電性側壁膜を覆い、高融点金属元素を含む第2のバリアメタル膜と、前記第2のバリアメタル膜を介して充填し、前記第2のバリアメタル膜に接する導電性プラグと、を含む。

(もっと読む)

半導体装置

【課題】動作速度が低下することを抑制することができる半導体装置を提供する。

【解決手段】半導体装置は、MOSトランジスタ9を有するシリコン基板5と、シリコン基板5上に形成され、配線および絶縁膜により構成された配線層が複数積層された多層配線層と、多層配線層内に埋め込まれた、下部電極(下部電極膜91)、容量絶縁膜92、および上部電極(上部電極膜93)を有しており、メモリ素子を構成する容量素子90と、を備え、容量素子90とMOSトランジスタ9との間にダマシン形状の銅配線(第2層配線25)が少なくとも1層以上形成され、1つの配線(第2層配線25)の上面と容量素子90の下面とが略同一平面上にあり、容量素子90上に銅配線(プレート線配線99)が少なくとも1層以上形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通電極およびこれと一体的に形成された裏面電極を有する半導体装置において、貫通電極の膜厚と裏面電極の膜厚とを独立に制御することにより、貫通電極の剥離の問題と裏面配線の剥離の問題を同時に解消することができる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板10と、半導体基板の上方に形成された少なくとも1層からなる配線層13と、半導体基板の裏面から配線に達する貫通電極30と、半導体基板の裏面に設けられて貫通電極に接続された裏面配線40と、裏面配線に接続された外部端子50と、を含む半導体装置であり、裏面配線は、少なくとも外部端子との接続部を含む部分の膜厚が、貫通電極の膜厚よりも厚く形成されている。

(もっと読む)

半導体装置の製造方法

【課題】高密度のカーボンナノチューブを容易に配線に用いることができる半導体装置の製造方法を提供する。

【解決手段】絶縁膜7にビアホール9を形成し、ビアホール9内及び絶縁膜7上に触媒部12を形成する。絶縁膜7上の触媒部12を不活化し、ビアホール9内の触媒部12を起点としてビアホール9内にカーボンナノチューブを成長させる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】バリアメタルの被覆性を向上させる。

【解決手段】本発明の半導体装置は、キャップ絶縁膜1d上に形成された絶縁膜と、絶縁膜に形成された配線溝と、配線溝の底面に形成されたビア孔と、少なくともビア孔の側壁を覆うバリアメタル膜と、を有する。ビア孔は、径が異なる複数の孔から構成されており、複数の孔は、下に向けて径が小さくなるように深さ方向に接続し、複数の孔の接続部にキャップ絶縁膜に対してほぼ平行な面を有する。

(もっと読む)

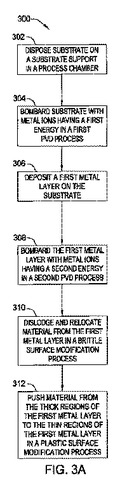

強化された銅のイオン化を伴うPVD銅シードオーバーハング再スパッタ

パターンが形成された基板上に金属を堆積させる方法および装置を提供する。金属層が,第1のエネルギーを有する物理蒸着工程で形成される。第2のエネルギーを用いて金属層上に第2の物理蒸着工程が行われ、ここで、堆積層は、脆性および塑性表面修正工程の相互作用を受け、基板上にほぼ同形の金属層が形成される。  (もっと読む)

(もっと読む)

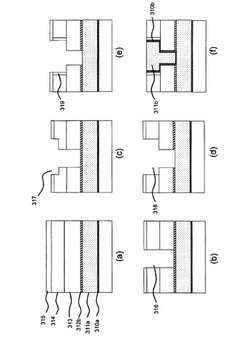

半導体装置および半導体装置の製造方法

【課題】貫通孔底部にノッチを有する半導体装置のノッチ部に被覆性良好な連続した金属膜を積層するプロセスを提供し、半導体装置の歩留まりと信頼性向上をはかること。

【解決手段】ノッチ部を含む貫通孔にCVD絶縁膜を積層した後に、バリア層およびシード層のメタル層をスパッタ法により形成する。メタル層のスパッタ成膜中に基板バイアス(負電圧)を印加して、アルゴンやクリプトン等の希ガスのプロセスガスイオンを貫通孔内部へ引き込み、既にある程度貫通孔底部に積層したメタル層をスパッタエッチングするか、貫通孔底部にメタル層を積層すると同時にスパッタエッチングしたメタル材料を貫通孔底部周辺のノッチ部分へ飛散させる。飛散したメタル材料はノッチ部分の絶縁膜上に付着し積層する。Ar+イオン等により飛散されたメタルは高いエネルギーを有する為、メタル層がノッチ内部へ強固に付着する。

(もっと読む)

半導体集積回路装置

【課題】複数層の埋め込み配線を有する半導体集積回路装置において、埋め込み配線と底部にて接続するプラグとその埋め込み配線との界面でのストレスマイグレーションによる導通不良を防ぐ。

【解決手段】たとえば、Cu配線33Wの幅が約0.9μm以上かつ約1.44μm未満であり、Cu配線43の幅およびプラグ43Pの径が約0.18μmである場合において、Cu配線33W上にてCu配線33WとCu配線43とを電気的に接続するプラグ43Pを2個以上配置する。

(もっと読む)

多層配線の形成方法

【課題】実効的な低配線間容量を維持しつつ、高密着性かつ高い配線間絶縁信頼性を有する多層配線の形成方法を提供する。

【解決手段】本発明に係る多層配線の形成方法は、シロキサン構造を含むビア層間絶縁膜43及び配線層間絶縁膜44を金属配線41a上に形成する第一の工程(図1[1])と、ビア層間絶縁膜43及び配線層間絶縁膜44の一部に金属配線41aに達する凹部としてのデュアルダマシン溝48を形成する第二の工程(図1[2]〜図2[2])と、ビア層間絶縁膜43及び配線層間絶縁膜44とデュアルダマシン溝48内で露出した金属配線41aとに水素プラズマ処理を施すことにより、ビア層間絶縁膜43及び配線層間絶縁膜44の表面に改質層49を形成するとともに金属配線金属配線41aの表面を還元する第三の工程(図3[1])と、を含むことを特徴とする。

(もっと読む)

貫通配線基板、半導体パッケージ及び貫通配線基板の製造方法

【課題】バリア層とシード層の境界に生じる隙間を低減して2層間の密着性を向上させ、貫通電極部分の信頼性に優れた貫通配線基板を提供する。

【解決手段】本発明に係る貫通配線基板10は、半導体基板11と、該半導体基板の一方の面側に配された電極部14と、前記半導体基板の他方の面側から一方の面側に至って配され、前記電極部の一部を露呈する貫通孔16と、前記貫通孔の内側面にシード層18を介して配された電解メッキ層19と、を少なくとも備えた貫通配線基板であって、前記シード層は、第一金属層18aと、該第一金属層に重ねて配された第二金属層18bとから構成され、前記第一金属層は、柱状形状をなす被膜であり、該柱状形状が、前記貫通孔の開口側に向かって指向性を有することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】低コストでメタルキャップ膜が形成された半導体装置及びその製造方法を提供する。

【解決手段】絶縁膜1bに配線溝及び配線孔を形成し、バリアメタル2bを成膜した後、銅層3bを配線溝及び配線孔に埋め込むように形成する。次に、CMP法により表面を平坦化して銅配線層を形成する。この際、CMP用のスラリーに異種金属を有する水溶性金属化合物を添加してCMPを行う。次に、不活性ガス又は還元性ガス雰囲気中で熱処理を行うことにより、銅配線層の表面に、異種金属が添加された銅層9bを形成する。その後、異種金属が添加された銅層9bを覆うようにバリア絶縁膜5bを形成する。

(もっと読む)

電子デバイス及びその製造方法

【課題】カーボンナノチューブを用いた配線構造を備える電子デバイスの製造方法について、炭素元素円筒型構造体からなるビアを歩留まり良く形成すること。

【解決手段】基板1上の第1絶縁膜2上に導電パターン5を形成する工程と、第1絶縁膜2と導電パターン5を覆う第2絶縁膜7を形成する工程と、第2絶縁膜7のうち導電パターン5の上にホール7aを形成する工程と、少なくともホール7a内の底面と第2絶縁膜7の上面に金属膜9を形成する工程と、金属膜9の表面に触媒粒子又は触媒膜からなる触媒面10を形成する工程と、触媒面10から炭素元素円筒型構造体11の束を成長する工程と、炭素元素円筒型構造体の束10の間隙に埋込膜12を形成する工程と、炭素元素円筒型構造体の束11及び埋込膜12及び金属膜9を研磨して第2絶縁膜7の上面から除去するとともに、埋込膜12及び炭素元素円筒型構造体の束11をホール7a内に残してビア13を形成する工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体キャパシタを覆う絶縁膜内に形成されて、その強誘電体キャパシタの電極に接続される導電性プラグをコンタクトホール内に埋め込む際に、工程増を抑制しながら、コンタクトホールの下への水素の浸入を防止する構造を備えた半導体装置を提供する。

【解決手段】絶縁膜20内であってキャパシタ上部電極18の上に形成されたコンタクトホール20e内に埋め込まれる導電性プラグ21eとして、アルミニウム膜32を有する複数層31〜34の構造を採用し、これにより、タングステン膜34をコンタクトホール20e内に充填する際に、水素がコンタクトホール20eの下の強誘電体キャパシタ17aに侵入することをアルミニウム膜32によって防止する。

(もっと読む)

1 - 20 / 34

[ Back to top ]