Fターム[5F033PP23]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | 成膜の方向性制御 (169) | バイアスを印加するもの (37)

Fターム[5F033PP23]に分類される特許

1 - 20 / 37

Cu配線の形成方法および成膜システム

【課題】Cuめっきを用いることなくPVDのみでトレンチまたはホールCuを埋め込んでCu配線を形成すること。

【解決手段】ウエハWに形成されたトレンチ203を有する層間絶縁膜202の全面にバリア膜204を形成する工程と、バリア膜204の上にRu膜205を形成する工程と、Ru膜205の上にPVDによりCuがマイグレーションする条件でトレンチ203内に第1のCu膜206を形成する工程と、第1のCu膜206の上に、第1のCu膜206よりも大きな成膜速度でPVDにより第2のCu膜207を形成する工程と、CMPにより全面を研磨する工程とを有する。

(もっと読む)

薄膜の成膜方法

【課題】基板上への薄膜の成膜速度を上げ、かつトレンチやビアホールの底面に効率よく薄膜を成膜できる薄膜の形成方法を提供すること。

【解決手段】本発明の成膜方法は、開口幅又は開口径が3μm以下で、かつ、アスペクト比が1以上の段差であるトレンチ又はビアホールを有する基板上に薄膜を成膜する成膜方法であり、真空排気可能な処理室に、基板を支持する第1の電極と、前記基板に対向するように配置されターゲットを支持する第2の電極と、前記第2の電極の外側に配置されて当該第2の電極の内側にカスプ磁界を形成する複数のマグネットと、を備え、

前記処理室にNeを含む処理ガスを導入し、前記第1の電極と前記第2の電極の少なくとも一方にプラズマ形成用の高周波電力を供給すると共に、前記第2の電極上にカスプ磁場を生成してプラズマを発生させ、ターゲット物質をトレンチ又はビアホールを有する基板上に成膜する。

(もっと読む)

半導体装置及びその配線の形成方法

【課題】 密着性を低下させることなく切削性を向上させることが可能な半導体装置及びその配線の形成方法を提供する。

【解決手段】 基板1上に開口部を形成するように絶縁樹脂4を形成する工程と、前記絶縁樹脂4上と、前記開口部の側壁面5aと底面とに第1配線層7を形成する工程と、前記第1配線層7上に第2配線層8を設ける工程と、前記開口部の前記側壁面5a上に形成された前記第1配線層7を露出するように切削して平坦化する工程とを含み、前記第1配線層7を形成する工程では、前記開口部の前記側壁面5aに形成される前記第1配線層7の厚さより前記底面に形成される前記第1配線層7の厚さの方が厚くなるように形成することを特徴としている。

(もっと読む)

成膜方法及び成膜装置

【課題】 ボイド等の発生を防止できるように凹部内に金属膜の成膜を施すことができる成膜方法である。

【解決手段】 処理容器22内でプラズマにより金属のターゲット76から金属イオンを発生させてバイアスにより引き込んで凹部4が形成されている被処理体に金属の薄膜を堆積させる成膜方法において、ターゲットから金属イオンを生成し、その金属イオンをバイアスにより引き込んで凹部内に下地膜90を形成する下地膜形成工程と、金属イオンを発生させない状態でバイアスにより希ガスをイオン化させると共に発生したイオンを引き込んで下地膜をエッチングするエッチング工程と、ターゲットをプラズマスパッタリングして金属イオンを生成し、その金属イオンをバイアス電力により引き込んで金属膜よりなる本膜92を堆積しつつ、その本膜を加熱リフローさせる成膜リフロー工程とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】より低コストで、より信頼性の高いMIMキャパシタを有する、より信頼性の高い半導体装置、およびその製造方法を提供する。

【解決手段】本製造方法は、半導体基板SUBを準備する工程と、半導体基板SUBの一方の主表面上に、アルミニウム層AC1を有する第1の金属電極LEL1と、第1の金属電極LEL1上の誘電体層DECと、誘電体層DEC上の第2の金属電極UELとを形成する工程とを備える。第1の金属電極LEL1を形成する工程においては、表面がRmax<80nm、Rms<10nm、Ra<9nmの関係を満たすように、アルミニウム層AC1が形成される。第1の金属電極LEL1を形成する工程には、少なくとも1層の第1のバリア層T1を形成する工程と、第1のバリア層T1上に、アルミニウム層AC1を形成する工程と、アルミニウム層AC1を構成する結晶を再結晶化する工程とを含んでいる。

(もっと読む)

スパッタリング方法

【課題】 1μm以上の開口径を有する高アスペクト比のTSVホールHがパターニング形成された処理対象物に対して、被覆性よく成膜できるスパッタリング方法を提供する。

【解決手段】 真空チャンバ1内に処理対象物と、処理対象物に形成しようとする金属膜に応じて作製されたターゲット2とを対向配置し、処理対象物の全面に亘って垂直な磁場が作用するように垂直磁場を発生させ、この真空チャンバ内にスパッタガスを導入し、ターゲットに所定の電力を投入して真空チャンバ内にプラズマを形成してターゲットをスパッタリングし、処理対象物に高周波バイアス電力を投入してターゲットからのスパッタ粒子やプラズマ中で電子で電離したイオンを引き込むようにしたものにおいて、前記バイアス電力を、200〜600Wの範囲とする。

(もっと読む)

表示装置用Al合金膜

【課題】450〜600℃程度の高温下に曝されてもヒロックが発生せず高温耐熱性に優れており、膜自体の電気抵抗(配線抵抗)も低く、アルカリ環境下の耐食性にも優れた表示装置用Al合金膜を提供する。

【解決手段】Ta、Nb、Re、Zr、W、Mo、V、Hf、Ti、CrおよびPtよりなる群(X群)から選択される少なくとも一種の元素と、希土類元素の少なくとも一種とを含み、450〜600℃の加熱処理を行なったとき、下記(1)の要件を満足する表示装置用Al合金膜である。

(1)Alと、X群から選択される少なくとも一種の元素と、希土類元素の少なくとも一種とを含む第1の析出物について、円相当直径20nm以上の析出物が500,000個/mm2以上の密度で存在する。

(もっと読む)

電子デバイスの製造方法

【課題】カーボン膜の抵抗率を低減することができる電子デバイスの製造方法を提供する。

【解決手段】基板11が載置されたチャンバ4内に炭素を含有する原料ガスを供給する。基板11の周囲からチャンバ4内のアノード1に向けて電子を放出させてチャンバ4内にプラズマ14を発生させ、基板11上にグラファイト、グラフェン等のカーボン膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】高密度のカーボンナノチューブを容易に配線に用いることができる半導体装置の製造方法を提供する。

【解決手段】絶縁膜7にビアホール9を形成し、ビアホール9内及び絶縁膜7上に触媒部12を形成する。絶縁膜7上の触媒部12を不活化し、ビアホール9内の触媒部12を起点としてビアホール9内にカーボンナノチューブを成長させる。

(もっと読む)

スパッタリング装置およびスパッタリング方法

【課題】単一のスパッタリングチャンバを用いて基板に形成された開口部内へのAl材料のコンタクト埋め込みを適切に行えるスパッタリング装置を提供する。

【解決手段】スパッタリング装置100は、Alからなるターゲット35Bおよび開口部が形成された基板34Bを格納可能なスパッタリングチャンバ30と、カソードユニット41およびアノードA間の放電によりプラズマを形成可能なプラズマガン40と、プラズマガン40から放出されたプラズマを磁界の作用によりシート状に変形可能な磁界発生手段24A、24Bと、を備える。シートプラズマ27は、スパッタリングチャンバ30内の基板34Bとターゲット35Bとの間を通過するように誘導され、シートプラズマ27中の荷電粒子によってターゲット35BからスパッタリングされたAl材料が基板34Bの開口部に堆積する際に、Al材料からなる堆積膜のカバレッジ性が、プラズマ放電電流IDおよび基板バイアス電圧VAに基づいて調整されている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置における基板貫通電極の形成において、貫通電極形成用穴内部にバリア層やめっきのためのシード層を成膜する際、貫通電極穴内部の成膜レートと、基板平面部の成膜レートが大きく異なるために、貫通電極形成用穴内部で所定の膜厚を得ようとすると、基板平面部には必要以上の厚みをもった膜が形成されてしまう。結果として、後工程でのウエットエッチングによる配線パターニングの際に、基板横方向へのエッチング液の入り込みによる大幅な寸法シフトが発生し、微細化の妨げとなっている。

【解決手段】貫通電極形成用穴の開口部を除く基板平面部にフォトレジストを形成してから成膜を行い、成膜後にフォトレジスト表面に付着した膜と共にフォトレジストを除去することで、貫通電極形成用穴内部に付着した薄膜は残したまま基板平面部を露出され、改めて基板平面部に必要分だけ成膜を行うことで課題を解決する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】上層配線の幅によらずにコンタクトプラグの底面がアンカー構造となり、下層配線との接続抵抗を低減できる半導体装置とその製造方法を提供する。

【解決手段】基板に下層配線W1となる第1導電層を形成し、絶縁膜を形成し、上層配線用溝とこれに連通するようにコンタクトホールCHを形成する。次に、コンタクトホール及び上層配線用溝の内壁面を被覆してバリアメタル層を形成し、その上層にコンタクトホール及び上層配線用溝に埋め込んで第2導電層を形成する。ここで、上層配線用溝及びコンタクトホールを形成する工程において、上層配線W2と下層配線W1の交差する領域に、上層配線にスリットSL1,SL2または切り欠きを設けて幅が狭くなった部分NPが設けられるように上層配線用溝を形成し、この幅が狭くなった部分NPにおいてコンタクトホールCHを形成する。

(もっと読む)

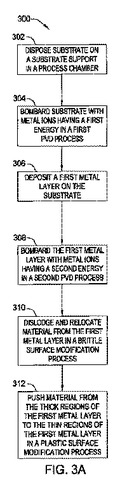

強化された銅のイオン化を伴うPVD銅シードオーバーハング再スパッタ

パターンが形成された基板上に金属を堆積させる方法および装置を提供する。金属層が,第1のエネルギーを有する物理蒸着工程で形成される。第2のエネルギーを用いて金属層上に第2の物理蒸着工程が行われ、ここで、堆積層は、脆性および塑性表面修正工程の相互作用を受け、基板上にほぼ同形の金属層が形成される。  (もっと読む)

(もっと読む)

ダメージフリー被覆刻設堆積法

【課題】周辺表面を汚染もしくは乱さずに、スパッタリングした銅シード層を堆積させて、所望の形状に刻設する方法を提供する。

【解決手段】底部516と、側壁514と、上側開口526とを有する複数の凹状のデバイス特徴を含む基板上に銅シード層を堆積させる方法であって、a)基板表面からのスパッタリングを引き起こす態様において前記凹状のデバイス特徴の基板表面に衝突することなく前記銅シード層の第1の部分を前記基板上にスパッタ堆積するステップと、b)前記銅シード層の第2の部分を前記基板上にスパッタ堆積すると同時に、銅シード層の前記第1の部分の少なくとも一部を、前記複数の凹状のデバイス特徴のそれぞれの底部から対応する側壁へと再配分するステップと、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】Cuを含む配線について、配線抵抗を低く維持しつつ、しかも、ストレスマイグレーション耐性の劣化を伴うことなく、エレクトロマイグレーション耐性を向上し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10の上方に形成された層間絶縁膜36と、層間絶縁膜36内に形成されたCuより成る配線50と、層間絶縁膜36と配線50の間に形成され、Ti膜42とTa膜44との積層膜より成るバリアメタル膜46とを有し、配線50表面に、TiとSiとを含む界面層54が形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通孔底部にノッチを有する半導体装置のノッチ部に被覆性良好な連続した金属膜を積層するプロセスを提供し、半導体装置の歩留まりと信頼性向上をはかること。

【解決手段】ノッチ部を含む貫通孔にCVD絶縁膜を積層した後に、バリア層およびシード層のメタル層をスパッタ法により形成する。メタル層のスパッタ成膜中に基板バイアス(負電圧)を印加して、アルゴンやクリプトン等の希ガスのプロセスガスイオンを貫通孔内部へ引き込み、既にある程度貫通孔底部に積層したメタル層をスパッタエッチングするか、貫通孔底部にメタル層を積層すると同時にスパッタエッチングしたメタル材料を貫通孔底部周辺のノッチ部分へ飛散させる。飛散したメタル材料はノッチ部分の絶縁膜上に付着し積層する。Ar+イオン等により飛散されたメタルは高いエネルギーを有する為、メタル層がノッチ内部へ強固に付着する。

(もっと読む)

半導体装置及びその製造方法

【課題】バリア膜を薄くする場合であっても良好なバリア性を確保し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上に形成された第1の導電体32と、半導体基板上及び第1の導電体上に形成され、第1の導電体に達するコンタクトホール52と、コンタクトホールの上部に接続された溝54とが形成された、酸素を含む絶縁膜48と、コンタクトホールの側面並びに溝の側面及び底面に形成された酸化ジルコニウム膜62と、コンタクトホール内及び溝内における酸化ジルコニウム膜上に形成されたジルコニウム膜64と、コンタクトホール内及び溝内に埋め込まれたCuより第2の導電体70とを有している。

(もっと読む)

薄膜トランジスタアレイ基板、その製造方法、及び表示装置

【課題】蓄積容量素子の占有面積を小さくすることが可能な薄膜トランジスタアレイ基板、その製造方法、及び表示装置を提供すること

【解決手段】本発明にかかる薄膜トランジスタアレイ基板は、基板1上に形成され、ソース/ドレイン領域を有する半導体層3と、ゲート絶縁膜4と、ゲート電極5と、層間絶縁膜6aと、ソース/ドレイン領域に接続する配線電極71、72と、保護膜8と、配線電極72に接続する画素電極9と、半導体層3より延在して形成された下部容量電極3aと、ゲート電極5と同じ層によって形成され、ゲート絶縁膜4を介して下部容量電極3aの対面に配置された共通配線電極5aと、層間絶縁膜6aより膜厚の薄い誘電体膜(保護膜8)を介して共通配線電極5aの対面に配置された上部容量電極9aと、を備えるものである。

(もっと読む)

半導体基板上の薄膜層のアパーチャのための充填装置

【課題】1以上のアスペクト比を有する多層集積回路のビア、スルーホール又はトレンチにAl電気コンタクトを形成する。

【解決手段】スパッタチャンバと、堆積チャンバと、移送チャンバと、を備え、半導体基板上における薄膜層のアパーチャを充填する充填装置において、スパッタチャンバは、スパッタ堆積材料の供給源となるターゲットカソードと、半導体基板を支持するための基板位置決め部材と、DC電源装置を具備し、ターゲットカソードからスパッタされた種を生成するために使用される第1のプラズマ発生ユニットと、基板位置決め部材に接続された基板バイアスRF電源装置と、RF電源装置を具備し、ターゲットカソードと基板位置決め部材との間に位置して、ターゲットカソードから前もってスパッタされた種をイオン化又は再イオン化するために使用される第2のプラズマ発生ユニットと、を具備する。

(もっと読む)

半導体装置のCu配線およびその製造方法

【課題】本発明の目的は、配線溝や層間接続路表面に形成されたTaNからなるバリア層との密着性が良好なCu配線と、このCu配線を製造できる方法を提供する。本発明の他の目的は、半導体基板上の絶縁膜に形成された配線溝や層間接続路の幅が狭く、深い場合でも、バリア層との密着性が良好で、配線溝や層間接続路の隅々に亘って埋め込まれているCu配線と、このCu配線を製造できる方法を提供する。

【解決手段】半導体基板上の絶縁膜に形成された配線溝または層間接続路に埋め込まれたCu配線を、(1)配線溝側または層間接続路側に形成されたTaNからなるバリア層と、(2)Pt、In、Ti、Nb、B、Fe、V、Zr、Hf、Ga、Tl、Ru、ReおよびOsよりなる群から選ばれる1種以上の元素を合計で0.05〜3.0原子%含有するCuからなる配線本体部とで構成すればよい。

(もっと読む)

1 - 20 / 37

[ Back to top ]