Fターム[5F033QQ12]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | ドライエッチング (6,179) | プラズマエッチング (898)

Fターム[5F033QQ12]に分類される特許

41 - 60 / 898

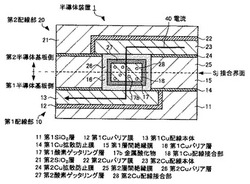

半導体装置、電子デバイス、及び、半導体装置の製造方法

【課題】 より信頼性の高いCu−Cu接合界面を有する半導体装置及びその製造方法を提供する。

【解決手段】 半導体装置1を、第1の配線18を含む第1半導体部10と、第1半導体部10と貼り合わせて設けられ、第1の配線18と電気的に接合された第2の配線28を含む第2半導体部20とを備える構成とする。さらに、半導体装置1は、酸素に対して水素よりも反応し易い金属材料と酸素とが反応して生成された金属酸化物17bを備える。そして、この金属酸化物17bを、第1の配線18及び第2の配線28の接合界面Sj、並びに、第1の配線18及び第2の配線28の少なくとも一方の内部を含む領域に拡散させた構成とする。

(もっと読む)

電子部品の製造方法

【課題】導電膜を含む層の加工によって密の配線と疎の配線とが混在して形成された配線層で、所望の配線間の領域にのみ空隙を形成することができる電子部品の製造方法を提供する。

【解決手段】実施形態によれば、電子部品の製造方法は、まず、密の配線と疎の配線とを含む配線パターンとなるように、基板1上の導電性材料膜を含む加工対象を加工する。ついで、密の配線の形成領域にのみ配線間を埋め込む犠牲膜111を形成した後、基板1上に絶縁膜112を形成する。絶縁膜112上にレジスト113を塗布し、密の配線の形成領域上の一部と疎の配線の形成領域とが露出するようにレジスト113のパターニングを行った後、レジスト113をマスクとして絶縁膜112をエッチングする。さらに、密の配線の形成領域上の一部を通して、犠牲膜111を除去する。そして、疎の配線の形成領域で隣接する配線間を埋め込むように基板1上に埋込絶縁膜114を形成する。

(もっと読む)

素子付き基板、赤外線センサー、および貫通電極形成方法

【課題】マイグレーションの問題を生じることなく、微細でアスペクトの高く絶縁特性に優れた絶縁膜を備えた貫通電極を有する素子付き基板、赤外線センサーおよび貫通電極形成方法を提供する。

【解決手段】予め、素子回路形成前のベース基板にビアホールを形成し、前記ベース基板の素子回路形成面と前記ビアホールの内面に熱酸化により絶縁膜を形成する熱酸化を行なう。前記熱酸化工程後に前記ビアホール形成部に導電部を有する素子回路を形成した後、前記素子回路形成工程後に前記ビアホールに導電体を埋め込み形成するようにしている。

(もっと読む)

半導体装置

【課題】隣接する画素の間に設ける絶縁膜は、バンク、隔壁、障壁、土手などとも呼ばれ

、薄膜トランジスタのソース配線や、薄膜トランジスタのドレイン配線や、電源供給線の

上方に設けられる。特に、異なる層に設けられたこれらの配線の交差部は、他の箇所に比

べて大きな段差が形成される。隣接する画素の間に設ける絶縁膜を塗布法で形成した場合

においても、この段差の影響を受けて、部分的に薄くなる箇所が形成され、その箇所の耐

圧が低下されるという問題がある。

【解決手段】段差が大きい凸部近傍、特に配線交差部周辺にダミー部材を配置し、その上

に形成される絶縁膜の凹凸形状を緩和する。また、上方配線の端部と下方配線の端部とが

一致しないように、上方配線と下方配線の位置をずらして配置する。

(もっと読む)

半導体装置、電子デバイス及び電子デバイスの製造方法

【課題】対向するバンプ、パッド等を良好に接続し、接続部分の水平強度を高めるための半導体装置を提供する。

【解決手段】半導体基板2の上方に形成される第1絶縁膜15と、第1絶縁膜15内に形成される導電パターン19と、第1絶縁膜15上に形成される第2絶縁膜21と、第2絶縁膜21内に形成され、導電パターン19に接続されるビアプラグ24と、記ビアプラグ24の上に接続され、開口部25aを有する電極パッド25と、第2絶縁膜21内でビアプラグ24の周辺に形成される内部空間21aとを有し、電極パッド25上面及び開口部25a内には外部の突起状電極58が接続される。

(もっと読む)

半導体装置およびその製造方法

【課題】SOGで平坦化した半導体装置であっても水分による閾値変動を抑制した半導体装置を提供する。

【解決手段】SOG平坦化後にSOGを除去したMOSトランジスタ領域を単層配線とし、SOGを残した非MOSトランジスタ領域を多層配線とすることで、SOGを介したMOSトランジスタへの水分の影響が無くなり、MOSトランジスタの閾値変動を抑制できる。

(もっと読む)

ホール形成方法、並びに該方法を用いてビアホールを形成した多層配線、半導体装置、表示素子、画像表示装置、及びシステム

【課題】プロセス再現性が高く、微細なホールを効率よく低コストで形成することができるホール形成方法、並びに、該ホール形成方法を用いてビアホールを形成した多層配線、半導体装置、表示素子、画像表示装置、及びシステムの提供。

【解決手段】基材上にピラー形成液を付与してピラーを形成するピラー形成工程と、前記ピラーが形成された基材上に絶縁膜形成材料を付与して絶縁膜を形成する絶縁膜形成工程と、前記ピラーを除去して前記絶縁膜に開口部を形成するピラー除去工程と、前記開口部が形成された絶縁膜を熱処理する熱処理工程とを含むホール形成方法である。

(もっと読む)

半導体装置の製造方法

【課題】膜厚の薄い抵抗体もつ抵抗素子を形成する際に、抵抗体の断線に対して強い抵抗素子を提供する。

【解決手段】バリアメタル膜とアルミ電極膜からなる積層電極の先端領域を単層のバリアメタル電極とし、並列するバリアメタル電極間に電気的に接続する抵抗体をリフトオフ法にて形成する。

(もっと読む)

半導体装置の製造方法及び記憶媒体

【課題】被エッチング膜の上に積層された、有機膜と、その有機膜の上に積層されたレジストパターンが開口したレジスト膜とを備える、被エッチング膜のエッチングマスクとなる複数層レジストの前記有機膜に、高い垂直性を有するマスクパターンを形成すること。

【解決手段】前記複数層レジストの前記有機膜を、二酸化炭素と水素とを含む処理ガスをプラズマ化して得たプラズマにより前記レジストパターンに沿ってエッチングして、前記被エッチング膜をエッチングするためのマスクパターンを形成する。実験により複数層レジストを構成する有機膜に垂直性が高いマスクパターンを得ることができることが示されている。

(もっと読む)

半導体装置

【課題】配線及びビア間接続の信頼性を向上させた半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上の異なる高さに配置され、配線が形成された複数の配線層と、前記配線層の積層方向に延びる柱状に形成され、異なる複数の前記配線層の配線間を電気的に接続するビアとを備える。前記配線の一部は、前記ビアの中間部において前記ビアに接触する中間配線であり、所定の前記配線層の中間配線は、前記ビアを前記積層方向に直交する方向で貫通し、且つ、上面、下面及び両側面において前記ビアと接触していることを特徴とする。

(もっと読む)

半導体装置の製造方法及び半導体ウエハ

【課題】 導電体部を有し、複数の絶縁膜を除去して形成される半導体装置において、金属汚染を抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】 導電パターンを有する配線層と、導電パターンの側面を囲む第1の絶縁膜を含む複数の絶縁膜と、を有する半導体装置の製造方法において、半導体ウエハ上に複数の絶縁膜を形成する工程と、配線層を形成する工程と、を有する。そして、半導体ウエハ上に複数の絶縁膜を形成する工程及び配線層を形成する工程の後に、複数の絶縁膜の一部の領域を除去し、開口を形成する工程と、を有する。ここで、第1の絶縁膜は、導電パターンの配置位置のうちウエハの最外周に最も近い位置よりも半導体ウエハの外周に近い位置まで配置されている。

(もっと読む)

半導体装置の製造方法、絶縁膜および半導体装置

【課題】Siを含まない化学構造を有する有機化合物である重合性化合物の重合体を含む材料で構成された絶縁膜を備え、誘電率の増大の問題が防止された信頼性の高い半導体装置を効率よく製造することができる製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、素子が形成された半導体基板を被覆するように、Siを含まない化学構造を有する有機化合物である重合性化合物の重合体を含む材料で構成された絶縁膜を形成する絶縁膜形成工程と、窒素系ガスを用いて前記絶縁膜をプラズマエッチングする窒素系エッチング工程と、前記窒素系エッチング工程が施された前記絶縁膜の酸素含有率を低減させる酸素含有率低減工程とを有することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】所望の微細化パターンを高精度かつ効率良く形成することができ、生産効率を向上させることのできる半導体装置の製造方法を提供する。

【解決手段】トリミングされたフォトレジスト層104のラインパターンの上に第1の膜105を成膜する工程と、前記ラインパターンの側壁部以外にある第1の膜105およびフォトレジスト層104を除去する工程と、該除去後に残った部分の第1の膜105をマスクとして反射防止膜103とコア層102をエッチングし、コア層102をラインパターンとする工程と、ラインパターン化コア層102の上に第2の膜106を成膜する工程と、ラインパターン化コア層102の側壁部以外にある第2の膜106およびラインパターン化コア層102を除去する工程と、該除去後に残った部分の第2の膜106をマスクとして被エッチング層101をエッチングし、ラインパターンとする工程とを備えた製造方法とする。

(もっと読む)

半導体装置の製造方法、半導体装置、および電子機器

【課題】配線層の露出面において、ダイシングの工程等で水が接触することにより生じ、配線層の露出面における接合強度の低下や外観不良等の原因となる腐食の発生を抑制する。

【解決手段】半導体基板の一方の面側にて、標準電極電位が互いに異なる2種以上の金属を含む合金により形成された配線層を露出させる工程(パッドを開口する工程(S10))と、前記配線層の露出面を含む範囲に、N2/Arプラズマを照射するプラズマ処理を行う工程(N2/Arプラズマ処理を行う工程(S30))と、を含む方法を用いる。

(もっと読む)

銅の光子誘起除去

【課題】基板から銅含有層の少なくとも一部を除去する方法を提供する。

【解決手段】第1反応チャンバ中で、銅含有表面層4の少なくとも一部を、ハロゲン化銅表面層5に変える工程と、第2反応チャンバ中で、光子含有雰囲気6に晒して、ハロゲン化銅表面層5の少なくとも一部を除去して、揮発性のハロゲン化銅生成物8の形成を始める工程とを含む。光子含有雰囲気6に晒す間に、この方法は、更に、第2反応チャンバから揮発性のハロゲン化銅生成物8を除去し、第2反応チャンバ中で揮発性のハロゲン化銅生成物8の飽和を避ける工程を含む。本発明の具体例にかかる方法は、銅含有層のパターニングに用いられる。例えば、本発明の具体例にかかる方法は、半導体デバイス中に銅含有相互接続構造を形成するのに使用される。

(もっと読む)

導電性素子およびその製造方法、配線素子、情報入力装置、表示装置、ならびに電子機器

【課題】精細かつ高スループットの導電性素子を提供する。

【解決手段】導電性素子は、第1の波面と第2の波面とを有する基体と、第1の波面上に形成された、2層以上の層が積層された積層膜とを備える。積層膜が、導電パターン部を形成する。第1の波面および第2の波面が、0≦(Am1/λm1)<(Am2/λm2)≦1.8(但し、Am1:第1の波面の振動の平均幅、Am2:第2の波面の振動の平均幅、λm1:第1の波面の平均波長、λm2:第2の波面の平均波長)の関係を満たす。

(もっと読む)

半導体装置の製造方法、及び固体撮像装置の製造方法

【課題】 精度よく開口を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】 第1の絶縁膜となる部材と、第1の絶縁膜となる部材と異なる材料からなる第2の絶縁膜となる部材と、第3の絶縁膜となる部材と、第3の絶縁膜となる部材と異なる材料の第4の絶縁膜となる部材とがこの順に積層された半導体基板の上に、複数の絶縁膜の開口を形成するための開口を有するマスクを形成する工程と、第3の絶縁膜となる部材のマスクの開口に対応する部分と第4の絶縁膜となる部材のマスクの開口に対応する部分を連続して除去する第1の工程と、第1の工程を行った後に、第2の絶縁膜となる部材のマスクの開口と対応する部分を除去する第2の工程と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の金属配線を高信頼性化する。

【解決手段】一つの実施形態によれば、半導体装置は、第1の配線材、開口部、及び電極端子部が設けられる。第1の配線材は、半導体基板上の第1の層間絶縁膜上に設けられ、配線層として用いられる。開口部は、第1の配線材上に設けられた第2の層間絶縁膜をエッチングして形成される。電極端子部は、開口部及び開口部周囲の第2の層間絶縁膜上に設けられ、第1の配線材に接するバリアメタル膜、シードメタル膜、及び第2の配線材が開口部を覆うように積層形成され、第2の配線材の上部及び側面に被覆メタル膜が形成される。

(もっと読む)

半導体装置の製造方法

【課題】配線中に残留した不純物金属の濃度が少ない半導体装置の製造方法を提供する。

【解決手段】半導体基板上に絶縁膜を形成し、絶縁膜に凹部を形成し、凹部の形成された絶縁膜の表面に所定の金属元素を含む前駆体膜を形成し、前駆体膜上に配線形成膜を堆積させ、酸化雰囲気下で熱処理を施すことにより、前駆体膜と絶縁膜を反応させ、その境界面に所定の金属元素と絶縁膜の構成元素を含む化合物を主成分とする自己形成バリア膜を形成し、未反応の所定の金属元素を配線形成膜内に拡散移動させて配線形成膜表面で雰囲気中の酸素と反応させ、未反応金属酸化膜として析出させ、未反応金属酸化膜を除去し、未反応金属酸化膜を除去する工程の後、配線形成膜上に、配線形成膜と同一の材料を堆積させて、配線形成膜を積み増した後、凹部外の絶縁膜が露出するまで配線形成膜を平坦化して配線構造を形成する。

(もっと読む)

半導体装置の製造方法

【課題】タングステン膜を使用した部分の抵抗を低減した半導体装置を提供する。

【解決手段】半導体装置の製造方法では、基板内に設けた開口部内、又は基板上にタングステン膜を形成する。タングステン膜の形成後、エッチバック又はエッチングを行う前にタングステン膜に対してアニール処理を行う。これにより、タングステン膜の結晶状態を変化させる。

(もっと読む)

41 - 60 / 898

[ Back to top ]