Fターム[5F033QQ12]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | ドライエッチング (6,179) | プラズマエッチング (898)

Fターム[5F033QQ12]に分類される特許

81 - 100 / 898

半導体装置の製造方法

【課題】微細で良好な形状のコンタクトホールを有する半導体装置の製造方法を提供する。

【解決手段】絶縁膜36上にフォトレジスト膜42を形成する工程と、フォトレジスト膜42に開口部44を形成する工程と、開口部44が形成されたフォトレジスト膜42をマスクとして絶縁膜36をエッチングすることによりコンタクトホール48を形成する工程とを有し、コンタクトホール48を形成する工程は、開口部44が形成されたフォトレジスト膜42上に保護膜46を堆積しながら絶縁膜36をプラズマエッチングする第1の工程と、フォトレジスト膜42上に堆積された保護膜46を一旦除去する第2の工程と、保護膜46が一旦除去されたフォトレジスト膜42上に他の保護膜を新たに堆積しながら絶縁膜36を更にプラズマエッチングする第3の工程とを含んでいる。

(もっと読む)

回路基板の製造方法

【課題】印刷法にて、回路基板に容易にヴィアホールを開口できる回路基板の製造方法を提供する事。

【解決手段】基板上に第一導電体を形成する第一導電体形成工程を行い、次に第一導電体を被覆する様に第一絶縁膜を成膜する第一絶縁膜成膜工程を行い、次に第一導電体上の第一絶縁膜に貫通孔32を開口して、第一導電体の表面を露出させる貫通孔形成工程を行い、次に第一導電体の表面を撥液化させる撥液化工程を行い、次に貫通孔32以外の領域に前駆体樹脂を印刷し、印刷後に前駆体樹脂を硬化して第二絶縁膜を形成する第二絶縁膜形成工程を行う。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクト孔に埋め込まれる金属プラグの材料が層間絶縁膜に染み出すのを防止できる半導体装置を提供する。

【解決手段】隣り合う2つのメモリセル1のサイドウォール間の不純物拡散領域に電気的接続されるコンタクトプラグ40が、層間絶縁膜18を貫通して設けられている。コンタクト孔41の側壁は、層間絶縁膜18より緻密なシール膜42で覆われている。コンタクトプラグ40は、シール膜42の表面およびコンタクト孔41の底面部を覆うように形成されたバリアメタル膜43と、バリアメタル膜43に包囲された状態でコンタクト孔41内に埋め込まれた金属プラグ44とを含む。

(もっと読む)

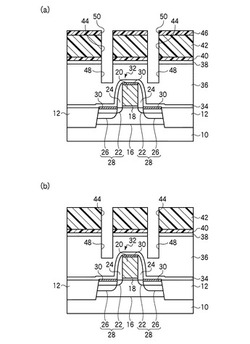

半導体装置およびその製造方法

【課題】サイドウォール間に層間絶縁膜を埋め込むときに埋め込み不良の発生を防止できる半導体装置の製造方法を提供する。

【解決手段】シリコン基板2の表面上に、ゲート酸化膜6、ポリシリコン層(第1ゲート層)9、タングステンシリサイド層(第2ゲート層)10および絶縁層8が形成される。絶縁層8が所定のゲートパターンにエッチングされる。タングステンシリサイド層10が前記所定のゲートパターンにエッチングされる。タングステンシリサイド層10の側壁が後退される。この後、ポリシリコン層9が前記所定のゲートパターンにエッチングされる。ゲート酸化膜6が前記所定のゲートパターンにエッチングされる。

(もっと読む)

微細パターンの形成方法

【課題】側壁部の形成の基礎となるパターンをレジストにより形成する場合であっても、側壁部の傾きを抑制できる微細パターンの形成方法を提供する。

【解決手段】基板上に形成されたエッチング対象層の上に有機膜を形成する有機膜形成ステップと、有機膜上にレジスト膜を形成し、このレジスト膜をパターニングするパターニングステップと、パターニングされたレジスト膜から露出する有機膜と、パターニングされたレジスト膜とを覆うように酸化シリコン膜を常温にて堆積する堆積ステップと、基板を加熱して酸化シリコン膜に引っ張り応力を生じさせる加熱ステップと、処理ステップの後に、パターニングされたレジスト膜の側壁に酸化シリコン膜が残るように当該酸化シリコン膜をエッチングする第1のエッチングステップと、パターニングされたレジスト膜を除去する除去ステップとを含む、微細パターンの形成方法が開示される。

(もっと読む)

半導体装置の製造方法

【課題】基板に形成される第1の膜と第2の膜との重なり量を精度良く算出する。

【解決手段】半導体装置の製造方法は、基板の第1の領域及び第2の領域に第1の膜を形成する工程と、第2の領域の第1の膜の幅を測定する工程と、基板の第2の領域及び第3の領域に第2の膜を形成する工程と、第2の領域の第2の膜の幅及び第2の領域の第1の膜と第2の膜との距離を測定する工程と、第2の領域における第1の膜の幅の測定値、第2の膜の幅の測定値、第1の膜と第2の膜との距離の測定値及び第1の膜と第2の膜とに関する設計値に基づいて、第1の領域における第1の膜と第3の領域における第2の膜との重なり量を算出する工程と、を備える。

(もっと読む)

エッチング方法、エッチングシステムおよびエッチング装置

【課題】シリコン酸化膜にコンタクト部に到達する高アスペクト比のホールを形成する際に、ホール内のコンタクト材料とコンタクト部との間で十分なコンタクトがとれるようなホールを形成すること。

【解決手段】基板上にBおよびPの少なくとも一方を含むシリコン酸化物からなる第1の酸化膜と、その上に形成された、BおよびPを含まないシリコン酸化物からなる第2の酸化膜とを有し、さらに第1の酸化膜および第2の酸化膜の界面より下方に形成されたコンタクト部を有する被処理体を準備し(ステップ1)、第2の酸化膜と前記第1の酸化膜をエッチングしてコンタクト部に到達するホールを形成し(ステップ2)、HFガスおよび不活性ガスを用いたドライプロセスにより第1の酸化膜をエッチングし、第1の酸化膜のコンタクト部上方領域のホール部分を広げる(ステップ3)。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】 基板を薄くしてもその反りを防止するTSV構造の製造方法を提供する

【解決手段】本発明の半導体装置の製造方法は、半導体基板の表面に半導体素子を集積させて回路の少なくとも一部を形成する工程と、半導体基板の表面から穴を開ける工程と、穴の内表面に絶縁膜およびバリア膜を形成する工程と、バリア膜の表面に、穴を埋めるように導電性金属を形成する工程と、半導体基板の裏面を加工して厚さを減少させ、導電性金属を突出させる工程と、半導体基板の裏面にSiCN膜を設ける工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の配線間容量を低減する。

【解決手段】半導体装置の製造方法は、基板の上方に絶縁膜を形成する工程と、絶縁膜を貫通する第1の溝及び絶縁膜の内部で終端する第2の溝を絶縁膜に形成する工程と、絶縁膜の内部で終端する配線溝を絶縁膜に形成する工程と、第1の溝の表面及び配線溝の表面に第1の金属膜を形成するともに、第2の溝の上方を覆うように第1の金属膜を形成する工程と、第1の溝及び配線溝に第2の金属膜を埋め込む工程と、を備える。

(もっと読む)

半導体装置及び製造方法

【課題】 基板及び表面層にビアホールが形成された半導体装置において、表面層の剥離及び破壊を抑制すること。

【解決手段】 本半導体装置は、基板10と、基板10上に設けられた基板10と異なる材料からなる表面層20と、表面層20上に設けられた電極パッド50と、を備え、基板10及び表面層20にはビアホール30が形成され、ビアホール30内には、電極パッド50と電気的に接続された金属層32が設けられ、ビアホール30の開口部の周囲には、ビアホール30を囲むように表面層20に溝22が形成されている。

(もっと読む)

マスクおよびその製造方法、半導体ウエハ

【課題】半導体ウエハ面内における金属配線の抵抗分布のばらつきを抑え、得られるデバイスの特性や精度を面内で均一化させることが可能なマスクを提供する。

【解決手段】本発明のマスクは、金属配線を有するデバイス10を基板2の一面上に多数形成する際に、該基板の一面に対向配置されて用いられるマスクであって、個々の前記デバイスが配される前記基板上の位置に応じて、それぞれのデバイスが有する前記金属配線に対応する部位の形状を変えたこと、を特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】金属マスクを形成する工程を含む半導体装置の製造方法において、金属片が支持基板に付着することを防止する。

【解決手段】この製造方法は、支持基板10の表面10aに貼付された半導体ウェハ12上にネガレジストを塗布し、該ネガレジストを露光することにより所定のパターンを有するレジスト18を形成するレジスト形成工程と、半導体ウェハ12上にメッキ処理を施すことにより金属マスク20を形成したのちレジスト18を除去する金属マスク形成工程と、金属マスク20を介して半導体ウェハ12にエッチングを施すことにより、貫通孔12dを形成するエッチング工程と、金属マスク20を除去したのち、貫通孔12dの内面及び半導体ウェハ12の裏面12bに金属膜26を形成する金属膜形成工程と、半導体ウェハ12を支持基板10から取り外す取外し工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】基板に形成されたビアホール内のメタライズを改善すること。

【解決手段】本半導体装置の製造方法は、SiCを材料10とする基板を備える半導体装置の製造方法であって、フッ化炭素を含むエッチングガス及びマスク14を用いて基板10の裏面をエッチングし、基板10の表面から裏面に貫通するビアホール20を形成する工程を有し、ビアホール20成する工程は、基板10の裏面から表面に向かって開口断面積が次第に小さくなるテーパ形状を形成する工程であり、かつエッチング条件は、誘導結合プラズマ方式のドライエッチングを含み、ガス流量が、フッ化炭素=10〜200sccm、ガス圧力が、Press=0.1〜10.0Pa、誘導結合プラズマパワーが、ICP=100〜5000W、バイアスパワーが、Bias=10〜1000W、であることを特徴とする。

(もっと読む)

配線構造及び配線構造の形成方法

【課題】配線の洗浄液への溶解を低減する配線構造の形成方法を提供する。

【解決手段】絶縁層13に犠牲配線溝21及び主配線溝31を形成し、犠牲配線溝21及び主配線溝31内にバリア層16を形成し、バリア層16が形成された犠牲配線溝21及び主配線溝31内に導電層17を埋め込んだ後に、絶縁層13上の導電層17の部分を研磨する工程と、犠牲配線溝21及び主配線溝31内の露出したバリア層16及び導電層17の表面を洗浄する工程と、を備え、研磨する工程の後における絶縁層13の平面視において、犠牲配線溝21内のバリア層16の部分の面積と導電層17の部分の面積との比S1が、主配線溝31内のバリア層16の部分の面積と導電層17の部分の面積との比S2よりも大きくなる。

(もっと読む)

プラズマ処理方法及び半導体装置の製造方法

【課題】サイドエッチングによるパターン細りを抑制しつつ、ドライ処理によってパターン側壁に堆積した金属を含む堆積物を効率良く除去することのできるプラズマ処理方法及び半導体装置の製造方法を提供する。

【解決手段】基板に形成された金属層をプラズマエッチングする工程を経て積層構造中に金属層を有するパターンを形成した後、金属層を構成する金属を含みパターンの側壁部に堆積した堆積物を除去するプラズマ処理方法であって、金属層の側壁部に当該金属の酸化物又は塩化物を形成する保護層形成工程と、フッ素原子を含むガスのプラズマを作用させて堆積物を除去する堆積物除去工程と、保護層形成工程及び堆積物除去工程の後、水素を含むプラズマを作用させて金属の酸化物又は塩化物を還元する還元工程とを具備している。

(もっと読む)

SiCの除去法

【課題】基板に形成されたカーバイドシリコン層の少なくとも露出された部分を除去するための方法を提供する。

【解決手段】カーバイドシリコン層45を酸素含有プラズマに曝すことにより、前記カーバイドシリコン層45の少なくとも露出された部分を酸化シリコン層に変換し、そして基板から前記酸化シリコン層を除去するステップからなる。

(もっと読む)

残存フォトレジスト及び残留側壁パッシベーションを除去する、その場でのポストエッチング工程

【課題】金属エッチングと、残存フォトレジスト及び残留側壁パッシベーションの剥離のための改良された技術を提供する。

【解決手段】単一のエッチングチャンバ内で、金属エッチングと、エッチングマスク剥離と、残留側壁パッシベーションの除去とを実行する方法。ウエハは、エッチングチャンバ内に配置される。ウエハ上で、金属エッチングが実行される。酸素とアルゴンとの混合物等の剥離ガスが、エッチングチャンバに提供され、酸素プラズマを形成するために励起される。酸素プラズマは、エッチングマスクをウエハから剥離させ、残留側壁パッシベーションを除去する。酸素プラズマは、更に、エッチングチャンバをクリーニングする。

(もっと読む)

半導体装置の作製方法

【課題】電気的特性が向上した、酸化物半導体を用いた半導体装置の作製方法を提供することを目的の一とする。

【解決手段】酸化物半導体膜と、酸化物半導体膜と重畳するゲート電極と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極と、を有する半導体装置の作製方法であって、酸化物半導体膜上に接して、酸化ガリウムを含む第1の絶縁膜を形成し、第1の絶縁膜上に接して第2の絶縁膜を形成し、第2の絶縁膜上にレジストマスクを形成し、第1の絶縁膜および第2の絶縁膜にドライエッチングを行ってコンタクトホールを形成し、レジストマスクを、酸素プラズマによるアッシングを用いて除去し、コンタクトホールを介して、ゲート電極、ソース電極またはドレイン電極のいずれか一または複数と電気的に接続される配線を形成する、半導体装置の作製方法である。

(もっと読む)

配線基板の製造方法

【課題】コンタクトホールを、生産性良く、低コストで、且つ信頼性良く製造する配線基板の製造方法を提供する。

【解決手段】基板1に第1電極3及び第2電極7が形成される。第1電極3及び第2電極7を連通するように形成された微細穴の側壁部及び底部に、導電膜9を形成してコンタクトホール2を形成する。この配線基板100の製造する際に、微細穴を形成する微細穴形成工程において、微細穴の側壁部の開口端側に相対的に浅い溝からなる第1溝領域4が形成され、微細穴の側壁部の底部側に相対的に深い溝からなる第2溝領域5が形成される。このように区分けした溝領域4,5のうち、第2溝領域5に導電性材料を含有する液体を付与して、導電膜9を形成する。

(もっと読む)

半導体装置の作製方法

【課題】下地に対する選択比が大きく、テーパー形状の配線を形成するドライエッチング

方法を提供する。

【解決手段】基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下の配線を形成

する。また、基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下のゲート配線

を形成し、前記ゲート配線上にゲート絶縁膜を形成し、前記ゲート絶縁膜上に活性層を形

成する。

(もっと読む)

81 - 100 / 898

[ Back to top ]